|

|

PDF uPD46365362B Data sheet ( Hoja de datos )

| Número de pieza | uPD46365362B | |

| Descripción | 36M-BIT QDR II SRAM 2-WORD BURST OPERATION | |

| Fabricantes | Renesas | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de uPD46365362B (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

μPD46365092B

μPD46365182B

μPD46365362B

Datasheet

36M-BIT QDRTM II SRAM

2-WORD BURST OPERATION

R10DS0089EJ0400

Rev.4.00

Nov 09, 2012

Description

The μPD46365092B is a 4,194,304-word by 9-bit, the μPD46365182B is a 2,097,152-word by 18-bit and the

μPD46365362B is a 1,048,576-word by 36-bit synchronous quad data rate static RAM fabricated with advanced CMOS

technology using full CMOS six-transistor memory cell.

The μPD46365092B, μPD46365182B and μPD46365362B integrate unique synchronous peripheral circuitry and a

burst counter. All input registers controlled by an input clock pair (K and K#) are latched on the positive edge of K and

K#.

These products are suitable for application which require synchronous operation, high speed, low voltage, high density

and wide bit configuration. These products are packaged in 165-pin PLASTIC BGA.

Features

• 1.8 ± 0.1 V power supply

• 165-pin PLASTIC BGA (13 x 15)

• HSTL interface

• PLL circuitry for wide output data valid window and future frequency scaling

• Separate independent read and write data ports with concurrent transactions

• 100% bus utilization DDR READ and WRITE operation

• Two-tick burst for low DDR transaction size

• Two input clocks (K and K#) for precise DDR timing at clock rising edges only

• Two output clocks (C and C#) for precise flight time and clock skew matching-clock

and data delivered together to receiving device

• Internally self-timed write control

• Clock-stop capability. Normal operation is restored in 20 μs after clock is resumed.

• User programmable impedance output (35 to 70 Ω)

• Fast clock cycle time : 3.3 ns (300 MHz), 4.0 ns (250 MHz).

• Simple control logic for easy depth expansion

• JTAG 1149.1 compatible test access port

R10DS0089EJ0400 Rev.4.00

Nov 09, 2012

Page 1 of 35

1 page

μPD46365092B, μPD46365182B, μPD46365362B

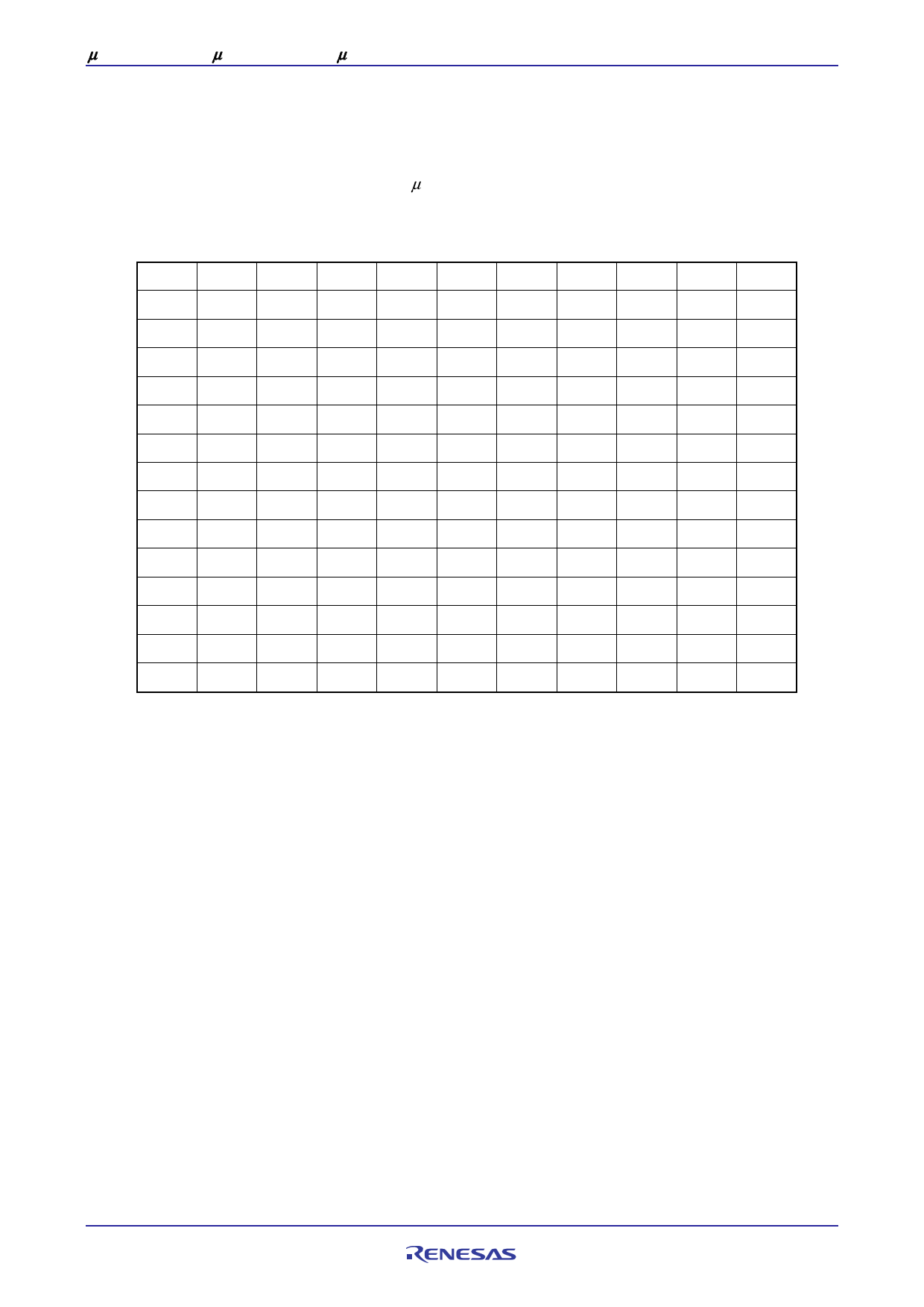

Pin Arrangement

165-pin PLASTIC BGA (13 x 15)

(Top View)

[μPD46365362B]

1M x 36

12345678

A CQ# VSS/288M NC/72M W# BW2# K# BW1# R#

B Q27 Q18 D18

A BW3# K BW0# A

C D27 Q28 D19 VSS

A

A

A VSS

D D28 D20 Q19 VSS VSS VSS VSS VSS

E Q29

D29

Q20 VDDQ

VSS

VSS

VSS VDDQ

F Q30

Q21

D21 VDDQ

VDD

VSS

VDD

VDDQ

G D30

D22

Q22 VDDQ

VDD

VSS

VDD

VDDQ

H DLL#

VREF

VDDQ

VDDQ

VDD

VSS

VDD

VDDQ

J D31

Q31

D23 VDDQ

VDD

VSS

VDD

VDDQ

K Q32

D32

Q23 VDDQ

VDD

VSS

VDD

VDDQ

L Q33

Q24

D24 VDDQ

VSS

VSS

VSS VDDQ

M D33 Q34 D25 VSS VSS VSS VSS VSS

N D34 D26 Q25 VSS

A

A

A VSS

P Q35 D35 Q26

A

A

C

A

A

R TDO TCK

A

A

A C# A

A

9 10

A

D17

VSS/144M

Q17

D16 Q7

Q16 D15

Q15 D6

D14 Q14

Q13 D13

VDDQ

D12

VREF

Q4

Q12 D3

D11 Q11

D10 Q1

Q10 D9

Q9 D0

A TMS

11

CQ

Q8

D8

D7

Q6

Q5

D5

ZQ

D4

Q3

Q2

D2

D1

Q0

TDI

A

D0 to D35

Q0 to Q35

R#

W#

BW0# to BW3#

K, K#

C, C#

CQ, CQ#

ZQ

DLL#

: Address inputs

: Data inputs

: Data outputs

: Read input

: Write input

: Byte Write data select

: Input clock

: Output clock

: Echo clock

: Output impedance matching

: PLL disable

TMS

TDI

TCK

TDO

VREF

VDD

VDDQ

VSS

NC

NC/xxM

: IEEE 1149.1 Test input

: IEEE 1149.1 Test input

: IEEE 1149.1 Clock input

: IEEE 1149.1 Test output

: HSTL input reference input

: Power Supply

: Power Supply

: Ground

: No connection

: Expansion address for xxMb

Remarks 1. ×××# indicates active LOW.

2. Refer to Package Dimensions for the index mark.

3. 2A, 3A and 10A are expansion addresses : 3A for 72Mb

: 3A and 10A for 144Mb

: 3A, 10A and 2A for 288Mb

2A and 10A of this product can also be used as NC.

R10DS0089EJ0400 Rev.4.00

Nov 09, 2012

Page 5 of 35

5 Page

μPD46365092B, μPD46365182B, μPD46365362B

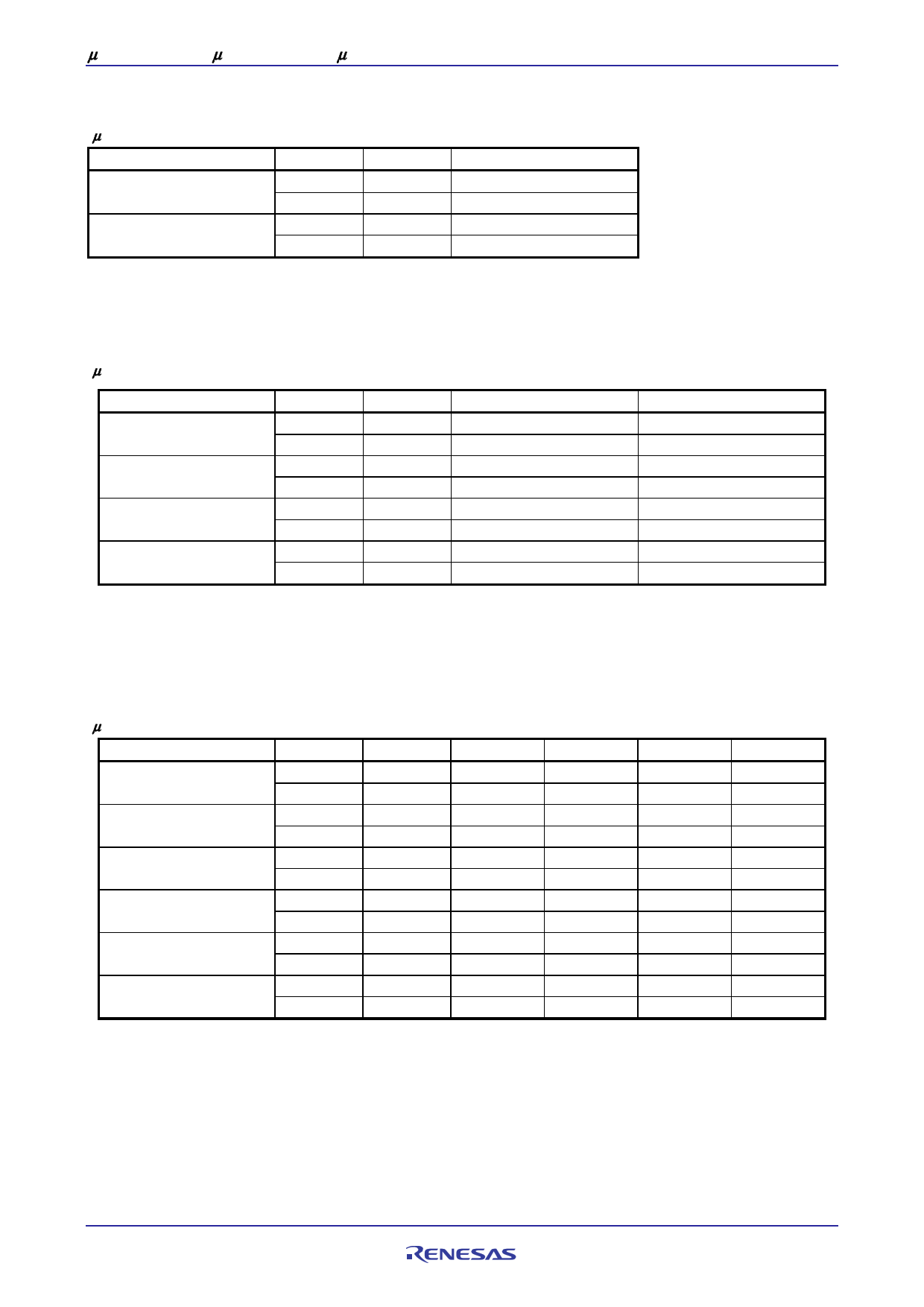

Byte Write Operation

[μPD46365092B]

Operation

K K#

Write D0 to D8

L→H

−

− L→H

Write nothing

L→H

−

− L→H

Remarks 1. H : HIGH, L : LOW, → : rising edge.

BW0#

0

0

1

1

2. Assumes a WRITE cycle was initiated. BW0# can be altered for any portion of the BURST WRITE

operation provided that the setup and hold requirements are satisfied.

[μPD46365182B]

Operation

Write D0 to D17

Write D0 to D8

Write D9 to D17

Write nothing

K

L→H

−

L→H

−

L→H

−

L→H

−

K#

−

L→H

−

L→H

−

L→H

−

L→H

BW0#

0

0

0

0

1

1

1

1

BW1#

0

0

1

1

0

0

1

1

Remarks 1. H : HIGH, L : LOW, → : rising edge.

2. Assumes a WRITE cycle was initiated. BW0# and BW1# can be altered for any portion of the BURST

WRITE operation provided that the setup and hold requirements are satisfied.

[μPD46365362B]

Operation

K

K#

BW0#

BW1#

BW2#

BW3#

Write D0 to D35

L→H

−

0

0

0

0

− L→H

0

0

0

0

Write D0 to D8

L→H

−

0

1

1

1

− L→H

0

1

1

1

Write D9 to D17

L→H

−

1

0

1

1

− L→H

1

0

1

1

Write D18 to D26

L→H

−

1

1

0

1

− L→H

1

1

0

1

Write D27 to D35

L→H

−

1

1

1

0

− L→H

1

1

1

0

Write nothing

L→H

−

1

1

1

1

− L→H

1

1

1

1

Remarks 1. H : HIGH, L : LOW, → : rising edge.

2. Assumes a WRITE cycle was initiated. BW0# to BW3# can be altered for any portion of the BURST

WRITE operation provided that the setup and hold requirements are satisfied.

R10DS0089EJ0400 Rev.4.00

Nov 09, 2012

Page 11 of 35

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet uPD46365362B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| uPD46365362B | 36M-BIT QDR II SRAM 2-WORD BURST OPERATION | Renesas |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |