|

|

PDF P4C1981 Data sheet ( Hoja de datos )

| Número de pieza | P4C1981 | |

| Descripción | STATIC CMOS RAM | |

| Fabricantes | PYRAMID | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de P4C1981 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

P4C1981/P4C1981L, P4C1982/P4C1982L

ULTRA HIGH SPEED 16K x 4

CMOS STATIC RAMS

FEATURES

Full CMOS, 6T Cell

High Speed (Equal Access and Cycle Times)

– 10/12/15/20/25 ns (Commercial)

– 12/15/20/25/35 ns (Industrial)

– 15/20/25/35/45 ns (Military)

Low Power Operation (Commercial/Military)

Output Enable and Dual Chip Enable Functions

5V ± 10% Power Supply

Data Retention with 2.0V Supply, 10 µA Typical

Current (P4C1981L/1982L Military)

Separate Inputs and Outputs

– P4C1981/L Input Data at Outputs during Write

– P4C1982/L Outputs in High Z during Write

Fully TTL Compatible Inputs and Outputs

Standard Pinout (JEDEC Approved)

– 28-Pin 300 mil DIP, SOJ

– 28-Pin 350 x 550 mil LCC

– 28-Pin CERPACK

DESCRIPTION

The P4C1981/L and P4C1982/L are 65,536-bit (16Kx4)

ultra high-speed static RAMs similar to the P4C198, but

with separate data I/O pins. The P4C1981/L feature a

transparent write operation when OE is low; the outputs

of the P4C1982/L are in high impedance during the write

cycle. All devices have low power standby modes. The

RAMs operate from a single 5V ± 10% tolerance power

supply. With battery backup, data integrity is maintained

for supply voltages down to 2.0V. Current drain is

typically 10 µA from 2.0V supply.

Access times as fast as 10 nanoseconds are available,

permitting greatly enhanced system operating speeds.

CMOS is used to reduce power consumption. For the

P4C1982L and P4C1981L, power is only 5.5 mW standby

with CMOS input levels.

The P4C1981/L and P4C1982/L are available in 28-pin 300

mil DIP and SOJ, 28-pin 350x550 mil LCC and a 28-pin

CERPACK package providing excellent board level den-

sities.

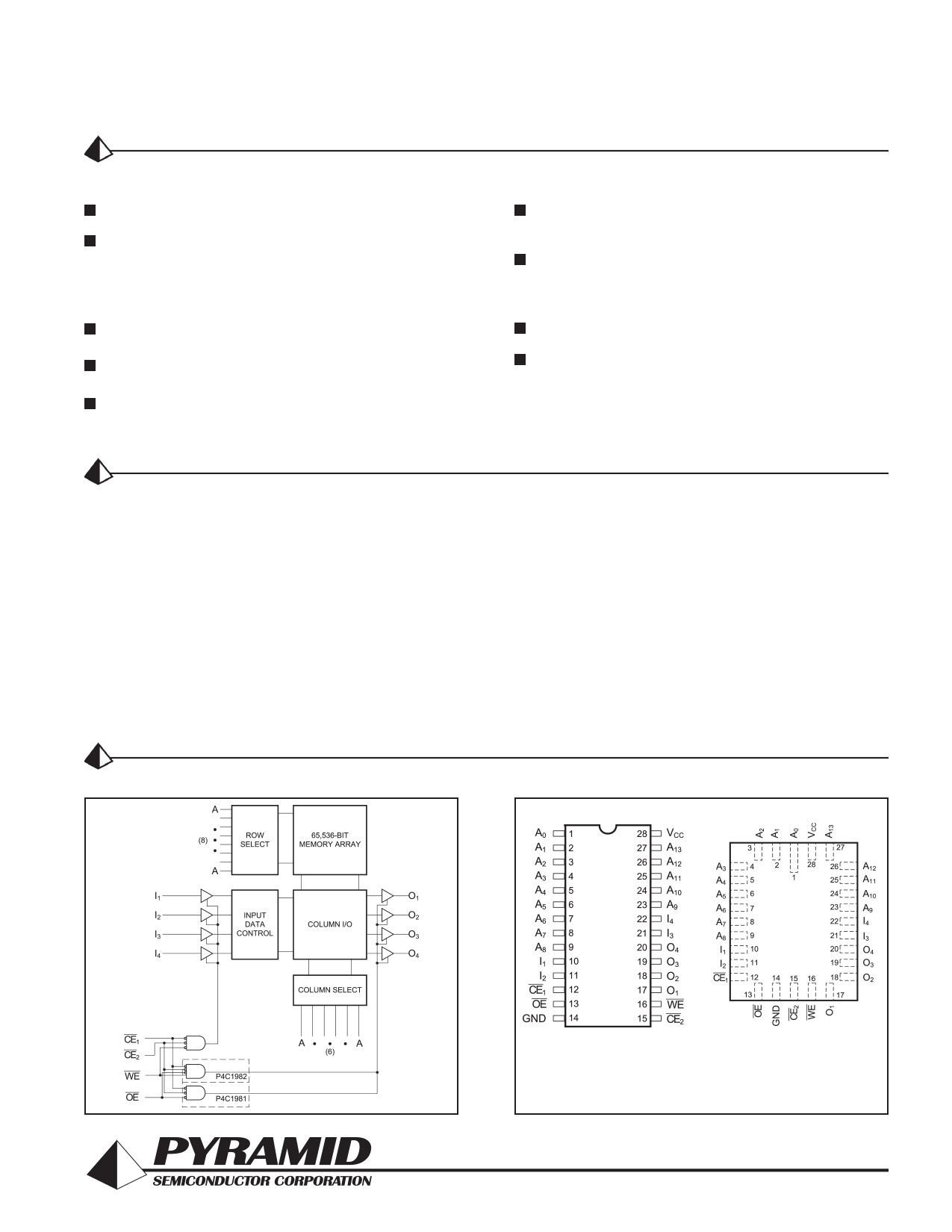

FUNCTIONAL BLOCK DIAGRAM

PIN CONFIGURATIONS

DIP (P5, C5, D5-2), SOJ (J5)

CERPACK (F4) SIMILAR

P4C1981/ 1982

LCC (L5)

Document # SRAM114 REV B

Revised August 2006

1

1 page

READ CYCLE NO. 2 (ADDRESS Controlled)(5,6)

P4C1981/1981L, P4C1982/1982L

READ CYCLE NO. 3 (CE1, CE2 Controlled)(5,7,8)

Note:

11. Transitions caused by a chip enable control have similar delays irrespective of whether CE1 or CE2 causes them.

Document # SRAM114 REV B

Page 5 of 13

5 Page

Pkg #

# Pins

Symbol

A

b

c

D

E

e

k

L

Q

S

S1

F4

28

Min Max

0.060 0.090

0.015 0.022

0.004 0.009

- 0.730

0.330 0.380

0.050 BSC

0.005 0.018

0.250 0.370

0.026 0.045

- 0.085

0.005

-

CERPACK CERAMIC FLAT PACKAGE

P4C1981/1981L, P4C1982/1982L

Pkg #

# Pins

Symbol

A

A1

b

C

D

e

E

E1

E2

Q

J5

28 (300 mil)

Min Max

0.120 0.148

0.078

-

0.014 0.020

0.007 0.011

0.700 0.730

0.050 BSC

0.335 BSC

0.292 0.300

0.267 BSC

0.025

-

SOJ SMALL OUTLINE IC PACKAGE

Document # SRAM114 REV B

Page 11 of 13

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet P4C1981.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| P4C198 | ULTRA HIGH SPEED 16K x 4 | ETC |

| P4C1981 | STATIC CMOS RAM | PYRAMID |

| P4C1981L | STATIC CMOS RAM | PYRAMID |

| P4C1982 | STATIC CMOS RAM | PYRAMID |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |