|

|

PDF LTC6945 Data sheet ( Hoja de datos )

| Número de pieza | LTC6945 | |

| Descripción | Ultralow Noise and Spurious 0.35GHz to 6GHz Integer-N Synthesizer | |

| Fabricantes | Linear | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LTC6945 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

LTC6945

Features

Ultralow Noise and Spurious

0.35GHz to 6GHz Integer-N

Synthesizer

Description

nn Low Noise Integer-N PLL

nn 350MHz to 6GHz VCO Input Range

nn –226dBc/Hz Normalized In-Band Phase Noise Floor

nn –274dBc/Hz Normalized In-Band 1/f Noise

nn –157dBc/Hz Wideband Output Phase Noise Floor

nn Excellent Spurious Performance

nn Output Divider (1 to 6, 50% Duty Cycle)

nn Low Noise Reference Buffer

nn Output Buffer Muting

nn Charge Pump Supply from 3.15V to 5.25V

nn Charge Pump Current from 250µA to 11.2mA

nn Configurable Status Output

nn SPI Compatible Serial Port Control

nn PLLWizard™ Software Design Tool Support

Applications

nn Wireless Base Stations (LTE, WiMAX, W-CDMA, PCS)

nn Broadband Wireless Access

nn Microwave Data Links

nn Military and Secure Radio

nn Test and Measurement

The LTC®6945 is a high performance, low noise, 6GHz phase-

locked loop (PLL), including a reference divider, phase-

frequency detector (PFD) with phase-lock indicator, charge

pump, integer feedback divider and VCO output divider.

The part features a buffered, programmable VCO output

divider with a range of 1 through 6. The differential, low

noise output buffer has user-programmable output power

ranging from –6dBm to 3dBm, and may be muted through

either a digital input pin or software.

The low noise reference buffer outputs a typical 0dBm

square wave directly into a 50Ω impedance from 10MHz

to 250MHz, or may be disabled through software.

The ultralow noise charge pump contains selectable high

and low voltage clamps useful for VCO monitoring, and

also may be set to provide a V+/2 bias.

All device settings are controlled through a SPI-compatible

serial port.

L, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and

PLLWizard is a trademark of Linear Technology Corporation. All other trademarks are the

property of their respective owners.

Typical Application

LTC6945 Data Converter Sample Clock

3.3V LOOP

0.1µF

BANDWIDTH

~2.3kHz

VTUNE

5V CRYSTEK

CVCSO-914-1000

100MHz

REF 1µF

51.1Ω

1µF

5V

0.1µF

432Ω

570nF

47nF

3.3V

0.1µF

SPI BUS

3.3V

0.1µF

REF– REF+

VREFO+

VREF+ CP VCP+VGVNCOD+

REFO

STAT

LTC6945

GND

GND

CS

SCLK

GND

GND

GND

SDI GND

SDO

VD+

MUTE

fPFD = 25MHz

GND RF– RF+ VRF+

VCO+

VCO–

BB

3.3V 0.01µF

16.5Ω

100pF

1.0µF

100pF

16.5Ω

16.5Ω

100pF

68nH

3.3V

100pF

50Ω

3.3V 0.01µF

68nH

3.3V

100pF

ALT SAMPLE CLOCK

500MHz OR 1GHz

SAMPLE CLOCK

1GHz, 7dBm

6945 TA01b

1GHz Sample Clock Phase Noise

–100

–110

–120

–130

–140

–150

–160

–170

–180

100

DSB INTEGRATION

(100Hz TO 1GHz)

RMS NOISE = 0.014°

RMS JITTER = 39fs

fPFD = 25MHz

BW = 2.3kHz

1k 10k 100k 1M

OFFSET FREQUENCY (Hz)

10M 40M

6945 TA01b

For more information www.linear.com/LTC6945

6945fa

1

1 page

LTC6945

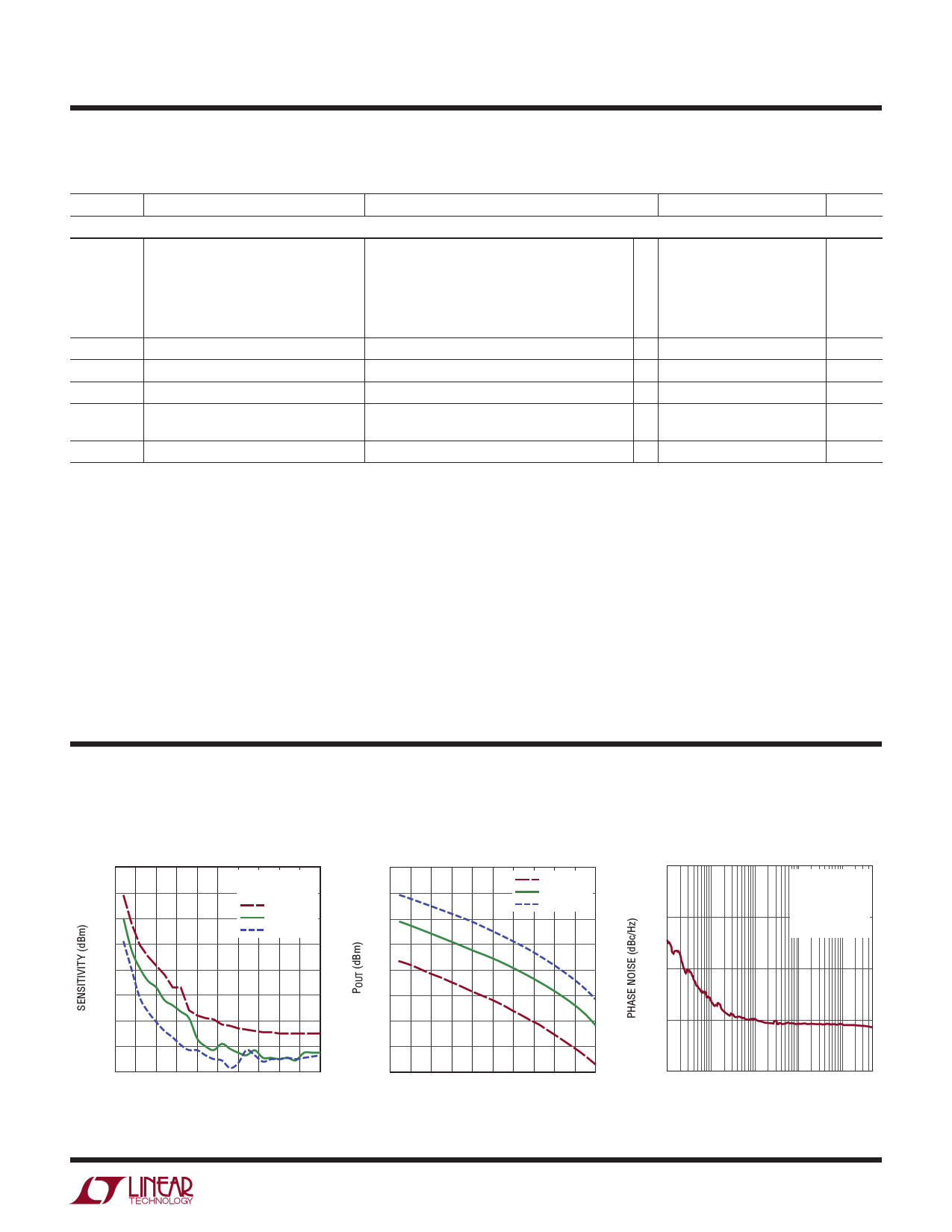

E lectrical Characteristics The l denotes the specifications which apply over the full operating

junction temperature

otherwise specified.

range, otherwise specifications are at

All voltages are with respect to GND.

TA

=

25°C.

VREF+

=

VREF0+

=

VD+

=

VRF+

=

VVCO+

=

3.3V,

VCP+

=

5V

unless

SYMBOL PARAMETER

Phase Noise and Spurious

LM(MIN)

Output Phase Noise Floor (Note 5)

LM(NORM) Normalized In-Band Phase Noise Floor

LM(NORM –1/f) Normalized In-Band 1/f Phase Noise

LM(IB)

In-Band Phase Noise Floor

Integrated Phase Noise from 100Hz to

40MHz

Spurious

CONDITIONS

RFO[1:0]

RFO[1:0]

=

=

3,

3,

OD[2:0]

OD[2:0]

=

=

1,

2,

ffRRFF

=

=

6GHz

3GHz

RFO[1:0] = 3, OD[2:0] = 3, fRF = 2GHz

RFO[1:0] = 3, OD[2:0] = 4, fRF = 1.5GHz

RFO[1:0] = 3, OD[2:0] = 5, fRF = 1.2GHz

RFO[1:0] = 3, OD[2:0] = 6, fRF = 1.0GHz

ICP = 11.2mA (Notes 6, 7, 8)

ICP = 11.2mA (Notes 6, 9)

(Notes 6, 7, 8, 10)

(Notes 4, 7, 10)

Reference Spur, PLL locked (Notes 4, 7, 10, 11)

MIN TYP MAX

–155

–155

–156

–156

–157

–158

–226

–274

–99

0.13

–102

UNITS

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

°RMS

dBc

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2: The LTC6945I is guaranteed to meet specified performance limits

over the full operating junction temperature range of –40°C to 105°C.

Under maximum operating conditions, air flow or heat sinking may

be required to maintain a junction temperature of 105°C or lower. It is

strongly recommended that the exposed pad (Pin 29) be soldered directly

to the ground plane with an array of thermal vias as described in the

Applications Information section.

Note 3: For 0.9V ≤ VCP ≤ (VCP+ – 0.9V).

Note 4: VCO is Crystek CVCO55CL-0902-0928.

Note 5: fVCO = 6GHz, fOFFSET = 40MHz.

Note 6: Measured inside the loop bandwidth with the loop locked.

Note 7: Reference frequency supplied by Wenzel 501-04608A,

fREF = 10MHz, PREF = 13dBm.

Note 8: Output phase noise floor is calculated from normalized phase

noise floor by LM(OUT) = –226 + 10log10(fPFD) + 20log10(fRF/fPFD).

Note 9: Output 1/f phase noise is calculated from normalized 1/f phase

noise by LM(OUT –1/f) = –274 + 20log10 (fRF) – 10log10 (fOFFSET).

Note 10: ICP = 11.2mA, fPFD = 250kHz, fRF = 914MHz, FILT[1:0] = 3, Loop

BW = 7kHz.

Note 11: Measured using DC1649.

Typical Performance Characteristics

REF Input Sensitivity vs

Frequency

–15

BST = 1

–20 FILT = 0

TJ = 105°C

–25 TJ = 25°C

TJ = –40°C

–30

–35

–40

–45

–50

–55

0 25 50 75 100 125 150 175 200 225 250

FREQUENCY (MHz)

6945 G01

REFO Output Power vs Frequency

4

TJ = 105°C

3 TJ = 25°C

TJ = –40°C

2

1

0

–1

–2

–3

–4

0 25 50 75 100 125 150 175 200 225 250

FREQUENCY (MHz)

6945 G02

For more information www.linear.com/LTC6945

REFO Phase Noise

–140

–145

POUT = 1.45dBm

fREF = 10MHz

BST = 1

FILT = 3

NOTE 7

–150

–155

–160

100

1k 10k 100k 1M 5M

OFFSET FREQUENCY (Hz)

6945 G03

6945fa

5

5 Page

LTC6945

Operation

PHASE/FREQUENCY DETECTOR (PFD)

The phase/frequency detector (PFD), in conjunction with

the charge pump, produces source and sink current pulses

proportional to the phase difference between the outputs

of the R and N dividers. This action provides the necessary

feedback to phase-lock the loop, forcing a phase align-

ment at the PFD’s inputs. The PFD may be disabled with

the CPRST bit which prevents UP and DOWN pulses from

being produced. See Figure 3 for a simplified schematic

of the PFD.

R DIV

N DIV

DQ

RST

DQ

RST

UP

CPRST

DELAY

DOWN

6945 F03

Figure 3. Simplified PFD Schematic

LOCK INDICATOR

The lock indicator uses internal signals from the PFD to

measure phase coincidence between the R and N divider

output signals. It is enabled by setting the LKEN bit in

the serial port register h07, and produces both LOCK and

UNLOCK status flags, available through both the STAT

output and serial port register h00.

The user sets the phase difference lock window time,

tLWW , for a valid LOCK condition with the LKWIN[1:0]

bits. See Table 3 for recommended settings for different

fPFD frequencies and the Applications Information section

for examples.

Table 3. LKWIN[1:0] Programming

LKWIN[1:0]

0

tLWW

3ns

1 10ns

2 30ns

3 90ns

fPFD

>5MHz

≤5MHz

≤1.7MHz

≤550kHz

The PFD phase difference must be less than tLWW for the

COUNTS number of successive counts before the lock

indicator asserts the LOCK flag. The LKCT[1:0] bits found

in register h09 are used to set COUNTS depending upon

the application. See Table 4 for LKCT[1:0] programming

and the Applications Information section for examples.

Table 4. LKCT[1:0] Programming

LKCT[1:0]

0

1

2

3

COUNTS

32

128

512

2048

When the PFD phase difference is greater than tLWW , the

lock indicator immediately asserts the UNLOCK status

flag and clears the LOCK flag, indicating an out-of-lock

condition. The UNLOCK flag is immediately de-asserted

when the phase difference is less than tLWW . See Figure 4

for more details.

+tLWW

PHASE

DIFFERENCE

AT PFD

0

–tLWW

UNLOCK FLAG

LOCK FLAG

t = COUNTS/fPFD

Figure 4. UNLOCK and LOCK Timing

For more information www.linear.com/LTC6945

6945 F04

6945fa

11

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet LTC6945.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LTC694 | Microprocessor Supervisory Circuits | Linear Technology |

| LTC694-3.3 | 3.3V Microprocessor Supervisory Circuits | Linear Technology |

| LTC6943 | Dual Precision Instrumentation Switched Capacitor Building Block | Linear |

| LTC6945 | Ultralow Noise and Spurious 0.35GHz to 6GHz Integer-N Synthesizer | Linear |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |