|

|

PDF EN25B64 Data sheet ( Hoja de datos )

| Número de pieza | EN25B64 | |

| Descripción | 64 Megabit Serial Flash Memory | |

| Fabricantes | Eon Silicon Solution | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de EN25B64 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

EN25B64

EN25B64

64 Megabit Serial Flash Memory with Boot and Parameter Sectors

FEATURES

• Single power supply operation

- Full voltage range: 2.7-3.6 volt

• 64 M-bit Serial Flash

- 64 M-bit/8192 K-byte/32768 pages

- 256 bytes per programmable page

• High performance

- 100MHz clock rate

• Low power consumption

- 5 mA typical active current

- 1 μA typical power down current

• Flexible Sector Architecture:

- Two 4-Kbyte, one 8-Kbyte, one 16-Kbyte,one

32-Kbyte, and one hundred twenty-seven 64-

Kbyte sectors

• Software and Hardware Write Protection:

- Write Protect all or portion of memory via

software

- Enable/Disable protection with WP# pin

• High performance program/erase speed

- Byte program time: 7µs typical

- Page program time: 1.5ms typical

- Sector erase time: 300 to 800ms typical

- Chip erase time: 50 Seconds typical

• Lockable 512byte OTP security sector

• Minimum 100K endurance cycle

• Package Options

- 16 pins SOP 300mil body width

- All Pb-free packages are RoHS compliant

• Industrial temperature Range

GENERAL DESCRIPTION

The EN25B64 is a 64M-bit (8192K-byte) Serial Flash memory, with advanced write protection

mechanisms, accessed by a high speed SPI-compatible bus. The memory can be programmed 1 to

256 bytes at a time, using the Page Program instruction.

The EN25B64 has one hundred twenty-eight sectors including one hundred twenty-seven sectors of

64KB, one sector of 32KB, one sector of 16KB, one sector of 8KB and two sectors of 4KB. This device is

designed to allow either single Sector at a time or full chip erase operation. The EN25B64 can protect

boot code stored in the small sectors for either bottom or top boot configurations. The device can sustain

a minimum of 100K program/erase cycles on each sector.

This Data Sheet may be revised by subsequent versions 1

or modifications due to changes in technical specifications.

©2004 Eon Silicon Solution, Inc., www.essi.com.tw

Rev. C, Issue Date: 2008/06/23

1 page

EN25B64

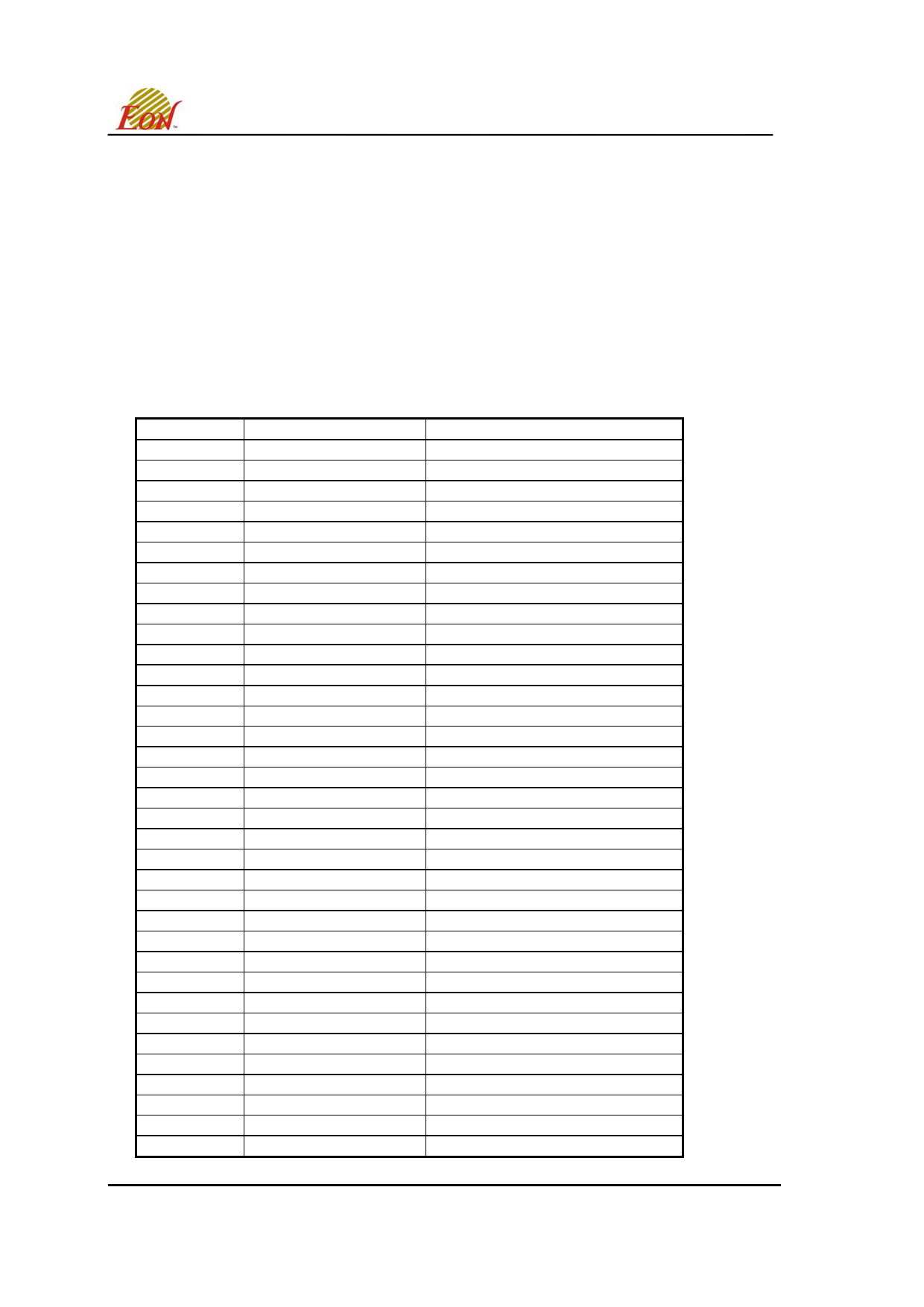

MEMORY ORGANIZATION

The memory is organized as:

z 8,388,608 bytes

z Flexible Sector Architecture

Two 4-Kbyte, one 8-Kbyte, one 16-Kbyte, one 32-Kbyte, and one hundred twenty-seven

64-Kbyte sectors

z Bottom or top boot configurations

z 32768 pages (256 bytes each)

Each page can be individually programmed (bits are programmed from 1 to 0). The device is Sector

or Bulk Erasable but not Page Erasable.

Table 2a. Bottom Boot Block Sector Architecture

Sector

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

SECTOR SIZE (KByte)

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

64

Address range

7F0000h – 7FFFFFh

7E0000h – 7EFFFFh

7D0000h – 7DFFFFh

7C0000h – 7CFFFFh

7B0000h – 7BFFFFh

7A0000h – 7AFFFFh

790000h – 79FFFFh

780000h – 78FFFFh

770000h – 77FFFFh

760000h – 76FFFFh

750000h – 75FFFFh

740000h – 74FFFFh

730000h – 73FFFFh

720000h – 72FFFFh

710000h – 71FFFFh

700000h – 70FFFFh

6F0000h – 6FFFFFh

6E0000h – 6EFFFFh

6D0000h – 6DFFFFh

6C0000h – 6CFFFFh

6B0000h – 6BFFFFh

6A0000h – 6AFFFFh

690000h – 69FFFFh

680000h – 68FFFFh

670000h – 67FFFFh

660000h – 66FFFFh

650000h – 65FFFFh

640000h – 64FFFFh

630000h – 63FFFFh

620000h – 62FFFFh

610000h – 61FFFFh

600000h – 60FFFFh

5F0000h – 5FFFFFh

5E0000h – 5EFFFFh

5D0000h – 5DFFFFh

This Data Sheet may be revised by subsequent versions

5

or modifications due to changes in technical specifications.

©2004 Eon Silicon Solution, Inc., www.essi.com.tw

Rev. C, Issue Date: 2008/06/23

5 Page

OPERATING FEATURES

EN25B64

SPI Modes

The EN25B64 is accessed through an SPI compatible bus consisting of four signals: Serial Clock

(CLK), Chip Select (CS#), Serial Data Input (DI) and Serial Data Output (DO). Both SPI bus

operation Modes 0 (0,0) and 3 (1,1) are supported. The primary difference between Mode 0 and

Mode 3, as shown in Figure 3, concerns the normal state of the CLK signal when the SPI bus

master is in standby and data is not being transferred to the Serial Flash. For Mode 0 the CLK signal

is normally low. For Mode 3 the CLK signal is normally high. In either case data input on the DI pin is

sampled on the rising edge of the CLK. Data output on the DO pin is clocked out on the falling edge

of CLK.

Figure 3. SPI Modes

Page Programming

To program one data byte, two instructions are required: Write Enable (WREN), which is one byte,

and a Page Program (PP) sequence, which consists of four bytes plus data. This is followed by the

internal Program cycle (of duration tPP).

To spread this overhead, the Page Program (PP) instruction allows up to 256 bytes to be pro-

grammed at a time (changing bits from 1 to 0), provided that they lie in consecutive addresses on

the same page of memory.

Sector Erase and Bulk Erase

The Page Program (PP) instruction allows bits to be reset from 1 to 0. Before this can be applied,

the bytes of memory need to have been erased to all 1s (FFh). This can be achieved either a sector

at a time, using the Sector Erase (SE) instruction, or throughout the entire memory, using the Bulk

Erase (BE) instruction. This starts an internal Erase cycle (of duration tSE or tBE). The Erase

instruction must be preceded by a Write Enable (WREN) instruction.

Polling During a Write, Program or Erase Cycle

A further improvement in the time to Write Status Register (WRSR), Program (PP) or Erase (SE or

BE) can be achieved by not waiting for the worst case delay (tW, tPP, tSE, or tBE). The Write In

Progress (WIP) bit is provided in the Status Register so that the application program can monitor its

value, polling it to establish when the previous Write cycle, Program cycle or Erase cycle is complete.

Active Power, Stand-by Power and Deep Power-Down Modes

When Chip Select (CS#) is Low, the device is enabled, and in the Active Power mode. When Chip

Select (CS#) is High, the device is disabled, but could remain in the Active Power mode until all

internal cycles have completed (Program, Erase, Write Status Register). The device then goes in to

the Stand-by Power mode. The device consumption drops to ICC1.

The Deep Power-down mode is entered when the specific instruction (the Enter Deep Power-down

Mode (DP) instruction) is executed. The device consumption drops further to ICC2. The device re-

mains in this mode until another specific instruction (the Release from Deep Power-down Mode and

Read Device ID (RDI) instruction) is executed.

This Data Sheet may be revised by subsequent versions 11 ©2004 Eon Silicon Solution, Inc., www.essi.com.tw

or modifications due to changes in technical specifications.

Rev. C, Issue Date: 2008/06/23

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet EN25B64.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EN25B64 | 64 Megabit Serial Flash Memory | Eon Silicon Solution |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |