|

|

PDF TH58NVG7D2GTA20 Data sheet ( Hoja de datos )

| Número de pieza | TH58NVG7D2GTA20 | |

| Descripción | 128 GBIT (8G x 8-BIT x 2) CMOS NAND E2PROM | |

| Fabricantes | Toshiba | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TH58NVG7D2GTA20 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

TOSHIBA CONFIDENTIAL TH58NVG7D2GTA20

TENTATIVE TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

128 GBIT (8G 8 BIT 2) CMOS NAND E2PROM (Multi-Level-Cell)

DESCRIPTION

The TH58NVG7D2G is a single 3.3 V 128 Gbit (149,189,296,128 bits) NAND Electrically Erasable and

Programmable Read-Only Memory (NAND E2PROM) organized as (8192 + 640) bytes 256 pages 8248 blocks.

The device has two 8832-byte static registers which allow program and read data to be transferred between the

register and the memory cell array in 8832-byte increments. The Erase operation is implemented in a single block

unit (2 Mbytes 160 Kbytes: 8832 bytes 256 pages).

The TH58NVG7D2G is a serial-type memory device which utilizes the I/O pins for both address and data

input/output as well as for command inputs. The Erase and Program operations are automatically executed making

the device most suitable for applications such as solid-state file storage, voice recording, image file memory for still

cameras and other systems which require high-density non-volatile memory data storage.

FEATURES

Organization

Memory cell array

Register

Page size

Block size

TH58NVG7D2G

8832 512K 8 2

8832 8

8832 bytes

(2M 160 K) bytes

Modes

Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Page Copy,

Multi Page Program, Multi Block Erase, Multi Page Copy, Multi Page Read

Mode control

Serial input/output

Command control

Number of valid blocks

Min 7992 blocks

Max 8248 blocks

Power supply

VCC 2.7 V to 3.6 V

Access time

Cell array to register 200 s max

Serial Read Cycle

25 ns min

Program/Erase time

Auto Page Program

Auto Block Erase

1400 s/page typ.

5 ms/block typ.

Operating current

Read (25 ns cycle)

Program (avg.)

Erase (avg.)

Standby

TBD ( 30 mA max.) per 1chip

TBD ( 30 mA max.) per 1chip

TBD ( 30 mA max.) per 1chip

100 A max

Package

(Weight: TBD g typ.)

FOR RELIABILITY GUIDANCE, PLEASE REFER TO THE APPLICATION NOTES AND COMMENTS (16).

1 2010-10-29C

1 page

TOSHIBA CONFIDENTIAL TH58NVG7D2GTA20

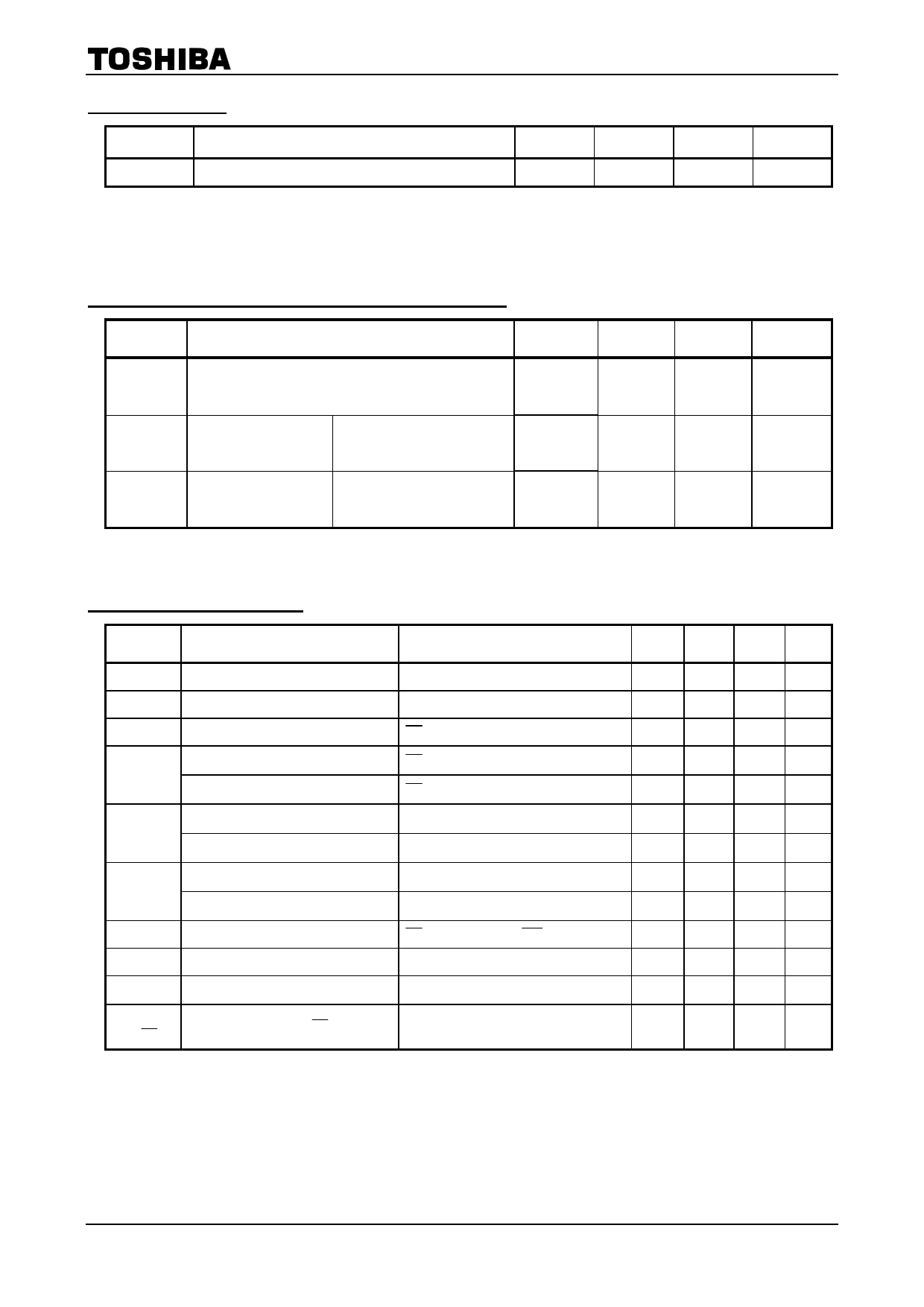

VALID BLOCKS

SYMBOL

PARAMETER

MIN

TYP.

MAX

UNIT

NVB Number of Valid Blocks

7992

8248

Blocks

NOTE:

The device occasionally contains unusable blocks. Refer to Application Note (12) toward the end of this document.

The first block (Block 0) is guaranteed to be a valid block at the time of shipment.

The specification for the minimum number of valid blocks is applicable over the device lifetime.

* The number of valid blocks includes extended blocks.

RECOMMENDED DC OPERATING CONDITIONS

SYMBOL

PARAMETER

MIN

TYP.

MAX

UNIT

VCC Power Supply Voltage

2.7 V

3.6 V

V

VIH High Level input Voltage 2.7 V VCC 3.6 V

0.8 x Vcc

VCC 0.3

V

VIL Low Level Input Voltage 2.7 V VCC 3.6 V

* 2 V (pulse width lower than 20 ns)

0.3*

0.2 x Vcc

V

DC CHARACTERISTICS (Ta 0 to 70℃, VCC 2.7 V to 3.6 V)

SYMBOL

PARAMETER

CONDITION

IIL Input Leakage Current

VIN 0 V to VCC

ILO

ICCO0*1,*3

Output Leakage Current

Power On Reset Current

VOUT 0 V to VCC

CE VIL

ICCO1*2,*3

Serial Read Current(Single page)

Serial Read Current( Multi-page )

CE VIL, IOUT 0 mA, tcycle 25 ns

CE VIL, IOUT 0 mA, tcycle 25 ns

ICCO2*2,*3

Programming Current( Single page )

Programming current( Multi-page )

ICCO3*2,*3

Single Block Erasing current

Multi-block Erasing current

ICCS

VOH

VOL

IOL

( RY / BY )

Standby Current

High Level Output Voltage

Low Level Output Voltage

Output current of RY / BY pin

CE VCC 0.2 V, WP 0 V/VCC,

IOH 0.4 mA (2.7 V VCC 3.6 V)

IOL 2.1 mA (2.7 V VCC 3.6 V)

VOL 0.4 V (2.7 V VCC 3.6 V)

*1: Icco0 is the average current during R/B signal=”Busy” state.

*2: All operation current are without data cache.

*3: Icco 0/1/2/3 are the value of one chip, and an unselected chip is in Standy mode.

MIN TYP. MAX UNIT

10 A

10 A

TBD mA

TBD mA

TBD mA

TBD mA

TBD mA

TBD mA

TBD mA

100 A

2.4 V

0.4 V

8 mA

5 2010-10-29C

5 Page

TOSHIBA CONFIDENTIAL TH58NVG7D2GTA20

Extended Blocks Arrangement

The device has 28 extended blocks to increase valid blocks. Extended blocks can be accessed by the following

addressing.

Page Address( PA0-20 )

00000h

00100h

00200h

00300h

00400h

00500h

|

FFE00h

FFF00h

100000h

100100h

|

101A00h

101B00h

101C00h – FFFFFFh

64Gbits

Block 0( District 0 )

Block 1( District 1 )

Block 2( District 0 )

Block 3( District 1 )

Block 4( District 0 )

Block 5( District 1 )

|

Block 4094( District 0 )

Block 4095( District 1 )

Block 4096( District 0 )

Block 4097( District 1 )

|

Block 4122( District 0 )

Block 4123( District 1 )

Address Gap

Main Blocks

( 4096 blocks )

Extended

Blocks

( 28 blcoks )

30 2010-10-29C

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet TH58NVG7D2GTA20.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TH58NVG7D2GTA20 | 128 GBIT (8G x 8-BIT x 2) CMOS NAND E2PROM | Toshiba |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |