|

|

PDF NCV7517B Data sheet ( Hoja de datos )

| Número de pieza | NCV7517B | |

| Descripción | Hex Low-Side MOSFET Pre-Driver | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NCV7517B (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

NCV7517B

FLEXMOSt Hex Low-Side

MOSFET Pre-Driver

The NCV7517B programmable six channel low−side MOSFET

pre−driver is one of a family of FLEXMOSTM automotive grade

products for driving logic−level MOSFETs. The product is

controllable by a combination of serial SPI and parallel inputs. It

features programmable fault management modes and allows

power−limiting PWM operation with programmable refresh time.

The device offers 3.3 V/5.0 V compatible inputs and the serial output

driver can be powered from either 3.3 V or 5.0 V. Power−on reset

provides controlled powerup and two enable inputs allow all outputs

to be simultaneously disabled.

Each channel independently monitors its external MOSFET’s

drain voltage for fault conditions. Shorted load fault detection

thresholds are fully programmable using an externally programmed

reference voltage and a combination of four discrete internal ratio

values. The ratio values are SPI selectable and allow different

detection thresholds for each group of three output channels.

Fault information for each channel is 2−bit encoded by fault type

and is available through SPI communication. Fault recovery

operation for each channel is programmable and may be selected for

latch−off or automatic retry.

The FLEXMOS family of products offers application scalability

through choice of external MOSFETs.

Features

• 16−Bit SPI with Frame Error Detection

• 3.3 V/5.0 V Compatible Parallel and Serial Control Inputs

• 3.3 V/5.0 V Compatible Serial Output Driver

• Two Enable Inputs

• Open−Drain Fault and Status Flags

• Programmable

− Shorted Load Fault Detection Thresholds

− Fault Recovery Mode

− Fault Retry Timer

− Flag Masking

• Load Diagnostics with Latched Unique Fault Type Data

− Shorted Load

− Open Load

− Short to GND

• NCV Prefix for Automotive and Other Applications Requiring

Unique Site and Control Change Requirements; AEC−Q100

Qualified and PPAP Capable

• These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS

Compliant

Benefits

• Scalable to Load by Choice of External MOSFET

www.onsemi.com

MARKING

DIAGRAM

LQFP32

FT SUFFIX

CASE 561AB

NCV7517B

AWLYYWWG

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb−Free Package

ORDERING INFORMATION

Device

NCV7517BFTG

Package

LQFP

(Pb−Free)

Shipping†

250 Units/Tray

NCV7517BFTR2G LQFP 2000 Tape & Reel

(Pb−Free)

†For information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specification

Brochure, BRD8011/D.

© Semiconductor Components Industries, LLC, 2016

June, 2016 − Rev. 2

1

Publication Order Number:

NCV7517B/D

1 page

NCV7517B

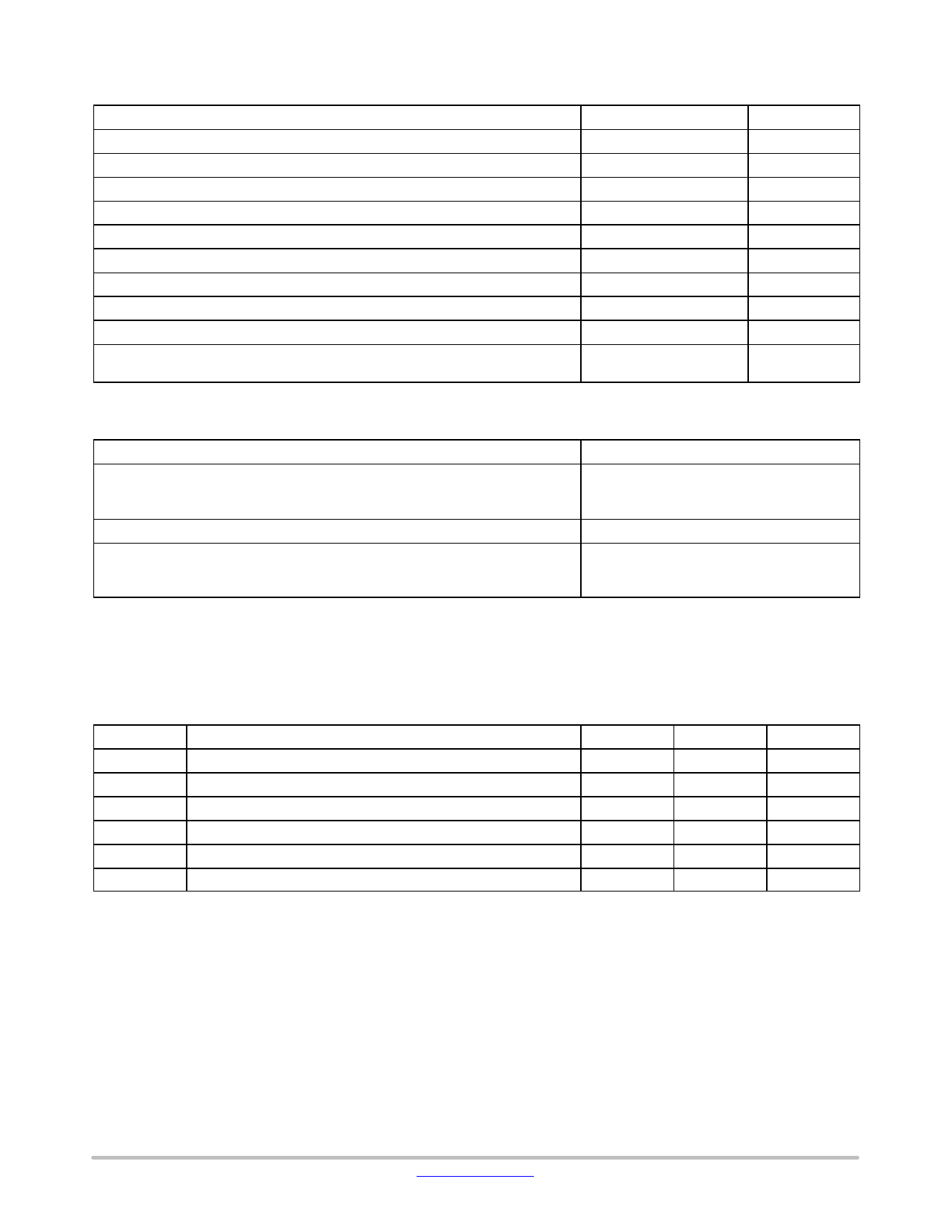

MAXIMUM RATINGS (Voltages are with respect to device substrate.)

Rating

Value

Unit

DC Supply (VCC1, VCC2, VDD)

Difference Between VCC1 and VCC2

Difference Between GND (Substrate) and VSS

Output Voltage (Any Output)

−0.3 to 6.5

"0.3

"0.3

−0.3 to 6.5

V

V

V

V

Drain Feedback Clamp Voltage (Note 1)

−0.3 to 47

V

Drain Feedback Clamp Current (Note 1)

10 mA

Input Voltage (Any Input)

−0.3 to 6.5

V

Junction Temperature, TJ

Storage Temperature, TSTG

Peak Reflow Soldering Temperature: Lead−Free

60 to 150 seconds at 217°C (Note 2)

−40 to 150

−65 to 150

260 peak

°C

°C

°C

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

should not be assumed, damage may occur and reliability may be affected.

ATTRIBUTES

Characteristic

Value

ESD Capability

Human Body Model

Machine Model

w " 2.0 kV

w " 200 V

Moisture Sensitivity (Note 2)

MSL2

Package Thermal Resistance (Note 3)

Junction–to–Ambient, RqJA

Junction–to–Pin, RYJL

86.0 °C/W

58.5 °C/W

1. An external series resistor must be connected between the MOSFET drain and the feedback input in the application. Total clamp power

dissipation is limited by the maximum junction temperature, the application environment temperature, and the package thermal resistances.

2. For additional information, see or download ON Semiconductor’s Soldering and Mounting Techniques Reference Manual, SOLDERRM/D, and

Application Note AND8003/D.

3. Values represent still air steady−state thermal performance on a 4 layer (42 x 42 x 1.5 mm) PCB with 1 oz. copper on an FR4 substrate, using

a minimum width signal trace pattern (384 mm2 trace area).

RECOMMENDED OPERATING CONDITIONS

Symbol

Parameter

Min Max Unit

VCC1

Main Power Supply Voltage

4.75 5.25

V

VCC2

Gate Drivers Power Supply Voltage

VCC1 − 0.3

VCC1 + 0.3

V

VDD Serial Output Driver Power Supply Voltage

3.0 VCC1

V

VIN High

Logic High Input Voltage

2.0 VCC1

V

VIN Low

Logic Low Input Voltage

0 0.8 V

TA Ambient Still−Air Operating Temperature

−40 125

°C

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the

Recommended Operating Ranges limits may affect device reliability.

www.onsemi.com

5

5 Page

NCV7517B

DETAILED OPERATING DESCRIPTION

General

The NCV7517B is a six channel general purpose

low−side pre−driver for controlling and protecting N−type

logic level MOSFETs. While specifically designed for

driving MOSFETs with resistive, inductive or lamp loads

in automotive applications, the device is also suitable for

industrial and commercial applications. Programmable

fault detection and protection modes allow the NCV7517B

to accommodate a wide range of external MOSFETs and

loads, providing the user with flexible application

solutions. Separate power supply pins are provided

for low and high current paths to improve analog

accuracy and digital signal integrity. ON Semiconductor’s

SMARTDISCRETESTM clamp MOSFETs, such as the

NID9N05CL, are recommended when driving unclamped

inductive loads.

Power Up/Down Control

The NCV7517B’s powerup/down control prevents

spurious output operation by monitoring the VCC1 power

supply. An internal Power−On Reset (POR) circuit causes

all GATX outputs to be held low until sufficient voltage is

available to allow proper control of the device. All internal

registers are initialized to their default states, fault data is

cleared, and the open−drain fault (FLTB) and status

(STAB) flags are disabled.

When VCC1 exceeds the POR threshold, outputs and

flags are enabled and the device is ready to accept input

data. When VCC1 falls below the POR threshold during

power down, flags are reset and disabled and all GATX

outputs are driven and held low until VCC1 falls below

about 0.7 V.

SPI Communication

The NCV7517B is a 16−bit SPI slave device. SPI

communication between the host and the NCV7517B may

either be parallel via individual CSB addressing or

daisy−chained through other devices using a compatible

SPI protocol.

The active−low CSB chip select input has a pullup

current source. The SI and SCLK inputs have pulldown

current sources. The recommended idle state for SCLK is

low. The tri−state SO line driver can be supplied with either

3.3 or 5.0 V and is powered via the device’s VDD and VSS

pins.

The NCV7517B employs frame error detection that

requires integer multiples of 16 SCLK cycles during each

CSB high−low−high cycle (valid communication frame.)

A frame error does not affect the flags. The CSB input

controls SPI data transfer and initializes the selected

device’s frame error and fault reporting logic.

The host initiates communication when a selected

device’s CSB pin goes low. Output (fault) data is

simultaneously sent MSB first from the SO pin while input

(command) data is received MSB first at the SI pin under

synchronous control of the master’s SCLK signal while

CSB is held low (Figure 10). Fault data changes on the

falling edge of SCLK and is guaranteed valid before the

next rising edge of SCLK. Command data received must be

valid before the rising edge of SCLK.

When CSB goes low, frame error detection is initialized,

latched fault data is transferred to the SPI, and the FLTB

flag is disabled and reset if previously set. Data for faults

detected while CSB is low are ignored but will be captured

if still present after CSB goes high.

If a valid frame has been received when CSB goes high,

the last multiple of 16 bits received is decoded into

command data, and FLTB is re−enabled. Latched

(previous) fault data is cleared and current fault data is

captured. The FLTB flag will be set if a fault is detected.

If a frame error is detected when CSB goes high, new

command data is ignored, and previous fault data remains

latched and available for retrieval during the next valid

frame. The FLTB flag will be set if a fault (not a frame

error) is detected.

CSB

SCLK

MSB

1

2

SI X B15

B14

3

B13

4 − 13

B12 − B3

14

B2

15

B1

SO

B15 B14

B13

B12 − B3

B2 B1

Note: X=Don’t Care, Z=Tri−State, UKN=Unknown Data

Figure 10. SPI Communication Frame Format

LSB

16

B0 X

B0 UKN Z

www.onsemi.com

11

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet NCV7517B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NCV7517 | Hex Low-side Predriver | ON Semiconductor |

| NCV7517B | Hex Low-Side MOSFET Pre-Driver | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |