|

|

PDF AFE1230 Data sheet ( Hoja de datos )

| Número de pieza | AFE1230 | |

| Descripción | G.SHDSL ANALOG FRONT-END | |

| Fabricantes | Burr-Brown Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AFE1230 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

AFE1230

AFE1230

SBWS015A – AUGUST 2001

G.SHDSL ANALOG FRONT-END

FEATURES

q E1, T1, AND SUBRATE OPERATION

q COMPLIES WITH G.SHDSL AND HDSL2

q 16-BIT, DELTA-SIGMA CONVERTERS

q ON-CHIP DRIVER AND PGA

q PROGRAMMABLE tx AND rx FILTERS

q SERIAL DIGITAL INTERFACE

q 750mW POWER DISSIPATION AT E1

q +5V POWER (5V OR 3.3V DIGITAL)

q SSOP-28 PACKAGE

q –40°C TO +85°C TEMPERATURE RANGE

DESCRIPTION

Texas Instrument’s analog front-end chip, the AFE1230, is

designed to greatly reduce the size and cost of G.SHDSL

and HDSL2 application designs. It provides a transceiver as

the line interface between the Digital Signal Processor

(DSP) and the local loop. The AFE1230 is designed to

handle upstream and downstream data transmission over a

wide range of data rates from 64kbps to 2.5Mbps. Function-

ally, this unit consists of a transmitter and receiver section.

The transmitter section consists of a digital interpolation

filter, a 16-bit, delta-sigma Digital-to-Analog (D/A) con-

verter, a digitally programmable fifth-order or seventh-order

SC (Switched Capacitor) low-pass filter, and a differential

output line driver. The receiver section includes an input

Programmable Gain Amplifier (PGA), a 16-bit, delta-sigma

Analog-to-Digital (A/D) converter, and a programmable

decimation filter.

The AFE1230 receives a 16-bit data word plus an 8-bit control

byte via the serial interface to facilitate the D/A conversion

and control functions. The subsequent analog signal is sent to

the on-chip line driver that provides 14.5dBm power into a

135Ω line for G.SHDSL operation. In addition, the on-chip

line driver can be used as an output buffer with an external line

driver, such as the OPA2677, to generate over 17dBm power

into a 135Ω line for HDSL2 operation. With an appropriate

DSP, the transmitted Power Spectral Density (PSD) complies

with either the G.SHDSL standard or with the HDSL2 stan-

dard (via an OPA2677 used as an external driver).

In the receive path, the input amplifier sums the signals from

the line and hybrid path to perform first-order analog echo

cancellation. The resultant signal is then digitized by the rest

of the receive section into a 16-bit digital word that is sent to

the external DSP.

This IC operates on a single 5V supply, while the digital supply

can be from 3.3V to 5V. It is housed in a SSOP-28 package.

The typical power consumption is 750mW at E1 rates with

G.SHDSL (560mW for HDSL2 operation) and an operation

temperature range of –40°C to +85°C.

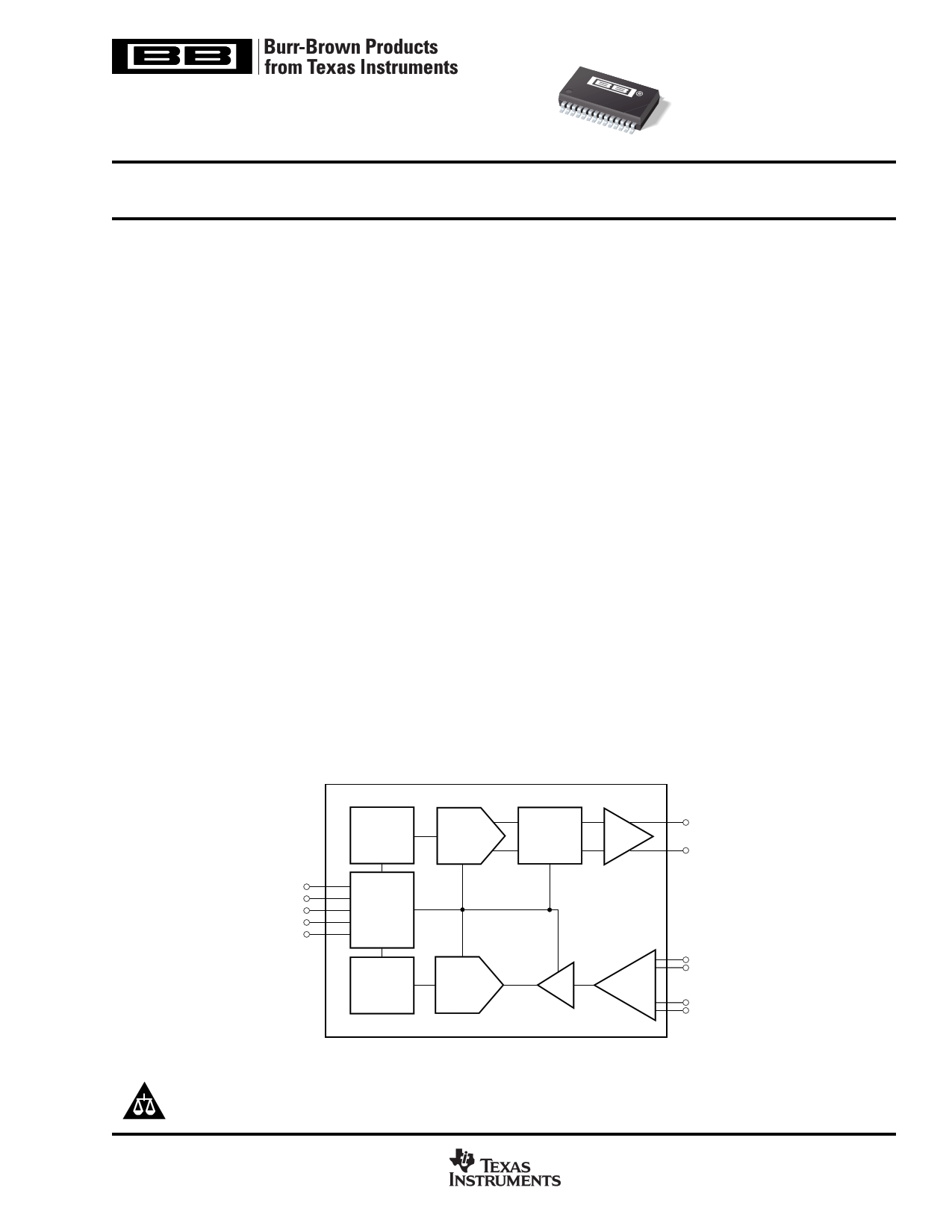

Digital

Interpolation

LPF

∆Σ 16-Bit

D/A Converter

Programmable

SC

LPF

Driver/

Buffer

txLINE

txLINE

MCLK

txBaud

txData

rxBaud

rxData

tx and rx

Digital

Interface

Registers

Programmable

Digital

LPF

∆Σ 16-Bit

A/D Converter

PGA

Input

Amplifier

hybINPUT

hybINPUT

rxINPUT

rxINPUT

AFE1230

Patents Pending

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

www.ti.com

Copyright © 2001, Texas Instruments Incorporated

1 page

0

–50

–100

–150

–200

–250

–300

10–3

10–2

10–1

100

FIGURE 2. Overall Transmit Filter. D/A Converter Frequency Response, Fifth-Order with 0.25x, 0.38x, and 0.5x.

0

–50

–100

–150

–200

–250

–300

–350

10–3

10–2

10–1

100

FIGURE 3. Overall Transmit Filter. D/A Converter Frequency Response, Seventh-Order with 0.25x, 0.38x, and 0.5x.

Receive Filter

The receive filter consists of three independent sections used

for both the removal of quantization noise as well as the

reduction of data rate (otherwise known as downsampling).

The first section is comprised of a sinc5 filter with a

downsampling ratio of 12x. The resulting digital signal is then

passed to a droop compensation filter before being sent

through the final IIR filter section, while being downsampled

by two. Two filter cutoff configurations are available, as seen

in Table II. The corresponding cutoff frequencies relate to the

full-rate low-pass filter spectral template of the filter, as seen

from the inputs of Table II.

rx CUTOFF (txData Bit 24)

RATIO (Corner Frequency)

0 0.25 MCLK/24

1 0.5 MCLK/24

TABLE II. rx Filter Cutoff Frequency Setting.

Transmit Power

The on-chip differential line driver is designed to drive G.SHDSL

power levels directly, or it can be used as a low-power buffer for

driving a higher power external driver (for example the OPA2677)

for applications such as HDSL2. The AFE1230 driver will

generate an output swing of 6.2V peak-to-peak differential.

When used with a suitable transformer (see Figures 8 and 10),

the AFE1230 can generate up to 14.5dBm of power into a 135Ω

line load. When used as a buffer with an OPA2677 driver,

17dBm of power can be generated. Relative transmit power can

be controlled digitally through control bits sent to the transmit

section by the serial interface. Relative transmit power reduction

can be set to 0, –6, –12, or –18dB, depending on the control bits

presented to the AFE1230, as shown in Table III.

TRANSMIT POWER

BACK OFF CODE

(txData Bits 25, 26)

TRANSMIT

POWER

REDUCTION

TRANSMIT POWER

G.SHDSL HDSL2

00 0dB 14.5dBm 17.0dBm

01

–6dB

8.5dBm 11.0dBm

10

–12dB

2.5dBm

5.0dBm

11

–18dB

–4.5dBm –1.0dBm

TABLE III. Transmit Power Backoff.

AFE1230

SBWS015A

5

5 Page

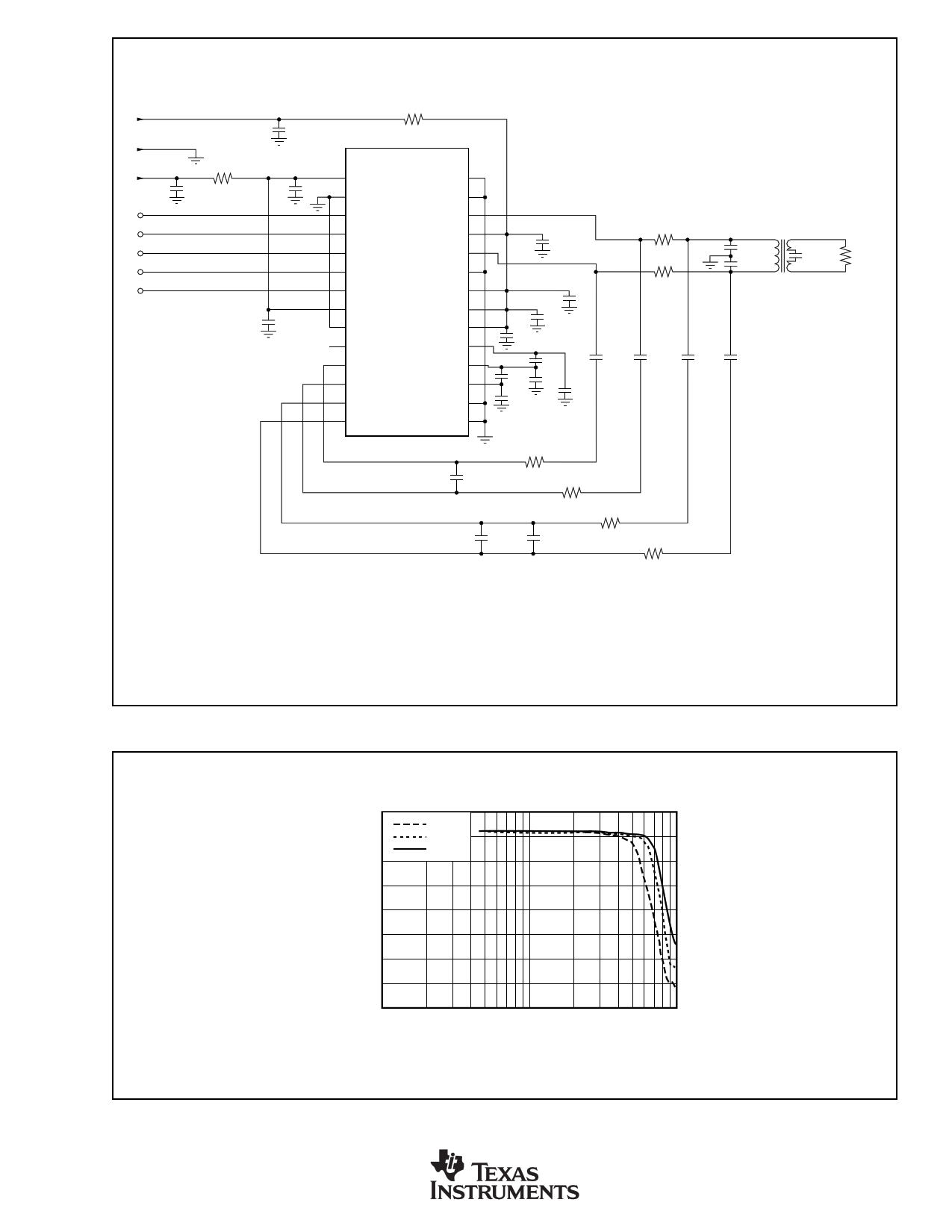

AVDD

GND

DVDD

0Ω

10µF

10µF

0Ω

C(1)

C(1)

1

DVDD

2

GNDD

3

txBaud

4

txData

5

MCLK

6

rxBaud

7

rxData

8

DVDD

9

GNDD

10

GNDA

11

HybP

12

HybM

13

LineP

14

LineM

AFE1230

GNDA

GNDA

txOutP

AVDD

txOutM

GNDA

AVDD

AVDD

AVDD

VREFM

VCM

VREFP

GNDA

GNDA

28

27

26

25

24

23

22

21

20

19

18

17

16

15

6.8pF(3)

C(1)

C(1)

C(1)

C(1)

C(1)

C(1)

C(1)

C(1)

0.1µF

R3

20kΩ

R5

20kΩ

R4

10kΩ

3.3pF(3)

10pF(3)

R1

4.99Ω

R2

4.99Ω

0.1µF

R6

10kΩ

1:3.7(2)

53nF

Zi(f)

53nF

0.47µF

0.1µF

0.1µF

135Ω

NOTES: (1) C = 0.1µF (Ceramic SMT). (2) Transformer = Midcom—

51185. (3) These components provide low-pass filtering to the input signal

and are optional, since the AFE1230 provides an internal low-pass filter

with 1MHz cutoff frequency on the front end of the receiver, as well as

oversampling by the A/D converter.

FIGURE 8. AFE1230 Line Interface with 14.5dBm Line Power for G.SHDSL.

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

10k

0.25x

0.38x

0.5x

100k

Logarithmic Scale (10kHz to 1000kHz)

1M

FIGURE 9. AFE1230 Transmit PSD with 30MHz of Master Clock, Seventh-Order tx Filter and Cutoff Frequency Ratio of 0.5x,

0.38x, and 0.25x.

AFE1230

SBWS015A

11

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet AFE1230.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AFE1230 | AFE1230: G.SHDSL Analog Front-End (Rev. A) | Texas Instruments |

| AFE1230 | G.SHDSL ANALOG FRONT-END | Burr-Brown Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |