|

|

PDF 54HC589 Data sheet ( Hoja de datos )

| Número de pieza | 54HC589 | |

| Descripción | 8-Bit Serial or Parallel-Input/Serial-Output Shift Register | |

| Fabricantes | Motorola Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 54HC589 (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

8-Bit Serial or Parallel-Input/

Serial-Output Shift Register

with 3-State Output

High–Performance Silicon–Gate CMOS

The MC54/74HC589 is similar in function to the HC597, which is not a

3–state device. The device inputs are compatible with standard CMOS

outputs, with pullup resistors, they are compatible with LSTTL outputs.

This device consists of an 8–bit storage latch which feeds parallel data to

an 8–bit shift register. Data can also be loaded serially (see Function Table).

The shift register output, QH, is a three–state output, allowing this device to

be used in bus–oriented systems.

The HC589 directly interfaces with the Motorola SPI serial data port on

CMOS MPUs and MCUs.

• Output Drive Capability: 15 LSTTL Loads

• Outputs Directly Interface to CMOS, NMOS, and TTL

• Operating Voltage Range: 2 to 6 V

• Low Input Current: 1 µA

• High Noise Immunity Characteristic of CMOS Devices

• In Compliance with the Requirements Defined by JEDEC Standard

No. 7A

• Chip Complexity: 526 FETs or 131.5 Equivalent Gates

MC54/74HC589

16

1

J SUFFIX

CERAMIC PACKAGE

CASE 620–10

16

1

N SUFFIX

PLASTIC PACKAGE

CASE 648–08

16

1

D SUFFIX

SOIC PACKAGE

CASE 751B–05

ORDERING INFORMATION

MC54HCXXXJ

MC74HCXXXN

MC74HCXXXD

Ceramic

Plastic

SOIC

SERIAL

DATA

INPUT

SA 14

PARALLEL

DATA

INPUTS

A 15

B1

C2

D3

E4

F5

G6

H7

LATCH CLOCK 12

SHIFT CLOCK 11

SERIAL SHIFT/

PARALLEL LOAD

OUTPUT ENABLE

13

10

LOGIC DIAGRAM

DATA

LATCH

SHIFT

REGISTER

VCC = PIN 16

GND = PIN 8

9 QH

SERIAL

DATA

OUTPUT

PIN ASSIGNMENT

B1

C2

16 VCC

15 A

D3

E4

F5

14 SA

13

SERIAL SHIFT/

PARALLEL LOAD

12 LATCH CLOCK

G6

H7

11 SHIFT CLOCK

10 OUTPUT ENABLE

GND 8

9 QH

www.DataSheet4U.com

10/95

© Motorola, Inc. 1995

3–1 REV 6

1 page

MC54/74HC589

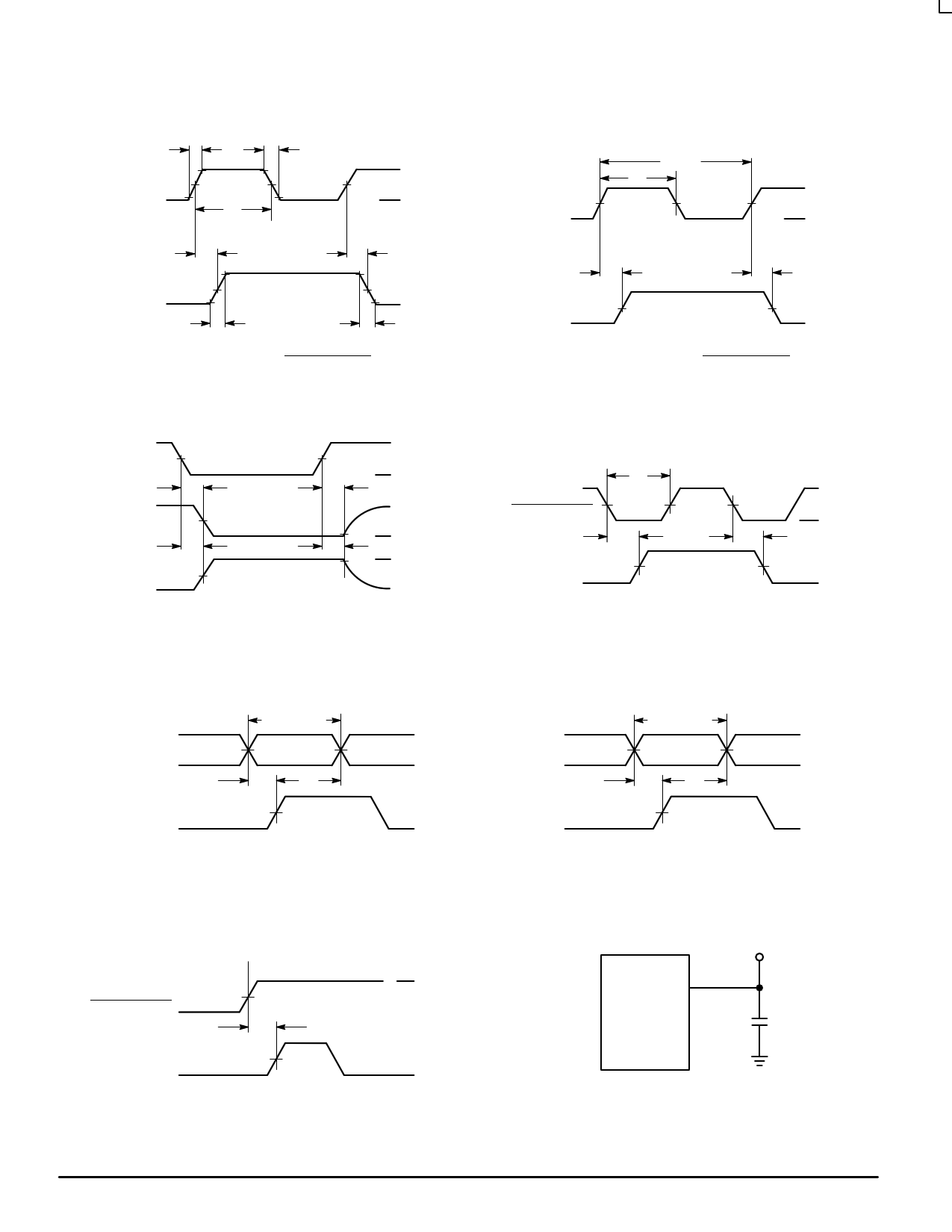

LATCH CLOCK

tr

90%

50%

10%

tw

tf

tPLH tPHL

QH

90%

50%

10%

tTLH tTHL

SWITCHING WAVEFORMS

VCC

1/fmax

tw

GND

SHIFT CLOCK

50%

QH 50%

tPLH

tPHL

VCC

GND

Figure 1. (Serial Shift/Parallel Load = L)

Figure 2. (Serial Shift/Parallel Load = H)

OUTPUT

ENABLE

QH

QH

50%

tPZL tPLZ

50%

tPZH tPHZ

50%

Figure 3.

VCC

GND

HIGH

IMPEDANCE

10% VOL

90% VOH

HIGH

IMPEDANCE

SERIAL SHIFT/

PARALLEL LOAD

QH

tw

50%

tPLH

50%

50%

tPHL

Figure 4.

VCC

GND

A–H

LATCH CLOCK

DATA VALID

50%

tsu th

50%

Figure 5.

SERIAL SHIFT/

PARALLEL LOAD

SHIFT CLOCK

50%

tsu

50%

Figure 7.

High–Speed CMOS Logic Data

DL129 — Rev 6

VCC

SA

GND

SHIFT CLOCK

DATA VALID

50%

tsu th

50%

Figure 6.

VCC

GND

TEST POINT

VCC OUTPUT

DEVICE

GND UNDER

TEST

CL*

* Includes all probe and jig capacitance

Figure 8. Test Circuit

3–5 MOTOROLA

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet 54HC589.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 54HC589 | 8-Bit Serial or Parallel-Input/Serial-Output Shift Register | Motorola Semiconductors |

| 54HC589A | 8-Bit Serial or Parallel-Input/Serial-Output Shift Register | Motorola Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |