|

|

PDF ADT7518 Data sheet ( Hoja de datos )

| Número de pieza | ADT7518 | |

| Descripción | 4-Channel ADC and Quad Voltage Output DAC | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADT7518 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

SPI/I2C Compatible, Temperature Sensor,

4-Channel ADC and Quad Voltage Output DAC

ADT7518

FEATURES

Four 8-bit DACs

Buffered voltage output

Guaranteed monotonic by design over all codes

10-bit temperature-to-digital converter

10-bit 4-channel ADC

DC input bandwidth

Input range: 0 V to 2.25 V

Temperature range: –40°C to +120°C

Temperature sensor accuracy of typ: ±0.5°C

Supply range: 2.7 V to 5.5 V

DAC output range: 0 V to 2 VREF

Power-down current: 1 µA

Internal 2.25 VREF option

Double-buffered input logic

Buffered reference input

Power-on reset to 0 V DAC output

Simultaneous update of outputs (LDAC function)

On-chip rail-to-rail output buffer amplifier

SPI®, I2C®, QSPI™, MICROWIRE™, and DSP-compatible

4-wire serial interface

SMBus packet error checking (PEC)-compatible

16-lead QSOP package

GENERAL DESCRIPTION

The ADT75181 combines a 10-bit temperature-to-digital

converter, a 10-bit 4-channel ADC, and a quad 8-bit DAC, in a

16-lead QSOP package. The part also includes a band gap

temperature sensor and a 10-bit ADC to monitor and digitize

the temperature reading to a resolution of 0.25°C.

The ADT7518 operates from a single 2.7 V to 5.5 V supply. The

input voltage range on the ADC channels is 0 V to 2.25 V, and

the input bandwidth is dc. The reference for the ADC channels

is derived internally. The output voltage of the DAC ranges

from 0 V to VDD, with an output voltage settling time of 7 ms

typical.

The ADT7518 provides two serial interface options: a 4-wire

serial interface that is compatible with SPI, QSPI, MICROWIRE,

and DSP interface standards, and a 2-wire SMBus/I2C interface.

It features a standby mode that is controlled through the serial

interface.

APPLICATIONS

Portable battery-powered instruments

Personal computers

Smart battery chargers

Telecommunications systems

Electronic text equipment

Domestic appliances

Process control

PIN CONFIGURATION

VOUT-B 1

16 VOUT-C

VOUT-A 2

15 VOUT-D

VREF-IN 3

14 AIN4

CS 4 ADT7518 13 SCL/SCLK

GND 5 TOP VIEW 12 SDA/DIN

(Not to Scale)

VDD 6

11 DOUT/ADD

D+/AIN1 7

10 INT/INT

D–/AIN2 8

9 LDAC/AIN3

Figure 1.

The reference for the four DACs is derived either internally or

from a reference pin. The outputs of all DACs may be updated

simultaneously using the software LDAC function or the exter-

nal LDAC pin. The ADT7518 incorporates a power-on reset

circuit, which ensures that the DAC output powers up to 0 V

and remains there until a valid write takes place.

The ADT7518’s wide supply voltage range, low supply current,

and SPI-/I2C-compatible interface make it ideal for a variety of

applications, including personal computers, office equipment,

and domestic appliances.

It is recommended that new designs use the ADT7519 rather

than the ADT7518. The ADT7518’s internal and external temp-

erature accuracy spec is only valid when not using the internal

reference for the on-chip DAC. The ADT7519 does not have

this limitation.

1 Protected by the following U.S. Patent Numbers: 6,169,442; 5,867,012;

5,764174. Other patents pending.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

1 page

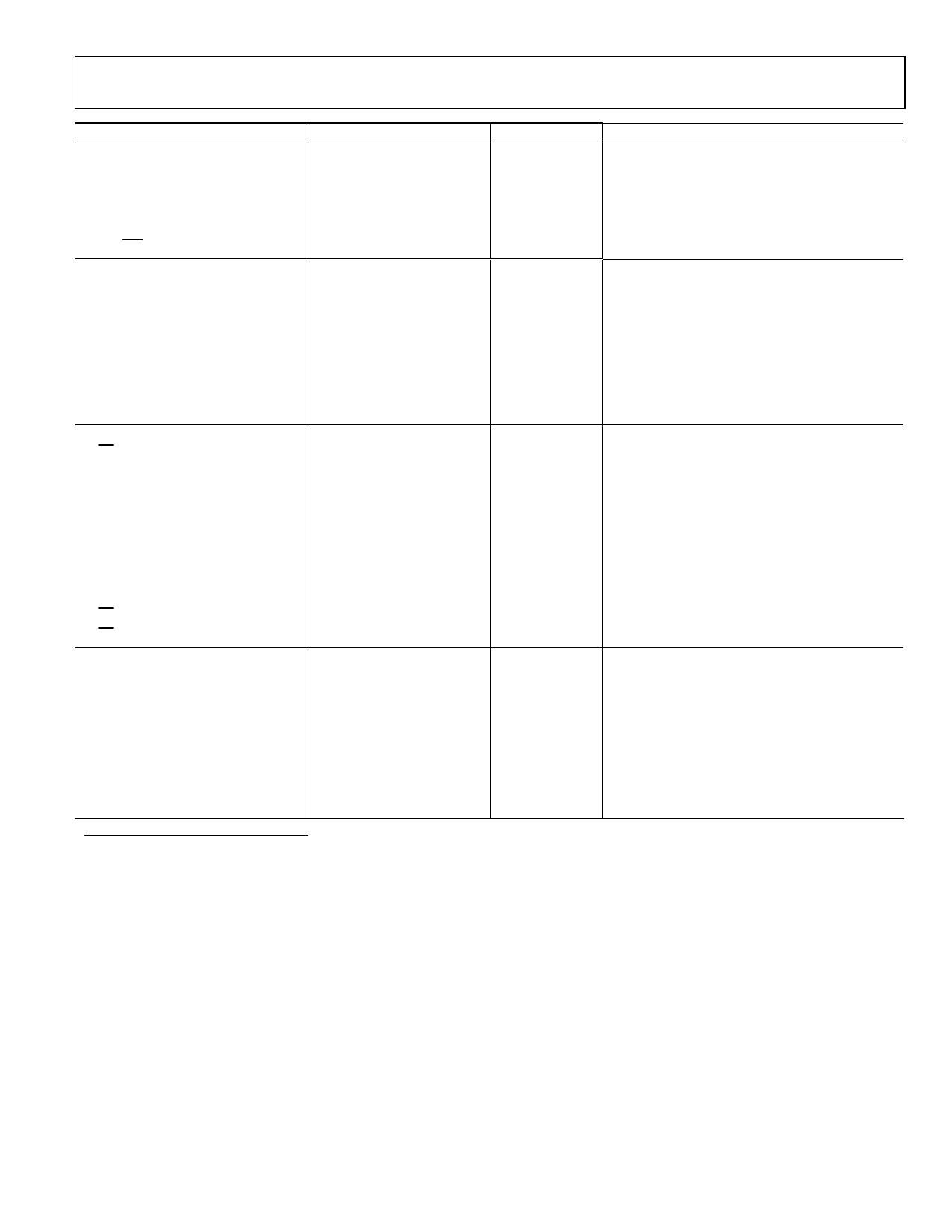

ADT7518

Parameter1

Min Typ Max

DIGITAL OUTPUT

Digital High Voltage, VOH

2.4

Output Low Voltage, VOL

Output High Current, IOH

Output Capacitance, COUT

INT/INT Output Saturation Voltage

0.4

1

50

0.8

I2C TIMING CHARACTERISTICS 8, 9

Serial Clock Period, t1

Data In Setup Time to SCL High, t2

Data Out Stable after SCL Low, t3

SDA Low Setup Time to SCL

Low (Start Condition), t4

SDA High Hold Time after SCL

High (Stop Condition), t5

SDA and SCL Fall Time, t6

SPI TIMING CHARACTERISTICS4, 10

2.5

50

0

50

50

90

CS to SCLK Setup Time, t1

0

SCLK High Pulse Width, t2

SCLK Low Pulse Width, t3

Data Access Time after SCLK

Falling Edge, t4 11

Data Setup Time Prior to SCLK

Rising Edge, t5

Data Hold Time after SCLK Rising

Edge, t6

CS to SCLK Hold Time, t7

50

50

20

0

0

35

CS to DOUT High Impedance, t8

40

POWER REQUIREMENTS

VDD 2.7 5.5

VDD Settling Time

IDD (Normal Mode) 12

50

3

2.2 3

IDD (Power-Down Mode)

10

10

Power Dissipation

10

33

Unit

V

V

mA

pF

V

µs

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

µs

ns

V

ms

mA

mA

µA

µA

mW

µW

Conditions/Comments

ISOURCE = ISINK = 200 µA.

IOL = 3 mA.

VOH = 5 V.

IOUT = 4 mA.

Fast Mode I2C. See Figure 2.

See Figure 2.

See Figure 2.

See Figure 2.

See Figure 2.

See Figure 3.

See Figure 3.

See Figure 3.

See Figure 3.

See Figure 3.

See Figure 3.

See Figure 3.

VDD settles to within 10% of its final voltage level.

VDD = 3.3 V, VIH = VDD, and VIL = GND.

VDD = 5 V, VIH = VDD, and VIL = GND.

VDD = 3.3 V, VIH = VDD, and VIL = GND.

VDD = 5 V, VIH = VDD, and VIL = GND.

VDD = 3.3 V. Normal mode.

VDD = 3.3 V. Shutdown mode.

1 See the Terminology section.

2 DC specifications are tested with the outputs unloaded.

3 Linearity is tested using a reduced code range: ADT7518 (Code 8 to 255).

4 Guaranteed by design and characterization, not production tested.

5 Round robin is the continuous sequential measurement of the following channels: VDD, internal temperature, external temperature (AIN1, AIN2), AIN3, and AIN4.

6 The temperature accuracy specifications are valid when the internal reference is not being used by the on-chip DAC. For new designs, the ADT7519 is recommended

as it does not have this limitation.

7 For the amplifier output to reach its minimum voltage, the offset error must be negative. For the amplifier output to reach its maximum voltage (VREF = VDD), the offset

plus gain error must be positive.

8 The SDA and SCL timing is measured with the input filters turned on to meet the fast-mode I2C specification. Switching off the input filters improves the transfer rate

but has a negative effect on the EMC behavior of the part.

9 Guaranteed by design, not production tested.

10 All input signals are specified with tr = tf = 5 ns (10% to 90% of VDD), and timed from a voltage level of 1.6 V.

11 Measured with the load circuit shown in Figure 4.

12 The IDD specification is valid for all DAC codes and full-scale analog input voltages. Interface inactive. All DACs and ADCs active. Load currents excluded.

Rev. A | Page 5 of 40

5 Page

DAC-to-DAC Crosstalk

This is the glitch impulse transferred to the output of one DAC

due to a digital code change and subsequent output change of

another DAC. This includes both digital and analog crosstalk. It

is measured by loading one of the DACs with a full-scale code

change (all 0s to all 1s and vice versa) with LDAC low and

monitoring the output of another DAC. The energy of the glitch

is expressed in nV-s.

Multiplying Bandwidth

The amplifiers within the DAC have a finite bandwidth. The

multiplying bandwidth is a measure of this. A sine wave on the

reference (with full-scale code loaded to the DAC) appears on

the output. The multiplying bandwidth is the frequency at

which the output amplitude falls to 3 dB below the input.

Total Harmonic Distortion

This is the difference between an ideal sine wave and its atten-

uated version using the DAC. The sine wave is used as the

reference for the DAC, and the THD is a measure of the

harmonics present on the DAC output, expressed in dB.

Round Robin

This term is used to describe the ADT7518 cycling through the

available measurement channels in sequence, taking a measure-

ment on each channel.

DAC Output Settling Time

This is the time required, following a prescribed data change, for

the output of a DAC to reach and remain within ±0.5 LSB of the

final value. A typical prescribed change is from 1/4 scale to

3/4 scale.

OUTPUT

VOLTAGE

ADT7518

GAIN ERROR

+

OFFSET ERROR

NEGATIVE

OFFSET

ERROR

DAC CODE

ACTUAL

IDEAL

AMPLIFIER

FOOTROOM

LOWER

DEADBAND

CODES

NEGATIVE

OFFSET

ERROR

Figure 8. DAC Transfer Function with Negative Offset

OUTPUT

VOLTAGE

GAIN ERROR

+

OFFSET ERROR

UPPER

DEADBAND

CODES

ACTUAL

IDEAL

POSITIVE

OFFSET

ERROR

DAC CODE

FULL SCALE

Figure 9. DAC Transfer Function with Positive Offset (VREF = VDD)

Rev. A | Page 11 of 40

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ADT7518.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADT7516 | SPI/I2C Compatible/ Temperature Sensor/ Four Channel ADC and Quad Voltage Output DAC | Analog Devices |

| ADT7517 | 4-Channel ADC and Quad Voltage Output | Analog Devices |

| ADT7517-KGD | SPI-/I2C-Compatible Temperature Sensor | Analog Devices |

| ADT7518 | 4-Channel ADC and Quad Voltage Output DAC | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |