|

|

PDF GAL20RA10B-30LJ Data sheet ( Hoja de datos )

| Número de pieza | GAL20RA10B-30LJ | |

| Descripción | High-Speed Asynchronous E2CMOS PLD Generic Array Logic | |

| Fabricantes | Lattice Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de GAL20RA10B-30LJ (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

GAL20RA10

High-Speed Asynchronous E2CMOS PLD

Generic Array Logic™

Features

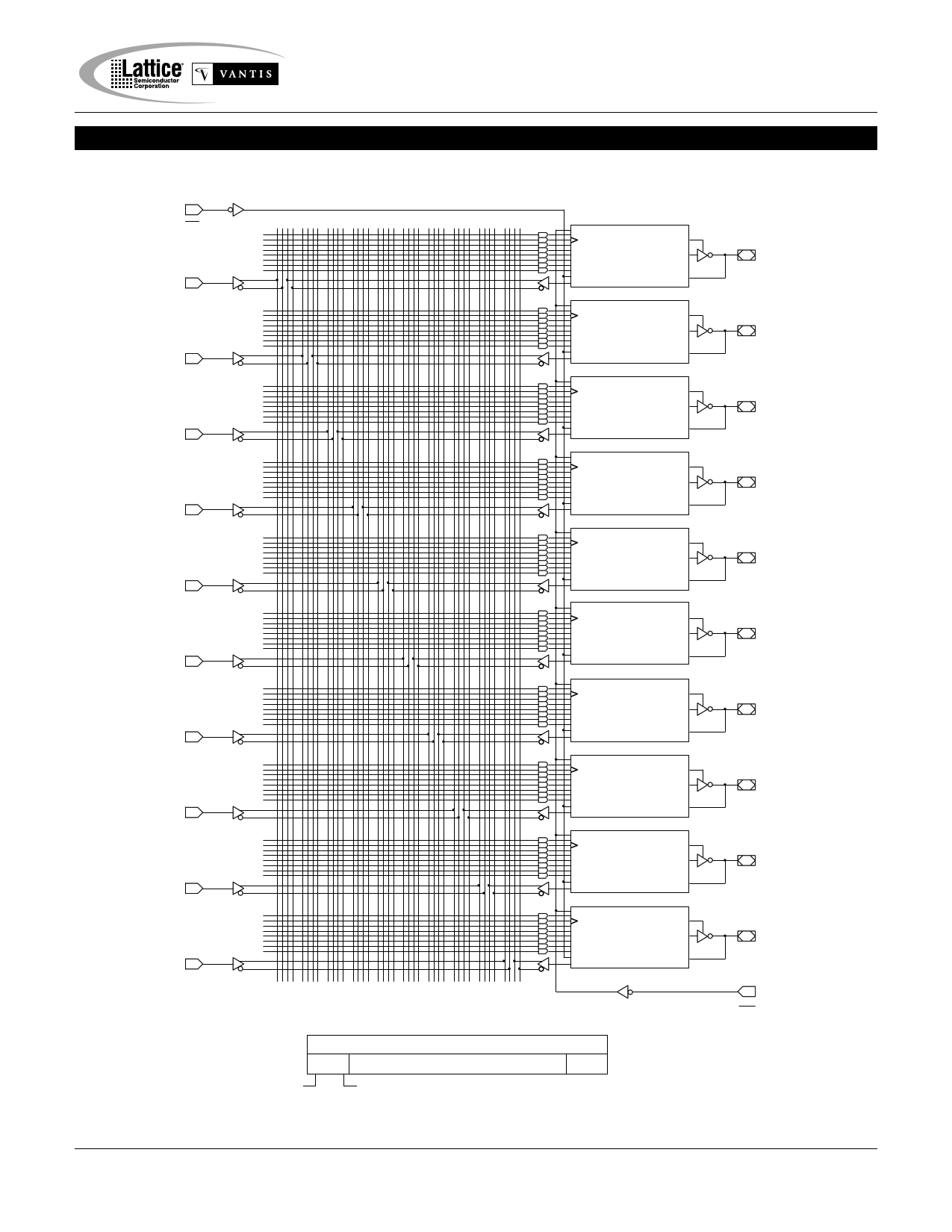

Functional Block Diagram

• HIGH PERFORMANCE E2CMOS ® TECHNOLOGY

— 7.5 ns Maximum Propagation Delay

— Fmax = 83.3 MHz

— 9 ns Maximum from Clock Input to Data Output

— TTL Compatible 8 mA Outputs

— UltraMOS® Advanced CMOS Technology

• 50% to 75% REDUCTION IN POWER FROM BIPOLAR

— 75mA Typical Icc

• ACTIVE PULL-UPS ON ALL PINS

• E2 CELL TECHNOLOGY

— Reconfigurable Logic

— Reprogrammable Cells

— 100% Tested/100% Yields

— High Speed Electrical Erasure (<100 ms)

— 20 Year Data Retention

• TEN OUTPUT LOGIC MACROCELLS

— Independent Programmable Clocks

— Independent Asynchronous Reset and Preset

— Registered or Combinatorial with Polarity

— Full Function and Parametric Compatibility with

PAL20RA10

• PRELOAD AND POWER-ON RESET OF ALL REGISTERS

— 100% Functional Testability

• APPLICATIONS INCLUDE:

— State Machine Control

— Standard Logic Consolidation

— Multiple Clock Logic Designs

• ELECTRONIC SIGNATURE FOR IDENTIFICATION

PL

I

I

I

I

I

I

I

I

I

I

8

OLMC

8

OLMC

8

OLMC

8

OLMC

8

OLMC

8

OLMC

8

OLMC

8

OLMC

8

OLMC

8

OLMC

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

Description

OE

The GAL20RA10 combines a high performance CMOS process

with electrically erasable (E2) floating gate technology to provide

the highest speed performance available in the PLD market. Lattice

Semiconductor’s E2CMOS circuitry achieves power levels as low

as 75mA typical I which represents a substantial savings in power

CC

when compared to bipolar counterparts. E2 technology offers high

speed (<100ms) erase times providing the ability to reprogram,

reconfigure or test the devices quickly and efficiently.

The generic architecture provides maximum design flexibility by

allowing the Output Logic Macrocell (OLMC) to be configured by

the user. The GAL20RA10 is a direct parametric compatible CMOS

replacement for the PAL20RA10 device.

Unique test circuitry and reprogrammable cells allow complete AC,

DC, and functional testing during manufacturing. Therefore, Lattice

Semiconductor delivers 100% field programmability and function-

ality of all GAL products. In addition, 100 erase/write cycles and

data retention in excess of 20 years are specified.

Pin Configuration

PLCC

4

I5

2 28 26

25

I

I7

23

NC GAL20RA10

I 9 Top View 21

I

I 11

19

12 14 16 18

I/O/Q

I/O/Q

I/O/Q

NC

I/O/Q

I/O/Q

I/O/Q

DIP

PL 1

I

24 Vcc

I/O/Q

I

I GAL

I 20RA10

I6

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I 18 I/O/Q

I I/O/Q

I I/O/Q

I I/O/Q

I I/O/Q

GND 12

13 OE

Copyright © 1997 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A.

Tel. (503) 681-0118; 1-888-ISP-PLDS; FAX (503) 681-3037; http://www.latticesemi.com

July 1997

20ra10_02

1

1 page

Specifications GAL20RA10

GAL20RA10 Logic Diagram

1 (2)

PL

DIP (PLCC) Package Pinouts

0 4 8 12 16 20 24 28 32 36

0

2 (3)

280

320

3 (4)

600

640

4 (5)

920

960

5 (6)

1240

1280

6 (7)

1560

1600

7 (9)

1880

1920

8 (10)

2200

2240

9 (11)

2520

2560

10 (12)

2840

2880

11 (13)

3160

OLMC

XOR - 3200

OLMC

XOR - 3201

OLMC

XOR - 3202

OLMC

XOR - 3203

OLMC

XOR - 3204

OLMC

XOR - 3205

OLMC

XOR - 3206

OLMC

XOR - 3207

OLMC

XOR - 3208

OLMC

XOR - 3209

64-USER ELECTRONIC SIGNATURE FUSES

3210, 3211, ....

.... 3272, 3273

Byte7 Byte6 ....

.... Byte1 Byte0

MSB

LSB

23 (27)

22 (26)

21 (25)

20 (24)

19 (23)

18 (21)

17 (20)

16 (19)

15 (18)

14 (17)

13 (16)

OE

5

5 Page

Power-Up Reset

Specifications GAL20RA10

Vcc (min.)

Vcc

CLK

INTERNAL REGISTER

Q - OUTPUT

tpr

tsu

t wl

Internal Register

Reset to Logic "0"

FEEDBACK/EXTERNAL

OUTPUT REGISTER

Device Pin

Reset to Logic "1"

Circuitry within the GAL20RA10 provides a reset signal to all reg-

isters during power-up. All internal registers will have their Q

outputs set low after a specified time (tpr, 1µs MAX). As a result,

the state on the registered output pins (if they are enabled) will

be high on power-up, because of the inverting buffer on the output

pins. This feature can greatly simplify state machine design by

providing a known state on power-up. The timing diagram for

power-up is shown to the right. Because of the asynchronous

nature of system power-up, some conditions must be met to

provide a valid power-up reset of the GAL20RA10. First, the Vcc

rise must be monotonic. Second, the clock input must be at a static

TTL level as shown in the diagram during power up. The regis-

ters will reset within a maximum of 1µs. As in normal system op-

eration, avoid clocking the device until all input and feedback path

setup times have been met. The clock must also meet the mini-

mum pulse width requirements.

Input/Output Equivalent Schematics

PIN

(Vref Typical = 3.2V)

Active Pull-up

Circuit

Vcc

Vcc Vref Vcc

ESD

Protection

Circuit

PIN

ESD

Protection

Circuit

Typical Input

PIN

Feedback

Tri-State

Control

Active Pull-up

Circuit

Vcc Vref

(Vref Typical = 3.2V)

Data

Output

PIN

Feedback

(To Input Buffer)

Typical Output

11

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet GAL20RA10B-30LJ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GAL20RA10B-30LJ | High-Speed Asynchronous E2CMOS PLD Generic Array Logic | Lattice Semiconductor |

| GAL20RA10B-30LP | High-Speed Asynchronous E2CMOS PLD Generic Array Logic | Lattice Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |