|

|

PDF NL256204AM15-01A Data sheet ( Hoja de datos )

| Número de pieza | NL256204AM15-01A | |

| Descripción | TFT MONOCHROME LCD MODULE | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NL256204AM15-01A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Global LCD Panel Exchange Center

www.panelook.com

TFT MONOCHROME LCD MODULE

NL256204AM15-01

NL256204AM15-01A

51cm (20.1 Type)

QSXGA

LVDS Interface (4 ports)

DATA SHEET

DOD-PD-0887 (4th edition)

This DATA SHEET is updated document from

DOD-PD-0561(3).

All information is subject to change without notice.

Please confirm the sales representative before

starting to design your system.

Document Number: DOD-PD-0887 (4th edition)

Published date: March 2005 CP(N)

1 ¤ NEC LCD Technologies, Ltd.

2003- 2005 All rights reserved.

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

1 page

Global LCD Panel Exchange Center

www.panelook.com

NL256204AM15-01/01A

2. GENERAL SPECIFICATIONS

Display area

399.36 (H) u 319.488 (V) mm

Diagonal size of display

51 cm (20.1 inches)

Drive system

a-Si TFT active matrix

Display gray scale

256 gray scales per 1 sub-pixel (8-bit) (766 gray scales per 1 pixel)

Pixel

2,560 (H) u 2,048 (V) pixels (1 pixel consists of 3 sub pixels (LCR))

Pixel arrangement

LCR Vertical stripe

Sub-pixel pitch

0.052 (H) u 0.156 (V) mm

Pixel pitch

0.156 (H) u 0.156 (V) mm

Module size

423.4 (W) u 343.5 (H) u 43.5 (D) mm (typ.)

Weight

2,440 g (typ.)

Contrast ratio

600:1 (typ.)

Viewing angle

At the contrast ratio t10:1

x Horizontal: Right side 85q (typ.), Left side 85q (typ.)

x Vertical: Up side 85q (typ.), Down side 85q (typ.)

Designed viewing direction Viewing angle with optimum grayscale (J=DICOM): normal axis Note1

Polarizer surface

Antiglare

Polarizer pencil-hardness

Response time

Luminance

White chromaticity

2H (min.) [by JIS K5400]

Ton + Toff (10%mo 90%)

30 ms (typ.)

At the maximum luminance control

850 cd/m2 (typ.)

NL256204AM15-01

Wx, Wy = (0.255, 0.310) (typ.)

NL256204AM15-01A

Wx, Wy = (0.280, 0.304) (typ.)

Signal system

4 ports LVDS interface

LCR 8-bit signals, Data enable signal (DE), Dot clock (CLK)

Power supply voltage

LCD panel signal processing board: 12.0V

Inverter: 12.0V

Direct light type: 12 cold cathode fluorescent lamps with an inverter

Backlight

NL256204AM15-01

Replaceable parts

x Backlight unit: Type No.: 201LHS07

x Inverter:

Type No.: 201PW121

NL256204AM15-01A

Replaceable parts

x Backlight unit: Type No.: 201LHS08

x Inverter:

Type No.: 201PW121

Power consumption

At checkered flag pattern and the maximum luminance control

49.2 W (typ.)

Note1: When the product luminance is 850cd/m2, the gamma characteristic is designed to J=DICOM.

DATA SHEET DOD-PD-0887 (4th edition)

5

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

5 Page

Global LCD Panel Exchange Center

www.panelook.com

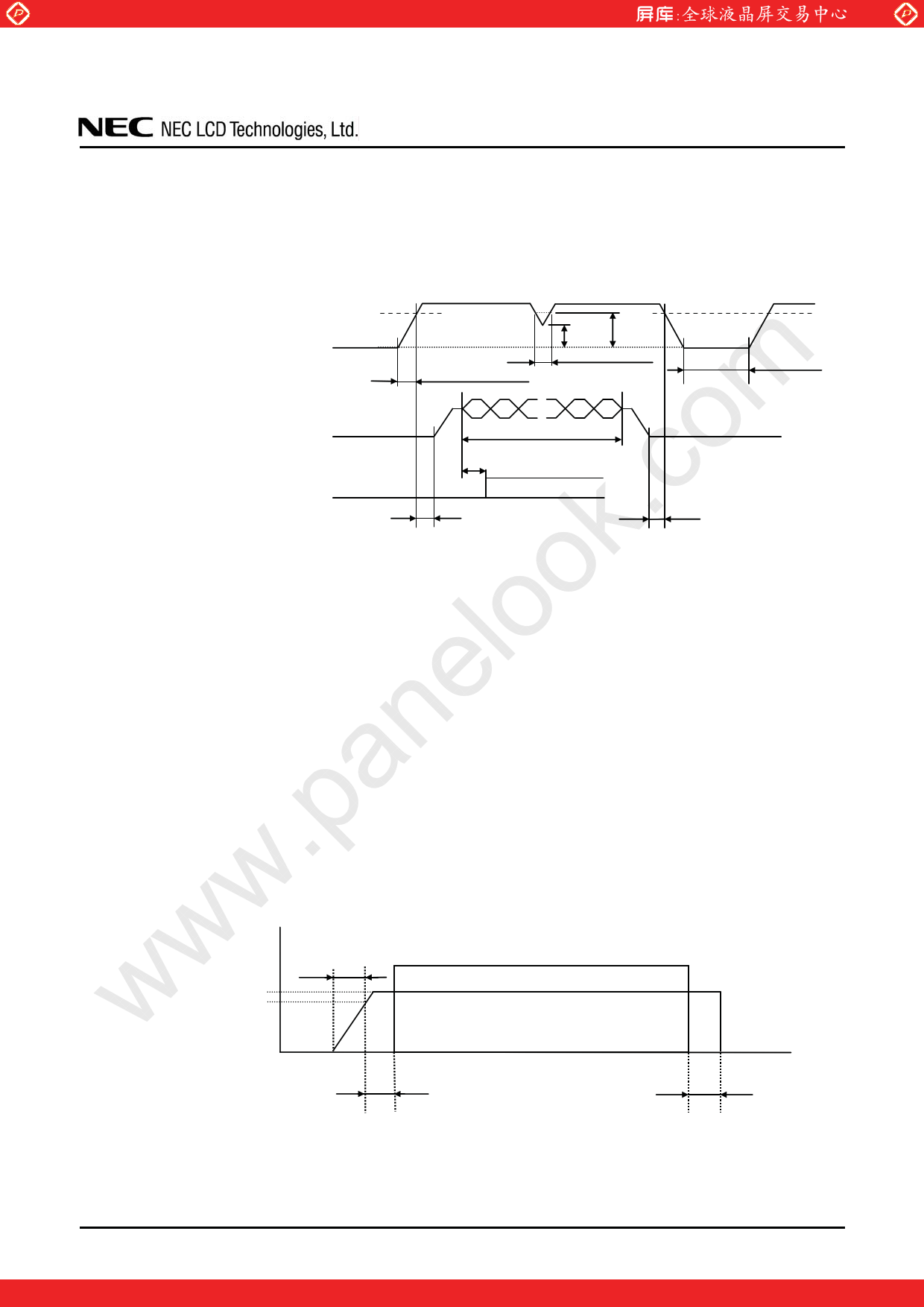

4.4 POWER SUPPLY VOLTAGE SEQUENCE

4.4.1 LCD panel signal processing board

NL256204AM15-01/01A

VDD ON

VDD OFF

VDD

Note1, Note2

10.8V

0V

5ms < Tr < 80ms

9.6V 10.8V

VDD dip < 20ms

LVDS Signals *1,*2

Note3

0V

CSR, CSL, SCLK, SDAT

Note3

0V

VALID period

tt20ms Note4

VALID period

10ms < t < 35ms

0ms < t < 35ms

VDD ON

10.8V

Toff > 50ms

*1: DA0+/-, DA1+/-, DA2+/-, DA3+/-, CKA+/-, DB0+/-, DB1+/-, DB2+/-, DB3+/-, CKB+/-,

DC0+/-, DC1+/-, DC2+/-, DC3+/-, CKC+/-, DD0+/-, DD1+/-, DD2+/-, DD3+/-, CKD+/-

*2: LVDS signals should be measured at the terminal of 100: resistance.

Note1: In terms of voltage variation (voltage drop) while VDD rising edge is below 10.8V, a protection

circuit may work, and then this product may not work.

Note2: VDD should be 10.8V or more during VDD ON period.

Note3: LVDS signals and CSR, CSL, SCLK, SDAT must be Low or High-impedance, exclude the

VALID period (See above sequence diagram), in order to avoid that internal circuits is

damaged.

If some of signals are cut while this product is working, even if the signal input to it once again,

it might not work normally. If customer stops the display and function signals, they should be

cut VDD.

Note4: At the beginning of the serial communication mode, take 20ms or more after the LVDS signal

input.

4.4.2 Inverter

Voltage

12.0V

11.4V

td800ms

BRTC

VDDB

Time

0<t 0<t

Note1: The inverter power supply voltage (VDDB) should be inputted within the valid period of LVDS

signals, in order to avoid unstable data display.

Note2: If tr is more than 800ms, the backlight will be turned off by a protection circuit for inverter.

Note3: When VDDB is 0V or BRTC is Low, PWSEL must be set to Low or Open.

DATA SHEET DOD-PD-0887 (4th edition)

11

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory! www.panelook.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet NL256204AM15-01A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NL256204AM15-01 | TFT COLOR LCD MODULE | NEC |

| NL256204AM15-01A | TFT MONOCHROME LCD MODULE | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |