|

|

PDF GDC21D401B Data sheet ( Hoja de datos )

| Número de pieza | GDC21D401B | |

| Descripción | Video Decoder | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de GDC21D401B (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

GDC21D401B

(Video Decoder)

Version 1.0

Mar, 99

HDS-GDC21D401B-9908 / 10

1 page

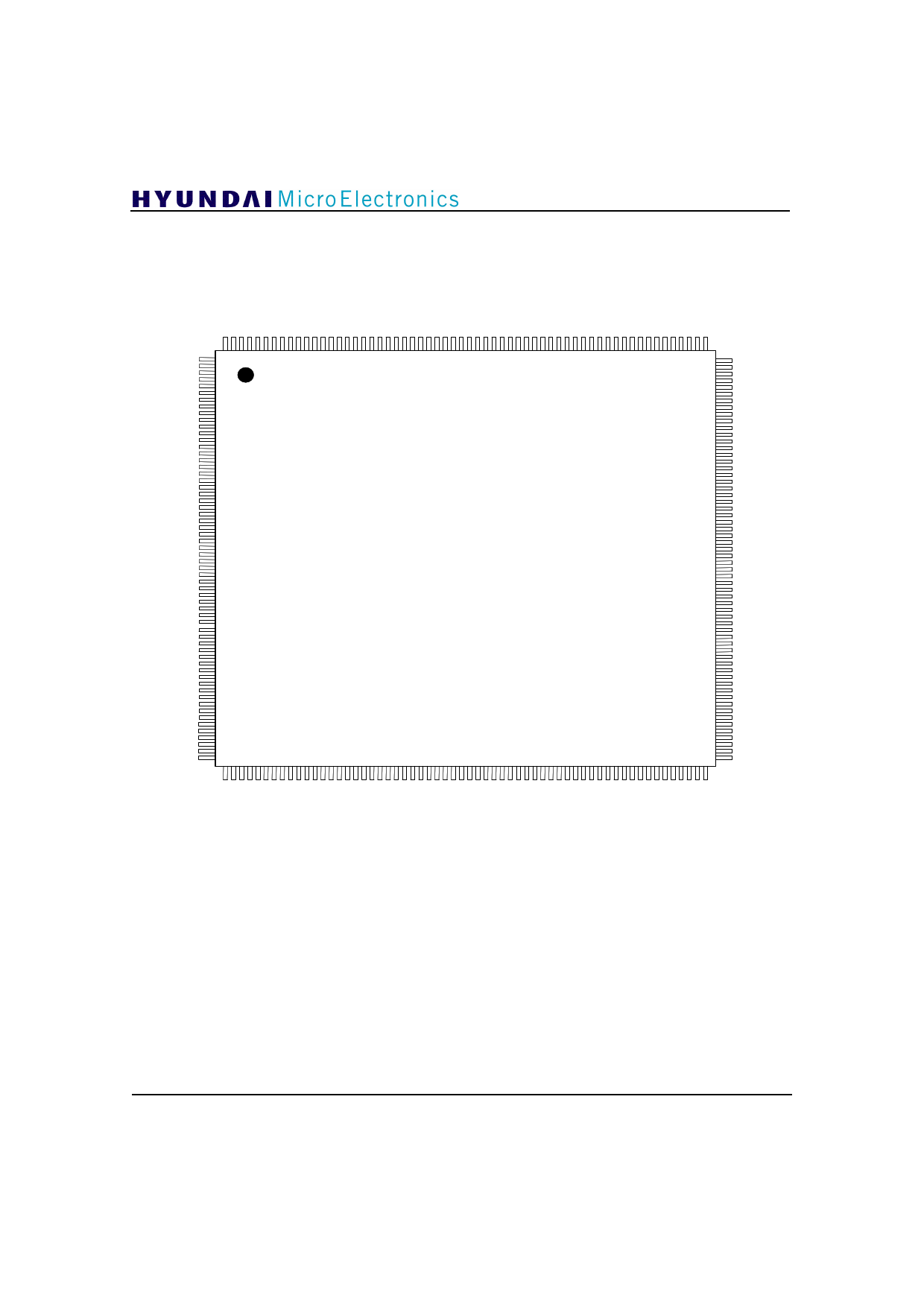

3. Pin Description

GDC21D401B

VSS

SCANTESTON

VDD

IDCTTESTON

MEMTESTON

CLK_27M

VSS

\RESET

TSW

\VIDEN

VSTCW

VSS

VID_STRB

VID_DATA[0]

VID_DATA[1]

VID_DATA[2]

VDD

VID_DATA[3]

VSS

VID_DATA[4]

VID_DATA[5]

VDD

VID_DATA[6]

VSS

VID_DATA[7]

SCL

VSS

SDA

\VID_REQ

\UBUFF_FULL

\INT_V

VDD

SDRAM_DATA[0]

SDRAM_DATA[1]

VSS

SDRAM_DATA[2]

VDD

SDRAM_DATA[3]

SDRAM_DATA[4]

SDRAM_DATA[5]

VDD

SDRAM_DATA[6]

SDRAM_DATA[7]

VDD

SDRAM_DATA[8]

VSS

SDRAM_DATA[9]

SDRAM_DATA[10]

VDD

SDRAM_DATA[11]

SDRAM_DATA[12]

VSS

SDRAM_DATA[13]

SDRAM_DATA[14]

VDD

SDRAM_DATA[15]

SDRAM_DATA[16]

VSS

SDRAM_DATA[17]

SDRAM_DATA[18]

1 240

5

10

15

20

25

30

35

40

45

50

55

60

HME

GDC21D401B

YYWWA

Figure 1. Pin Description

180

175

170

165

160

155

150

145

140

135

130

125

VSS

PSTR[1]

PSTR[0]

PDWIN

VSS

D_INFO_WIN

DIS_INFO

VDD

VDD

\FFPN

VSS

MBFI

MBCLK

VDD

SCLK

VDCLK

VSS

SDRAM_DATA[63]

SDRAM_DATA[62]

SDRAM_DATA[61]

VDD

VDD

SDRAM_DATA[60]

SDRAM_DATA[59]

VSS

VSS

SDRAM_DATA[58]

VDD

SDRAM_DATA[57]

VSS

SDRAM_DATA[56]

VDD

SDRAM_DATA[55]

SDRAM_DATA[54]

VSS

SDRAM_DATA[53]

SDRAM_DATA[52]

VDD

SDRAM_DATA[51]

SDRAM_DATA[50]

VSS

SDRAM_DATA[49]

SDRAM_DATA[48]

VDD

SDRAM_DATA[47]

VDD

SDRAM_DATA[46]

SDRAM_DATA[45]

VSS

VSS

SDRAM_DATA[44]

VDD

SDRAM_DATA[43]

VDD

SDRAM_DATA[42]

SDRAM_DATA[41]

VSS

SDRAM_DATA[40]

VSS

SDRAM_DATA[39]

6

5 Page

5.3 STC (System Time Clock)

Generation

Internal STC counter is supported. STC value

should be loaded after the reset by host

microprocessor or transport decoder, and be

counted at 90 KHz clock derived from external 27

MHz system clock. Also it should be loaded

whenever the system time base is changed. 27

MHz system clock is supplied by transport

decoder through external 27 MHz clock input.

5.4 DTS (Decoding Time Stamp)

Synchronization

The DTS values are determined when the

associated pictures are decoded referring to the

STC. The transport decoder must extract PTS &

DTS values from MPEG-2 system layer, and

transfer them to the VD through host interface or

transport data interface. DTS values are extracted

and stored in DTS-FIFO with 8-bit associated

picture numbers(they are defined by the VD

internally).

Before each picture decoding, picture decoding

controller checks if there is a DTS associated with

each picture. And it compares the DTS value from

DTS-FIFO with STC value.

The DTS value is considered to match the current

STC value if the DTS satisfies this equation:

STC + jitter_b(negative) < DTS < STC + jitter_f(positive)

In the case that jitter is the tolerance for the

comparison:

If the DTS is less than STC + jitter_b (in

other words, the time for current picture

decoding has already passed), picture

decoding controller discards B picture in

VBV delay mode and any picture in low

delay mode without decoding it.

If the DTS is greater than STC + jitter_f (the

time for current picture decoding has not

come yet), picture decoding controller pauses

decoding process until the DTS value falls

within the allowed tolerance of STC.

GDC21D401B

When system time base is changed, the time base

of the current DTS can differ from that of the new

STC temporarily because of video decoding delay.

In this case, for about 0.5 sec, DTS

synchronization mode must be disabled by using

decoding mode register.

5.5 Error Concealment

When the VLD detects a bitstream syntax error or

an MPEG-2 error code (0x000001B4), it performs

appropriate error handling and error concealment

to continue the decoding and to minimize the

effect of the error on decoded video. If an error

occurs at picture data layer, the slice-based error

concealment is performed. If an error occurs at

header layer, the associated sequence is skipped.

5.6 User Data Read

User data in MPEG Video Sequence can be read

through host interface(I2C) as follows. If user data

interrupt is enabled, user data is stored in internal

user data FIFO, and once ‘PIC_DEC_SYNC’ is

set to ‘high’, a interrupt signal is generated which

informs host that user data is stored in user data

FIFO. If user data interrupt is disabled, user data

is discarded.

When user data interrupt signal is generated, host

reads the ‘U_D_COUNT’ register for bytes of

user data FIFO. And then it reads the

‘USER_DATA’ register(user data FIFO output)

repeatedly as many as the number of

‘U_D_COUNT’ register. In this case, the host

had better use I2C burst read cycle for reading

speed efficiency.

If internal user data FIFO becomes full during user

data interrupts, ‘\UBUFF_FULL’ signal is

generated. And also the host reads user data by

using the same method as that of user data

interrupt.

12

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet GDC21D401B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GDC21D401B | Video Decoder | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |