|

|

PDF FX604 Data sheet ( Hoja de datos )

| Número de pieza | FX604 | |

| Descripción | V23 Compatible Modem | |

| Fabricantes | CML Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de FX604 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

CML Semiconductor Products

V23 Compatible Modem FX604

1.0 Features

D/604/3 November 1996

Provisional Information

• 1200/75 bits/sec Full Duplex V23 compatible Modem with:

• Optional 75bits/sec Back Channel • Optional Line Equalisation

• Optional 1200bits/sec Data

Retiming Facility

• -40°C to +85°C Operating

Temperature

• 3.58MHz Xtal/Clock Rate

• 16-pin SOIC and DIP Packages

• 3.0 to 5.5V Supply; 1.0mA typ. at 3V • Conforms to relevant sections of

'Zero-Power' Mode; 1µA typ.

V23 and ETSI specifications

1.1 Brief Description

The FX604 is a low power CMOS integrated circuit for the reception or transmission of asynchronous

1200bits/sec data in accordance with CCITT V.23 and ETSI specifications. It is also capable of generating the

75bits/sec 'back channel'.

The device incorporates an optional Tx and Rx data retiming function that removes the need for a UART in the

associated µC when operating at 1200bits/sec. The device can disable the back channel or be operated so

only the mark or space tone is produced. An optional line equaliser is incorporated into the receive path, this is

controlled by an external logic level.

The FX604 may be used in a wide range of telephone telemetry systems. With a low voltage requirement of

3.0V it is suitable for both portable terminal and line powered applications. A very low current 'sleep' mode (1µ

A typ.) and operating current of 1mA typ. mean the device is ideal for line powered applications. A 3.58MHz

standard Xtal/Clock rate is required and the device operates from a 3.0 to 5.5V supply. Both SOIC (D4) and

Plastic DIL (P3) 16-pin package types are available.

© 1996 Consumer Microcircuits Limited

1 page

V.23 Compatible Modem

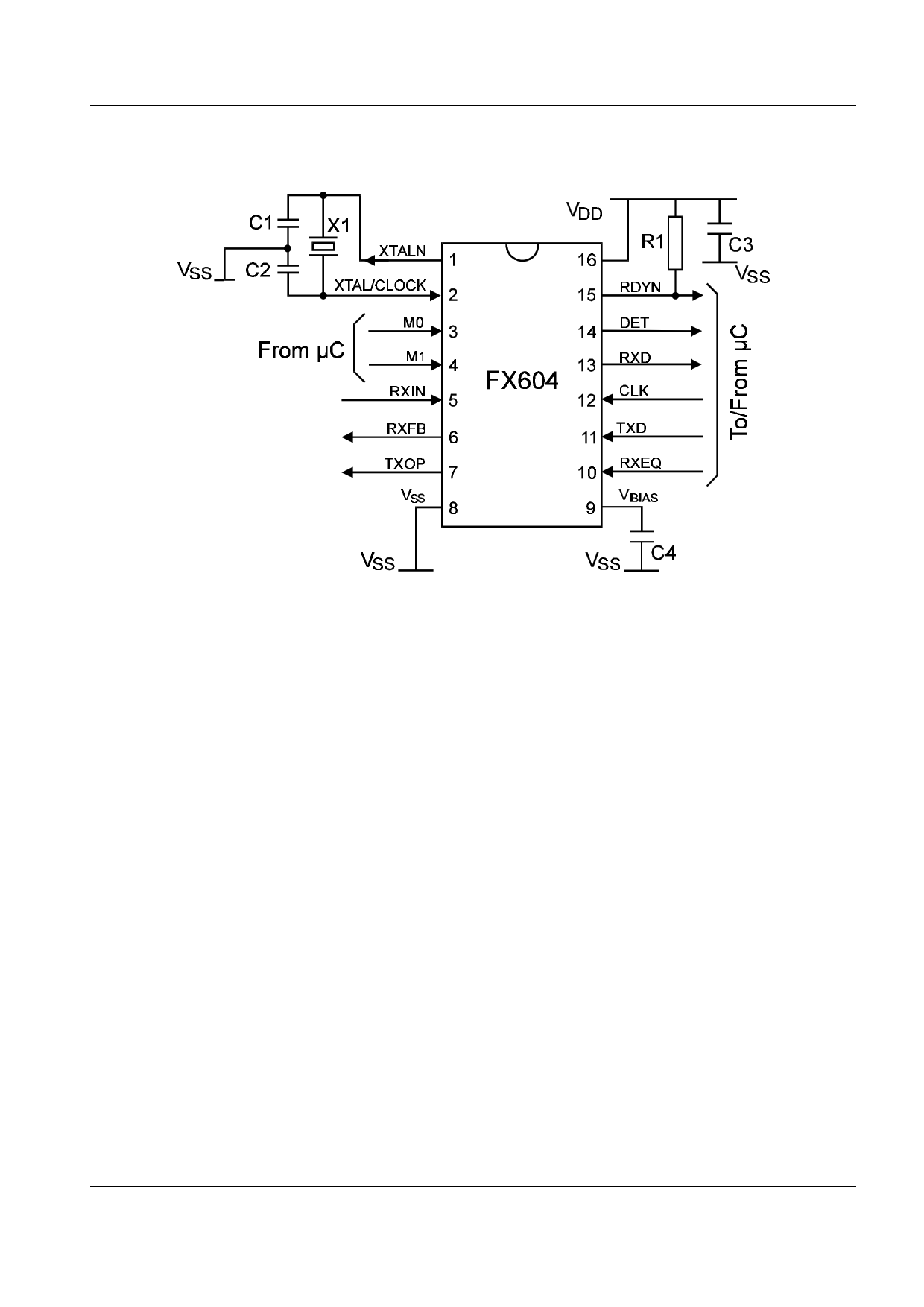

1.4 External Components

FX604

R1 100kΩ

X1 3.579545MHz

C1, C2

C3

C4

18pF

0.1µF

0.1µF

Resistors ±5%, capacitors ±10% unless otherwise stated.

Figure 2 Recommended External Components for Typical Application

1.5 General Description

1.5.1 Xtal Osc and Clock Dividers

Frequency and timing accuracy of the FX604 is determined by a 3.579545MHz clock present at the

XTAL/CLOCK pin. This may be generated by the on-chip oscillator inverter using the external components C1,

C2 and X1 of Figure 2, or may be supplied from an external source to the XTAL/CLOCK input. If supplied from

an external source, C1, C2 and X1 should not be fitted.

The on-chip oscillator is turned off in the 'Zero-Power' mode.

If the clock is provided by an external source which is not always running, then the 'Zero-Power' mode must be

set when the clock is not available. Failure to observe this rule may cause a significant rise in the supply

current drawn by FX604 as well as generating undefined states of the RXD, DET and RDYN outputs.

© 1996 Consumer Microcircuits Limited

5

D/604/3

5 Page

V.23 Compatible Modem

FX604

So to use the retiming option the CLK input should be held low until the RDYN output is pulled low. When the

RDYN pin goes low the next data bit should be applied at the TXD input and the CLK input pulled high and

then low within the time limits set out in Figure 6c.

Td = Internal FX604 delay; max 1µs

Tr = RDYN low to CLK going low; max 800µs

Tchi = CLK high time; min 1µs

Ts = data set up time; min 1µs

Th = data hold time; min 1µs

Figure 6c FSK Operation with Tx Data Retiming

To ensure synchronisation between the controlling device and the FX604 when entering Tx retiming mode the

TXD pin must be held at a constant logic level from when the CLK pin is first pulled low to the end of loading in

the second retimed bit. Similarly when exiting Tx retiming mode the TXD pin should be held at the same logic

level as the last retimed bit for at least 2 bit times after the CLK line is pulled high.

If the data retiming facility is not required, the CLK input to the FX604 should be kept high at all times. The

asynchronous data to the FSK modulator will then be connected directly to the TXD input pin. This is

illustrated in Figure 6d and will also be the case when transmitting 75bits/sec data which has no retime option.

Figure 6d FSK Operation without Tx Data Retiming (CLK always high)

© 1996 Consumer Microcircuits Limited

11

D/604/3

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet FX604.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FX601 | Ultrahigh-Speed Switching Applications | Sanyo Semicon Device |

| FX602 | Ultrahigh-Speed Switching Applications | Sanyo Semicon Device |

| FX603 | Ultrahigh-Speed Switching Applications | Sanyo Semicon Device |

| FX604 | Ultrahigh-Speed Switching Applications | Sanyo Semicon Device |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |