|

|

PDF M2N2G64TU8HG4B Data sheet ( Hoja de datos )

| Número de pieza | M2N2G64TU8HG4B | |

| Descripción | Unbuffered DDR2 SO-DIMM | |

| Fabricantes | Nanya | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de M2N2G64TU8HG4B (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

M2N1G64TUH8G5F / M2S1G64TUH8G4F / M2N2G64TU8HG5B / M2N2G64TU8HG4B

1GB: 128M x 64 / 2GB: 256M x 64

PC2-5300 / PC2-6400

Unbuffered DDR2 SO-DIMM

Based on DDR2-667/800 64Mx16 (1GB)/128Mx8 (2GB) SDRAM G-Die

Features

• Performance:

Speed Sort

PC2-5300 PC2-6400

-3C -AC Unit

DIMM CAS Latency

5

5

fck – Clock Freqency

333

400 MHz

tck – Clock Cycle 3 2.5 ns

Data Transfer Speed

667

800 Mbps

• 200-Pin Small Outline Dual In-Line Memory Module (SO-DIMM)

• 1GB: 128Mx64 Unbuffered DDR2 SO-DIMM based on 64M x16

DDR2 SDRAM G-Die devices.

• 2GB: 256Mx64 Unbuffered DDR2 SO-DIMM based on 128M x8

DDR2 SDRAM G-Die devices.

• Intended for 333MHz and 400MHz applications

• Inputs and outputs are SSTL-18 compatible

• VDD = VDDQ = 1.8V ±0.1V

• SDRAMs have 8 internal banks for concurrent operation

• Differential clock inputs

• Data is read or written on both clock edges

• DRAM DLL aligns DQ and DQS transitions with clock transitions.

• Address and control signals are fully synchronous to positive

clock edge

• Auto Refresh (CBR) and Self Refresh Modes

• Automatic and controlled precharge commands

• Programmable Operation:

- DIMM Latency: 3, 4, 5

- Burst Type: Sequential or Interleave

- Burst Length: 4, 8

- Operation: Burst Read and Write

• 13/10/2 Addressing (1GB)

• 14/10/2 Addressing (2GB)

• 7.8 s Max. Average Periodic Refresh Interval

• Serial Presence Detect

• Gold contacts

• 1GB module’s SDRAMs are 84-ball BGA Package

• 2GB module’s SDRAMs are 60-ball BGA Package

• RoHS compliance

Description

M2N1G64TUH8G5F / M2S1G64TUH8G4F / M2N2G64TU8HG5B / M2N2G64TU8HG4B are unbuffered 200-Pin Double Data Rate 2

(DDR2) Synchronous DRAM Small Outline Dual In-Line Memory Module (SO-DIMM), organized as two ranks of 128Mx64 (1GB)/256Mx64

(2GB) high-speed memory array. M2N1G64TUH8G5F / M2S1G64TUH8G4F uses eight 64Mx16 84-ball BGA packaged devices and

M2N2G64TU8HG5B / M2N2G64TU8HG4B uses sixteen 128Mx8 60-ball BGA packaged devices. These DIMMs are manufactured using

raw cards developed for broad industry use as reference designs. The use of these common design files minimizes electrical variation

between suppliers. All Elixir DDR2 SODIMMs provide a high-performance, flexible 8-byte interface in a space-saving footprint.

The DIMM is intended for use in applications operating of 333MHz/400MHz clock speeds and achieves high-speed data transfer speed of

667Mbps/800Mbps. Prior to any access operation, the device latency and burst/length/operation type must be programmed into the

DIMM by address inputs A0-A12 (1GB) / A0-A13 (2GB) and I/O inputs BA0, BA1 and BA2 using the mode register set cycle.

The DIMM uses serial presence-detect implemented via a serial EEPROM using a standard IIC protocol. The first 128 bytes of SPD data are

programmed and locked during module assembly. The remaining 128 bytes are available for use by the customer.

REV 1.0

07/2010

1

© NANYA TECHNOLOGY CORPORATION

NANYA reserves the right to change products and specifications without notice.

1 page

M2N1G64TUH8G5F / M2S1G64TUH8G4F / M2N2G64TU8HG5B / M2N2G64TU8HG4B

1GB: 128M x 64 / 2GB: 256M x 64

PC2-5300 / PC2-6400

Unbuffered DDR2 SO-DIMM

Functional Block Diagram

[1GB – 2 Ranks, 64Mx16 DDR2 SDRAMs]

3 Ohms +/- 5%

ODT1

ODT0

CKE1

CKE0

DQS0

DM0

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQS1

DM1

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

LDQS

LDM

C

K

E

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D0

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

O

D

T

C

LDQS

LDM

K

E

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D4

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

O

D

T

DQS4

DM4

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQS5

DM5

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

LDQS

LDM

C

K

E

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D2

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

O

D

T

C

LDQS

LDM

K

E

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D6

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

O

D

T

DQS2

DM2

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQS3

DM3

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

LDQS

LDM

C

K

E

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D1

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

O

D

T

C

LDQS

LDM

K

E

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D5

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

O

D

T

DQS6

DM6

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQS7

DM7

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

LDQS

LDM

C

K

E

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D3

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

O

D

T

C

LDQS

LDM

K

E

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D7

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

O

D

T

BA0- BA2

A0- A 12

SDRAMS D0-D7

SDRAMS D0-D7

SDRAMS D0-D7

SDRAMS D0-D7

SDRAMS D0-D7

V DDSPD

VDD

VREF

VSS

VDDID

SPD

D0-D7, VDD and VDDQ

D0-D7

D0-D7, SPD

CK0

CK1

4 loads

4 loads

Notes:

1. DQ wiring may differ from that described in this drawing.

2. DQ/DQS/DM/CKE/S S relationships are maintained as shown.

3. DQ/DQS/DM/DQS resistors are 22 +/- 5% Ohms

4. VDDID strap connections (for memory device VDD,VDDQ):

STRAP OUT (OPEN): VDD = VDDQ

STRAP IN (VSS ): VDD is not equal to VDDQ

REV 1.0

07/2010

5

SCL

SA0

SA1

WP

Serial PD

A0 A1

SA0 SA1

A2

SDA

© NANYA TECHNOLOGY CORPORATION

NANYA reserves the right to change products and specifications without notice.

5 Page

M2N1G64TUH8G5F / M2S1G64TUH8G4F / M2N2G64TU8HG5B / M2N2G64TU8HG4B

1GB: 128M x 64 / 2GB: 256M x 64

PC2-5300 / PC2-6400

Unbuffered DDR2 SO-DIMM

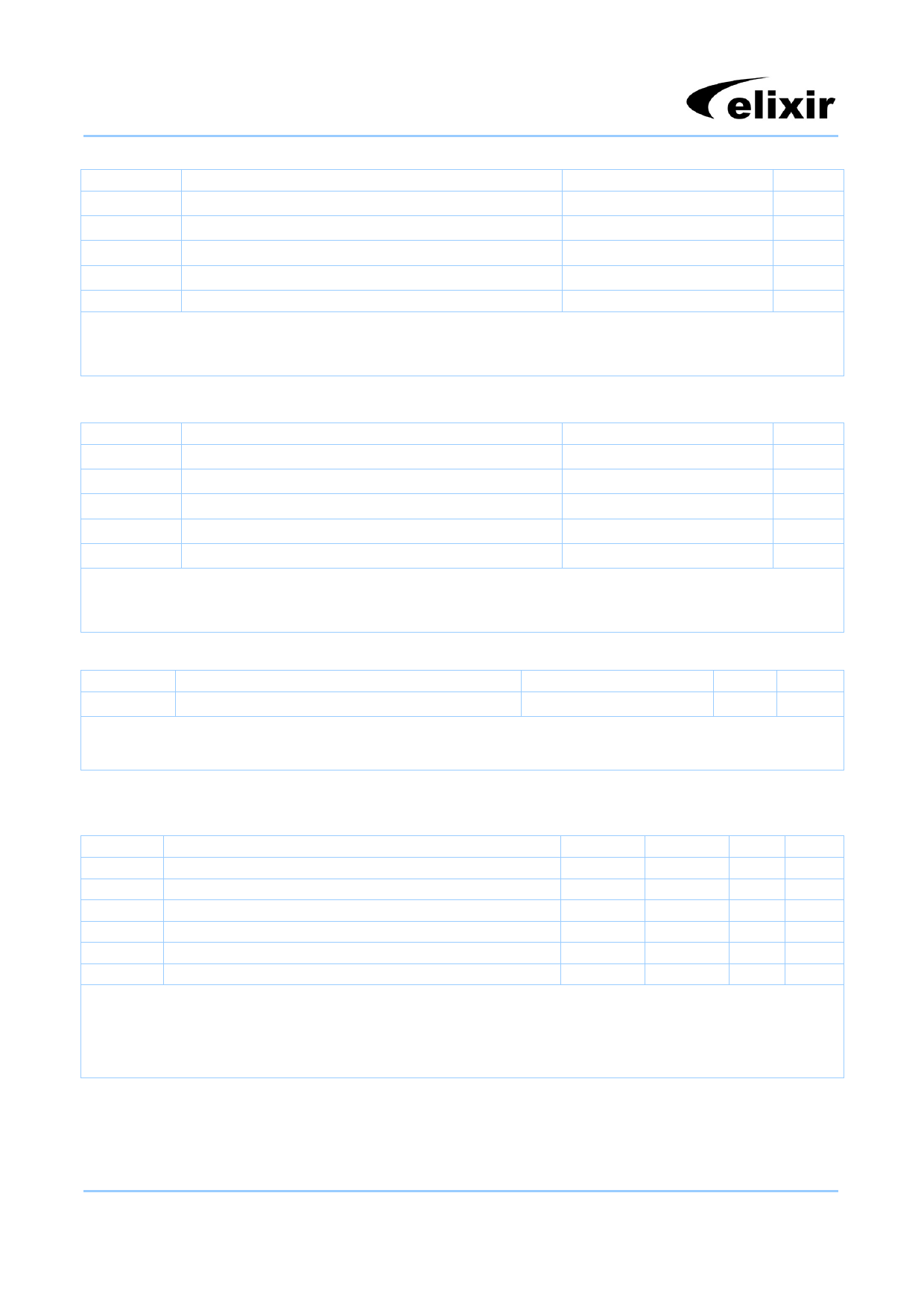

Environmental Requirements

Symbol

Parameter

Rating

Units

TOPR

HOPR

TSTG

HSTG

Operating Temperature (ambient)

Operating Humidity (relative)

Storage Temperature

Storage Humidity (without condensation)

Barometric pressure (operating & storage) up to 9850ft.

0 to 65

10 to 90

-50 to 100

5 to 95

105 to 69

°C

%

°C

%

kPa

Note: Stress greater than those listed may cause permanent damage to the device. This is a stress rating only and device functional

operation at or above the conditions indicated is not implied. Exposure to absolute maximum rating conditions for extended periods may

affect reliability

Absolute Maximum DC Ratings

Symbol

Parameter

Rating

Units

VDD Voltage on VDD pins relative to Vss

-1.0 to +2.3

V

VDDQ

Voltage on VDDQ pins relative to Vss

-0.5 to +2.3

V

VDDL

Voltage on VDDL pins relative to Vss

-0.5 to +2.3

V

VIN, VOUT Voltage on I/O pins relative to Vss

-0.5 to +2.3

V

TSTG

Storage Temperature (Plastic)

-55 to +100

°C

Note: Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is stress

rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

Storage temperature is the case surface temperature on the center/top side of the DRAM.

Operating temperature Conditions

Symbol

Parameter

TCASE

Operating Temperature (Ambient)

Note:

1.

2.

Case temperature is measured at top and center side of any DRAMs.

tCASE > 85°C tREFI = 3.9 μs

Rating

0 to 95

Units

°C

Note

1

DC Electrical Characteristics and Operating Conditions

Symbol

Parameter

Min

Max

Units Notes

VDD Supply Voltage

1.7 1.9 V 1

VDDL DLL Supply Voltage

1.7 1.9 V 1

VDDQ Output Supply Voltage

1.7 1.9 V 1

VSS, VSSQ Supply Voltage, I/O Supply Voltage

0 0V

VREF

VTT

Input Reference Voltage

Termination Voltage

0.49VDDQ 0.51VDDQ

VREF – 0.04 VREF + 0.04

V

V

1, 2

3

Note:

1. There is no specific device VDD supply voltage requirement for SSTL_18 compliance. However, VDDQ must be less than or equal to

VDD under all conditions.

2. VREF is expected to be equal to 0.5 V DDQ of the transmitting device, and to track variations in the DC level of the same. Peak-to-peak

noise on VREF may not exceed 2% of the DC value.

3. VTT of transmitting device must track VREF of receiving device.

REV 1.0

07/2010

11

© NANYA TECHNOLOGY CORPORATION

NANYA reserves the right to change products and specifications without notice.

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet M2N2G64TU8HG4B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M2N2G64TU8HG4B | Unbuffered DDR2 SO-DIMM | Nanya |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |