|

|

PDF H5MS2562JFR-L3M Data sheet ( Hoja de datos )

| Número de pieza | H5MS2562JFR-L3M | |

| Descripción | Mobile DDR SDRAM 256Mbit (16M x 16bit) | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de H5MS2562JFR-L3M (archivo pdf) en la parte inferior de esta página. Total 62 Páginas | ||

|

No Preview Available !

256Mbit MOBILE DDR SDRAM based on 4M x 4Bank x16 I/O

Specification of

256Mb (16Mx16bit) Mobile DDR SDRAM

Memory Cell Array

- Organized as 4banks of 4,194,304 x16

This document is a general product description and is subject to change without notice. Hynix does not assume any responsibility for

use of circuits described. No patent licenses are implied.

Rev 1.2 / July. 2009

1

1 page

Mobile DDR SDRAM 256Mbit (16M x 16bit)

H5MS2562JFR Series

The Hynix H5MS2562JFR series has the special Low Power function of Auto TCSR (Temperature Compensated Self

Refresh) to reduce self refresh current consumption. Since an internal temperature sensor is implemented, it enables

to automatically adjust refresh rate according to temperature without external EMRS command.

Deep Power Down Mode is an additional operating mode for Low Power DDR SDRAM (Mobile DDR SDRAM). This mode

can achieve maximum power reduction by removing power to the memory array within Low Power DDR SDRAM

(Mobile DDR SDRAM). By using this feature, the system can cut off almost all DRAM power without adding the cost of

a power switch and giving up mother-board power-line layout flexibility.

All inputs are LVCMOS compatible. Devices will have a VDD and VDDQ supply of 1.8V (nominal).

The Hynix H5MS2562JFR series is available in the following package:

- 60Ball FBGA [8mm x 10mm, t=1.0mm max]

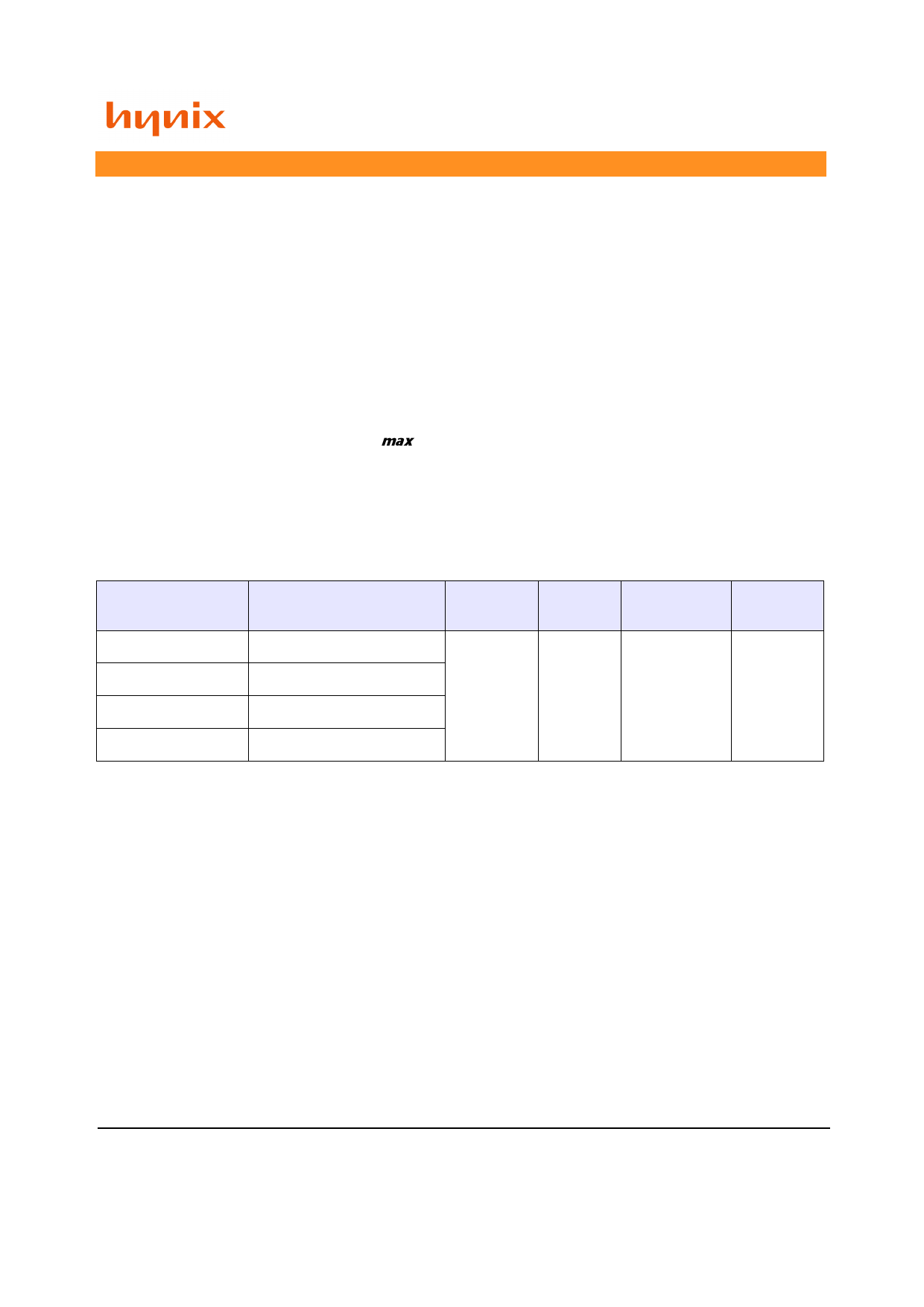

256Mb Mobile DDR SDRAM ORDERING INFORMATION

Part Number

H5MS2562JFR-E3M

H5MS2562JFR-J3M

H5MS2562JFR-K3M

H5MS2562JFR-L3M

Clock Frequency

Organiza-

tion

Interface

Operating

temperature

Package

200MHz(CL3) / 83MHz(CL2)

166MHz(CL3) / 83MHz(CL2) 4banks x 4Mb

133MHz(CL3) / 83MHz(CL2)

x 16

LVCMOS

Mobile Temp Lead & Halogen

(-30oC ~ 85oC)

Free

100MHz(CL3) / 66MHz(CL2)

Rev 1.2 / July. 2009

5

5 Page

Mobile DDR SDRAM 256Mbit (16M x 16bit)

H5MS2562JFR Series

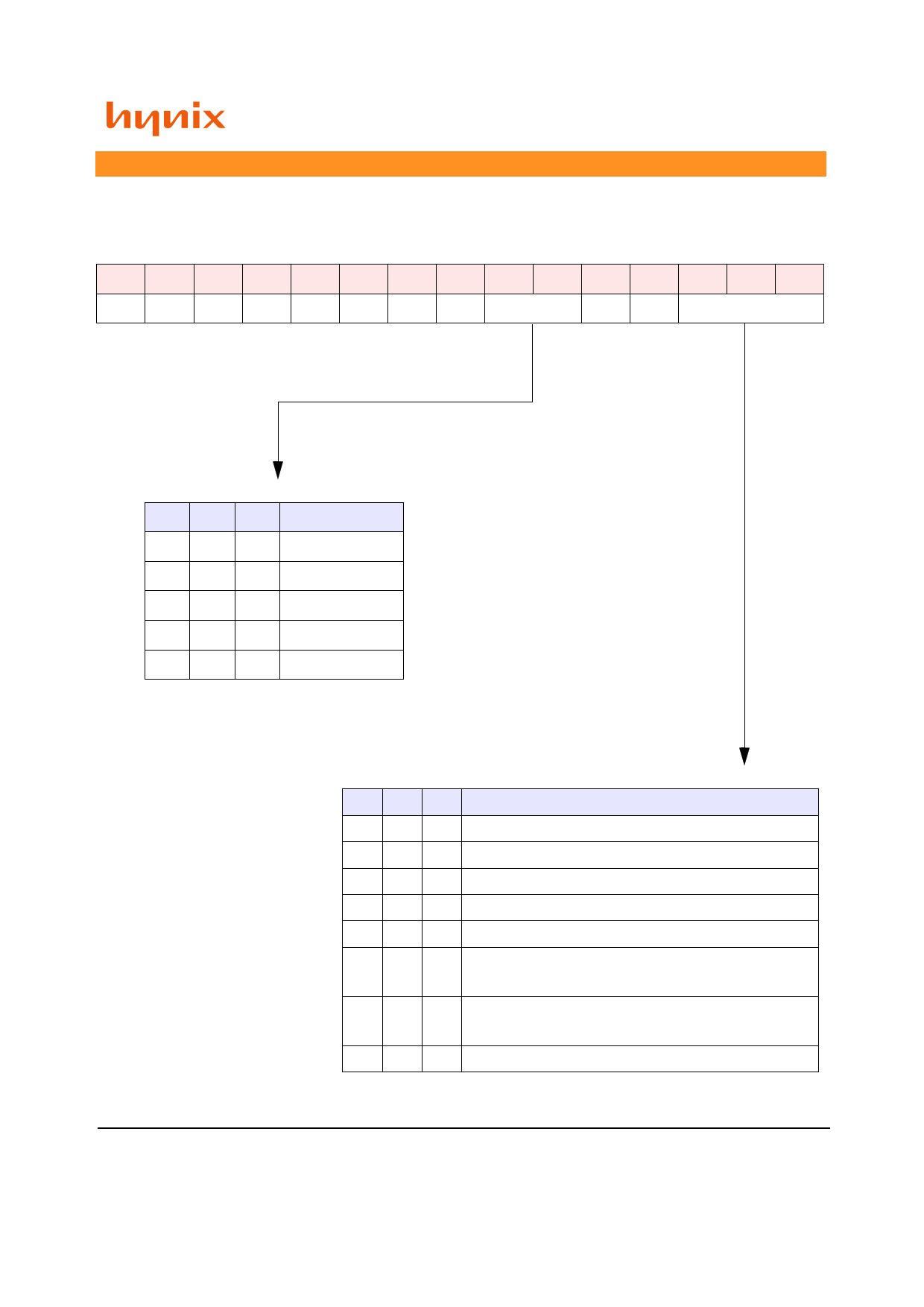

REGISTER DEFINITION II

Extended Mode Register Set (EMRS) for Mobile DDR SDRAM

BA1 BA0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1 0 0 0 0 0 0 0 DS 0 0

PASR

DS (Drive Strength)

A7 A6 A5 Drive Strength

0 0 0 Full

0 0 1 Half (Default)

0 1 0 Quarter

0 1 1 Octant

1 0 0 Three-Quarters

Rev 1.2 / July. 2009

PASR (Partial Array Self Refresh)

A2 A1 A0 Self Refresh Coverage

0 0 0 All Banks (Default)

0 0 1 Half of Total Bank (BA1=0)

0 1 0 Quarter of Total Bank (BA1=BA0=0)

0 1 1 Reserved

1 0 0 Reserved

1 0 1 One Eighth of Total Bank

(BA1 = BA0 = Row Address MSB=0)

1 1 0 One Sixteenth of Total Bank

(BA1 = BA0 = Row Address 2 MSBs=0)

1 1 1 Reserved

11

11 Page | ||

| Páginas | Total 62 Páginas | |

| PDF Descargar | [ Datasheet H5MS2562JFR-L3M.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| H5MS2562JFR-L3M | Mobile DDR SDRAM 256Mbit (16M x 16bit) | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |