|

|

PDF HCTL-2020 Data sheet ( Hoja de datos )

| Número de pieza | HCTL-2020 | |

| Descripción | Quadrature Decoder/Counter Interface ICs | |

| Fabricantes | Agilent(Hewlett-Packard) | |

| Logotipo | .gif) |

|

Hay una vista previa y un enlace de descarga de HCTL-2020 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

H

Quadrature Decoder/Counter

Interface ICs

Technical Data

HCTL-2000

HCTL-2016

HCTL-2020

Features

• Interfaces Encoder to

Microprocessor

• 14 MHz Clock Operation

• Full 4X Decode

• High Noise Immunity:

Schmitt Trigger Inputs Digital

Noise Filter

• 12 or 16-Bit Binary Up/

Down Counter

• Latched Outputs

• 8-Bit Tristate Interface

• 8, 12, or 16-Bit Operating

Modes

• Quadrature Decoder Output

Signals, Up/Down and Count

• Cascade Output Signals, Up/

Down and Count

• Substantially Reduced

System Software

Applications

• Interface Quadrature

Incremental Encoders to

Microprocessors

• Interface Digital Potentiom-

eters to Digital Data Input

Buses

Description

The HCTL-2000, 2016, 2020 are

CMOS ICs that perform the

quadrature decoder, counter, and

bus interface function. The

HCTL-20XX family is designed to

improve system performance

Devices

Part Number

HCTL-2000

HCTL-2016

HCTL-2020

Description

12-bit counter. 14 MHz clock operation.

All features of the HCTL-2000. 16-bit counter.

All features of the HCTL-2016. Quadrature decoder output

signals. Cascade output signals.

Package Drawing

A

A

B

ESD WARNING: Standard CMOS handling precautions should be observed with the HCTL-20XX family

ICs.

2-178

5965-5894E

1 page

Switching Characteristics

Table 5. Switching Characteristics Min/Max specifications at VDD = 5.0 ± 5%, TA = -40 to + 85°C.

Symbol Description

Min. Max. Units

1 tCLK Clock period

2 tCHH Pulse width, clock high

3 tCD[1] Delay time, rising edge of clock to valid, updated count

information on D0-7

70 ns

28 ns

65 ns

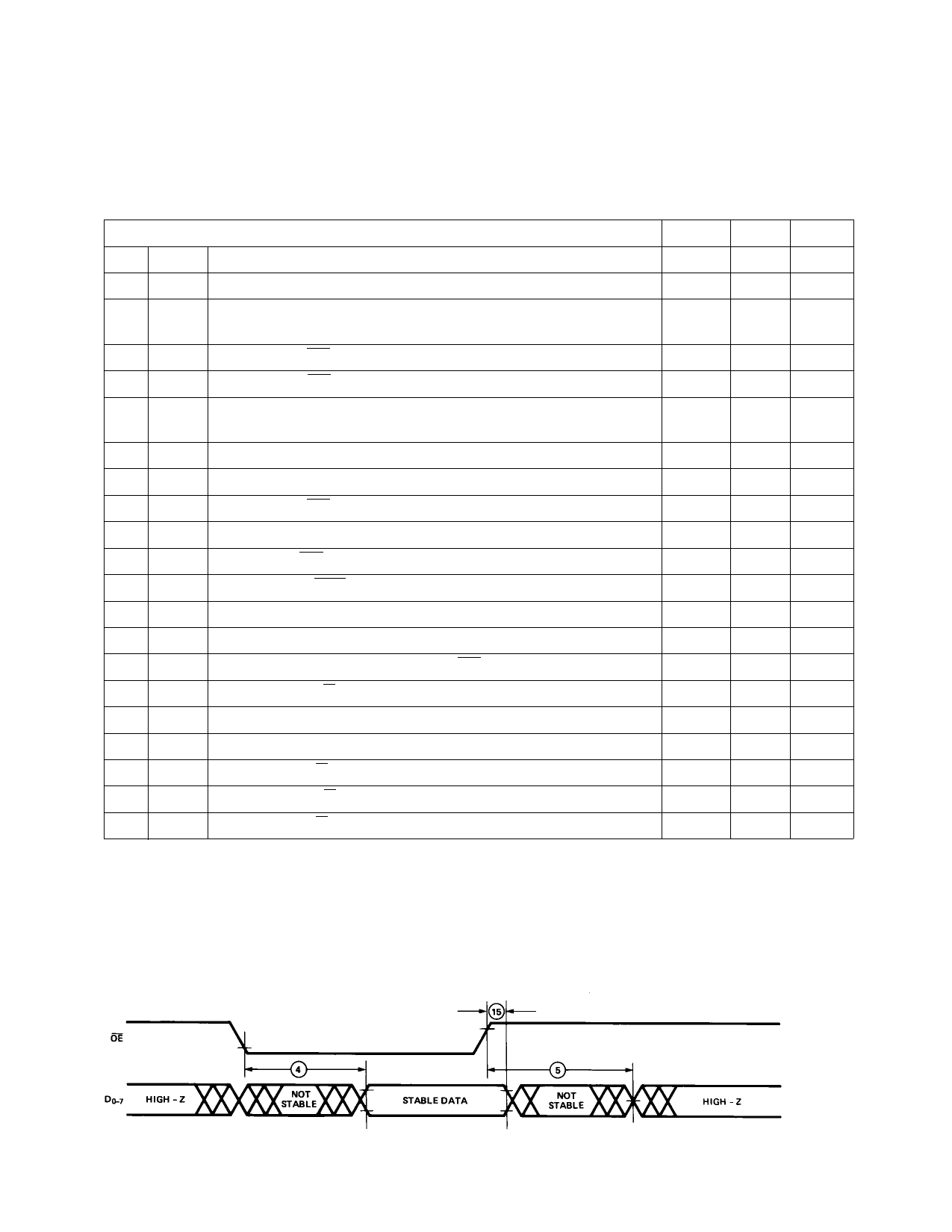

4 tODE Delay time, OE fall to valid data

5 tODZ Delay time, OE rise to Hi-Z state on D0-7

6 tSDV Delay time, SEL valid to stable, selected data byte

(delay to High Byte = delay to Low Byte)

65 ns

40 ns

65 ns

7 tCLH Pulse width, clock low

28

8 tSS[2] Setup time, SEL before clock fall

20

9 tOS[2] Setup time, OE before clock fall

20

10 tSH[2] Hold time, SEL after clock fall

0

11 tOH[2] Hold time, OE after clock fall

0

12 tRST Pulse width, RST low

28

13 tDCD Hold time, last position count stable on D0-7 after clock rise 10

14 tDSD Hold time, last data byte stable after next SEL state change

5

15 tDOD Hold time, data byte stable after OE rise

5

16 tUDD Delay time, U/D valid after clock rise

17 tCHD Delay time, CNTDCDR or CNTCAS high after clock rise

18 tCLD Delay time, CNTDCDR or CNTCAS low after clock fall

19 tUDH Hold time, U/D stable after clock rise

10

20 tUDCS Setup time, U/D valid before CNTDCDR or CNTCAS rise

tCLK-45

21 tUDCH Hold time, U/D stable after CNTDCDR or CNTCAS rise

tCLK-45

45

45

45

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Notes:

1. tCD specification and waveform assume latch not inhibited.

2. tSS, tOS, tSH, tOH only pertain to proper operation of the inhibit logic. In other cases, such as 8 bit read operations, these setup

and hold times do not need to be observed.

Figure 3. Tri-State Output Timing.

2-182

5 Page

CLK

CHAFILT*

CHBFILT*

U/D

CNTDCDR*

INTERNAL COUNTER

ROLL OVER

FF 00

START INHIBIT

CNTCAS

COUNT

FFFDH

FFFEH

FFFFH

0000H

FFFFH

FFFDH

*CHAFILT AND CHBFILT ARE THE OUTPUTS

OF THE DIGITAL NOISE FILTER (SEE FIGURES 7 AND 8).

Figure 12. Decode and Cascade Output Diagram.

Cascade Considerations

(HCTL-2020 Only)

The HCTL-2020’s cascading

system allows for position reads

of more than two bytes. These

reads can be accomplished by

latching all of the bytes and then

reading the bytes sequentially

over the 8-bit bus. It is assumed

here that, externally, a counter

followed by a latch is used to

count any count that exceeds 16

bits. This configuration is

compatible with the HCTL-2020

internal counter/latch

combination.

Consider the sequence of events

for a read cycle that starts as the

HCTL-2020’s internal counter

rolls over. On the rising clock

edge, count data is updated in the

internal counter, rolling it over. A

count-cascade pulse (CNTCAS)

will be generated with some delay

after the rising clock edge (tCHD).

There will be additional

propagation delays through the

external counters and registers.

Meanwhile, with SEL and OE low

to start the read, the internal

latches are inhibited at the falling

edge and do not update again till

the inhibit is reset. If the CNTCAS

pulse now toggles the external

counter and this count gets

latched a major count error will

occur. The count error is because

the external latches get updated

when the internal latch is

inhibited.

Valid data can be ensured by

latching the external counter data

when the high byte read is started

(SEL and OE low). This latched

external byte corresponds to the

count in the inhibited internal

latch. The cascade pulse that

occurs during the clock cycle

when the read begins gets

counted by the external counter

and is not lost.

For example, suppose the HCTL-

2020 count is at FFFFH and an

external counter is at F0H, with

the count going up. A count

occurring in the HCTL-2020 will

cause the counter to roll over and

a cascade pulse will be generated.

A read starting on this clock cycle

will show FFFFH from the HCTL-

2020. The external latch should

read F0H, but if the host latches

the count after the cascade signal

propagates through, the external

latch will read F1H.

2-188

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet HCTL-2020.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HCTL-2020 | Quadrature Decoder/Counter Interface ICs | Agilent(Hewlett-Packard) |

| HCTL-2020 | Quadrature Decoder/Counter Interface ICs | Agilent(Hewlett-Packard) |

| HCTL-2020 | (HCTL20xx) Quadrature Decoder/Counter Interface ICs | Hewlett-Packard |

| HCTL-2021 | (HCTL2017 / HCTL2021) Quadrature Decoder/Counter Interface ICs | AVAGO TECHNOLOGIES |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |