|

|

PDF NE33200 Data sheet ( Hoja de datos )

| Número de pieza | NE33200 | |

| Descripción | SUPER LOW NOISE HJ FET | |

| Fabricantes | California Eastern | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NE33200 (archivo pdf) en la parte inferior de esta página. Total 7 Páginas | ||

|

No Preview Available !

SUPER LOW NOISE HJ FET NE33200

FEATURES

• VERY LOW NOISE FIGURE:

0.75 dB typical at 12 GHz

• HIGH ASSOCIATED GAIN:

10.5 dB Typical at 12 GHz

• GATE LENGTH: 0.3 µm

• GATE WIDTH: 280 µm

DESCRIPTION

The NE33200 is a Hetero-Junction FET chip that utilizes the

junction between Si-doped AlGaAs and undoped InGaAs to

create a two-dimensional electron gas layer with very high

electron mobility. Its excellent low noise figure and high

associated gain make it suitable for commercial and industrial

applications.

NEC's stringent quality assurance and test procedures as-

sure the highest reliability and performance.

NOISE FIGURE & ASSOCIATED

GAIN vs. FREQUENCY

VDS = 2 V, IDS = 10 mA

4 24

3.5

Ga

3

21

18

2.5 15

2 12

1.5 9

1

0.5

0

1

NF

10

Frequency, f (GHz)

6

3

0

30

ELECTRICAL CHARACTERISTICS (TA = 25°C)

PART NUMBER

PACKAGE OUTLINE

NE33200

00 (Chip)

SYMBOLS

PARAMETERS AND CONDITIONS

UNITS

MIN

TYP MAX

NFOPT1

GA1

Noise Figure, VDS = 2 V, ID = 10 mA,

f = 4 GHz

f = 12 GHz

Associated Gain, VDS = 2 V, ID = 10 mA,

f = 4 GHz

f = 12 GHz

dB 0.35

dB 0.75 1.0

dB

dB 9.5

15.0

10.5

P1dB

Output Power at 1 dB Gain Compression Point, f = 12 GHz

VDS = 2 V, IDS = 10 mA

VDS = 2 V, IDS = 20 mA

dBm

dBm

11.2

12.0

G1dB

Gain at P1dB, f = 12 GHz

VDS = 2 V, IDS = 10 mA

VDS = 2 V, IDS = 20 mA

dB 11.8

dB 12.8

IDSS Saturated Drain Current, VDS = 2 V, VGS = 0 V

mA 15 40 80

VP Pinch-off Voltage, VDS = 2 V, ID = 100 µA

V -2.0 -0.8 -0.2

gm

IGSO

RTH(CH-C)2

Transconductance, VDS = 2 V, ID = 10 mA

Gate to Source Leakage Current, VGS = -5 V

Thermal Resistance (Channel to Case)

mS

µA

°C/W

45

70

0.5 10

240

Notes:

1. RF performance is determined by packaging and testing 10 samples per wafer. Wafer rejection criteria for standard devices is 2 rejects for

10 samples.

2. Chip mounted on infinite heat sink.

California Eastern Laboratories

1 page

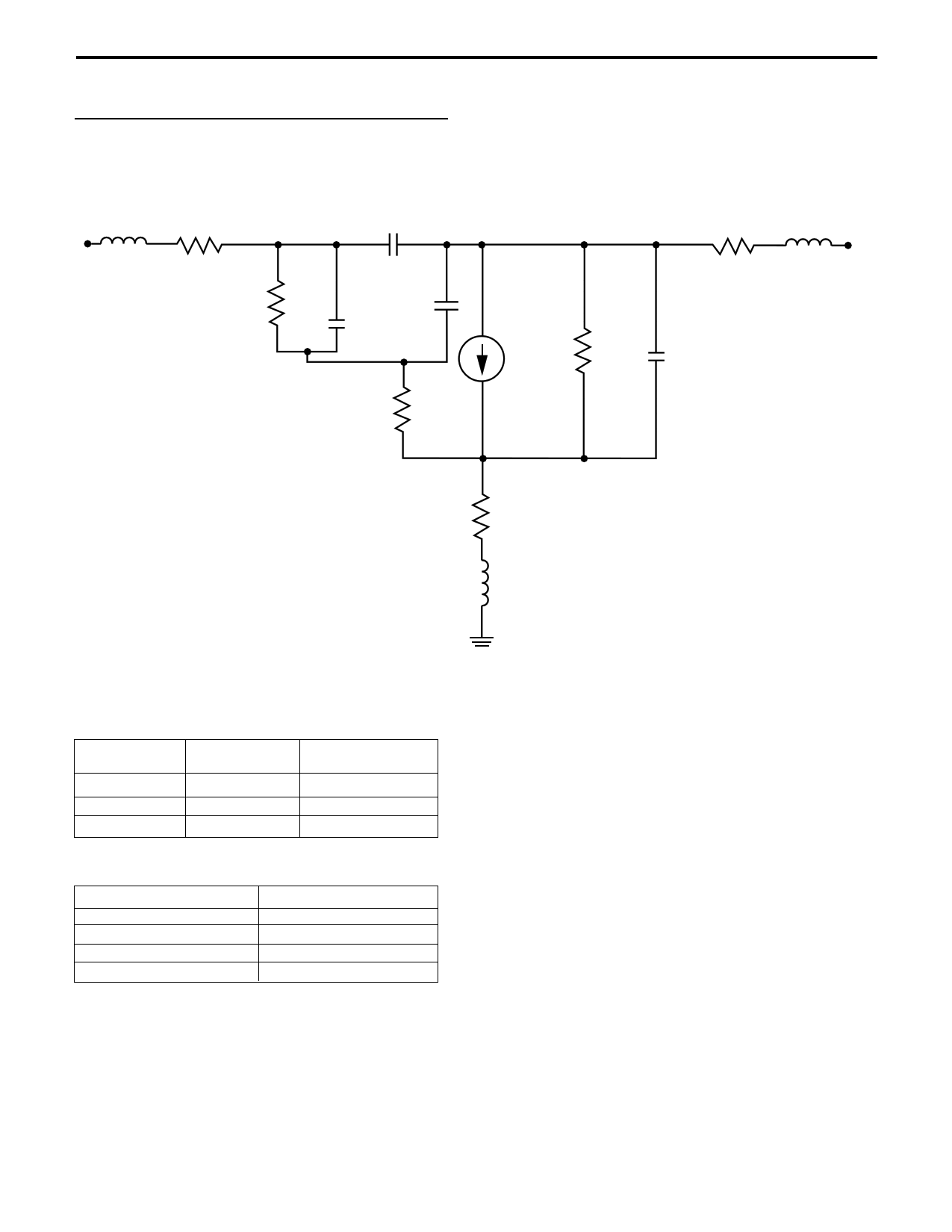

NE33200 LINEAR MODEL

SCHEMATIC

LG RG

0.19

GATE

0.16

GGS

1E-5

CDG

0.04

CGS CDC

0.22 0.065

RI

0.52

NE33200

RDS

g

t

f= 281GHz

RD

0.24

LD

0.2

DRAIN

CDS

0.05

RS

0.19

LS

0.03

SOURCE

BIAS DEPENDENT MODEL PARAMETERS

Parameters

g

t

RDS

2 V, 10 mA

73 mS

2.5 pSec

220 ohms

2 V, 20 mA

96 mS

3.5 pSec

160 ohms

UNITS

Parameter

capacitance

inductance

resistance

conductance

Units

picofarads

nanohenries

ohms

millisiemans

MODEL RANGE

Frequency: 0.1 to 26.5 GHz

Bias:

VDS = 2 V, ID = 10, 20 mA

Date:

7/19/96

5 Page | ||

| Páginas | Total 7 Páginas | |

| PDF Descargar | [ Datasheet NE33200.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NE33200 | SUPER LOW NOISE HJ FET | California Eastern |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |