No Preview Available !

Enpirion® Power Datasheet

EN5394QI 9A PowerSoC

Voltage Mode Synchronous

Buck PWM DC-DC Converter

With Integrated Inductor

Description

Typical Application Circuit

The EN5394QI is a Power Supply on a Chip

(PwrSoC) DC to DC converter with integrated

inductor, PWM controller, MOSFETS, and

compensation providing the smallest possible

solution size in a 68 pin QFN module. The

switching frequency can be synchronized to an

external clock or other EN5394QIs with the

added capability of phasing multiple EN5394QIs

as desired. Other features include precision

ENABLE threshold, pre-bias monotonic start-up,

margining, and parallel operation.

EN5394QI is specifically designed to meet the

precise voltage and fast transient requirements

of present and future high-performance

applications such as set-top boxes/HD DVRs,

LAN/SAN adapter cards, audio/video equipment,

optical networking, multi-function printers, test

and measurement, embedded computing,

storage, and servers. Advanced circuit

techniques, ultra high switching frequency, and

very advanced, high-density, integrated circuit

and proprietary inductor technology deliver high-

quality, ultra compact, non-isolated DC-DC

conversion. Operating this converter requires

very few external components.

The Altera Enpirion integrated inductor solution

significantly helps to reduce noise. The complete

power converter solution enhances productivity

by offering greatly simplified board design, layout

and manufacturing requirements.

All Altera Enpirion products are RoHS compliant

and lead-free manufacturing environment

compatible.

VIN

47µF

15nF

PVIN VOUT

AVIN

ENABLE

PGND VFB

SS

OCP_ADJ

PGND

AGND

VOUT

2x47µF

Figure 1: Typical Application Schematic

Features

• Integrated Inductor, MOSFETS, Controller in

a 8 x 11 x 1.85mm package

• Wide input voltage range of 2.375V to 6.6V.

• > 30W continuous output power.

• High efficiency, up to 93%.

• Output voltage margining

• Monotonic output voltage ramp during start-

up with pre-biased loads.

• Precision Enable pin for accurate sequencing

of power converters and Power OK signal.

• Programmable soft-start time.

• Soft Shutdown.

• 4 MHz operating frequency with ability to

synchronize to an external system clock or

other EN5394’s.

• Programmable phase delays between

synchronized units to allow reduction of

input ripple.

• Master/slave configuration for paralleling

multiple EN5394’s for greater power output.

• Under Voltage Lockout, Over-current, Short

Circuit, and Thermal Protection

• RoHS compliant, MSL level 3, 260C reflow.

03738

1

October 11, 2013

www.altera.com/enpirion

Rev E

EN5394QI

Electrical Characteristics table. See Figures 6 be used advantageously for power supply

and 7 for an example of using phase delay.

sequencing using the precision Enable threshold.

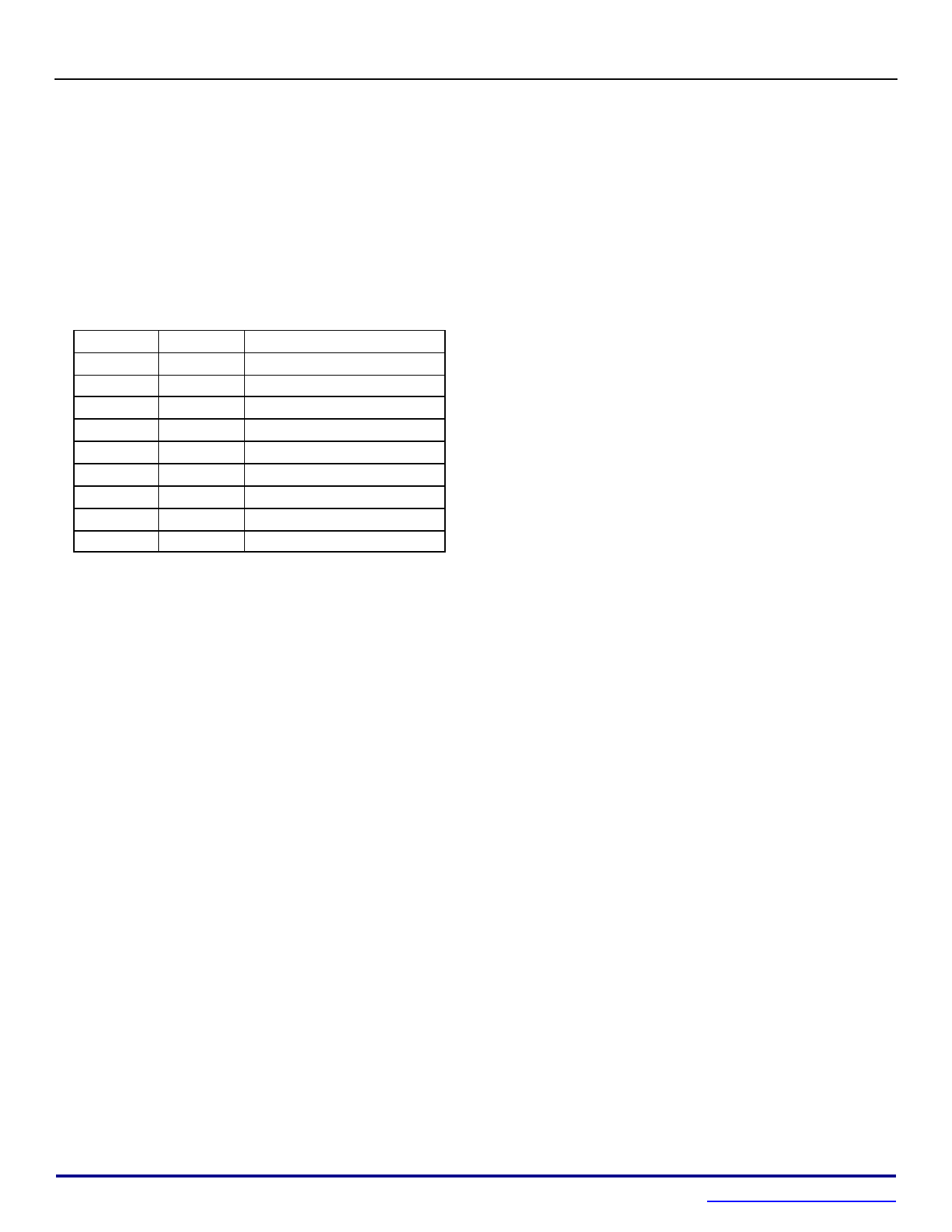

Margining

Using MAR1 and MAR2 pins, the nominal output

voltage can be increased / decreased by 2.5, 5

or 10% for system compliance, reliability or other

tests. The POK threshold voltages scale with the

margined output voltages. The following table

provides the possible combinations:

MAR1 MAR2 Output Modulation

Float Float

0%

Low Low

-2.5%

High

Low

+2.5%

Low High

-5%

High High

+5%

Low Float

-10%

High Float

+10%

Float High

0%, Delay Bypass

Float Low

Reserved

Note: Low means tie to GND. High means tie to VIN

as shown in Figure 5.

As shown above, when MAR1 is floating, and

MAR2 is high, the device enters the delay

bypass mode. In this mode, the delay from the

internal clock or S_IN to S_OUT is almost

eliminated (see Electrical Characteristics table).

Soft-Start Operation

The SS pin in conjunction with a small external

capacitor between this pin and AGND provides

the soft start function to limit the in-rush current

during start-up. During start-up of the converter

the reference voltage to the error amplifier is

gradually increased to its final level as an internal

current source of typically 10uA charges the soft

start capacitor. The typical soft-start time for the

output to reach regulation voltage, from when

AVIN > VUVLO and ENABLE crosses its logic high

threshold, is given by:

TSS = (CSS * 65KΩ) ± 25%

where the soft-start time TSS is in seconds and

the soft-start capacitance CSS is in Farads.

Typically, around 15nF is recommended. The

soft-start capacitor should be between 4.7nF and

100nF. A proper choice of SS capacitance can

During a soft-start cycle, when the soft-start

capacitor voltage reaches 0.60V, the output has

reached its programmed regulation range. Note

that the soft-start current source will continue to

charge the SS capacitor beyond 0.6V. During

normal operation, the soft-start capacitor will

charge to a final value of ~1.5V.

Soft-Shutdown Operation

When the Enable signal is de-asserted, the soft-

start capacitor is discharged in a controlled

manner. Thus the output voltage ramps down

gradually. The internal circuits are kept active for

the duration of soft-shutdown, thereafter they are

deactivated.

Pre-Bias Operation

When EN_PB is asserted, the device will support

a monotonic output voltage ramp if the output

capacitor is charged to a pre-bias level.

Proprietary circuit ensures the output voltage

ramps monotonically from pre-bias voltage to the

programmed output voltage. Monotonic start-up

is guaranteed by design for pre-bias voltages

between 20% and 85% of the programmed

output voltage. This feature is not supported

when ENABLE is tied to VIN.

POK Operation

The POK signal indicates if the output voltage is

within a specified range. The POK signal is

asserted when the rising output voltage crosses

92% (nominal) of the programmed output

voltage. POK is de-asserted ~50us (256 clock

cycles) after the falling output voltage crosses

90% (nominal) of the programmed voltage. POK

is also de-asserted if the output voltage exceeds

120% of the programmed output. If the feedback

loop is broken, POK will remain de-asserted

(output < 92% of programmed value), and the

output voltage will equal the input voltage. If

however, there is a short across the PFET, and

the feedback is in place, POK will be de-asserted

as an over voltage condition. The power NFET is

also turned on, resulting in a large input supply

current. This in turn is expected to trip the OCP

03738

11

October 11, 2013

www.altera.com/enpirion

Rev E