|

|

PDF HDSP-4200 Data sheet ( Hoja de datos )

| Número de pieza | HDSP-4200 | |

| Descripción | 20 mm (0.8 inch) Seven Segment Displays | |

| Fabricantes | Agilent(Hewlett-Packard) | |

| Logotipo | .gif) |

|

Hay una vista previa y un enlace de descarga de HDSP-4200 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Low Cost Gigabit Rate

Transmit/Receive Chip Set with

TTL I/Os

Preliminary Technical Data

HDMP-1022 Transmitter

HDMP-1024 Receiver

Features

• Transparent, Extended

Ribbon Cable Replacement

• Implemented in a Low Cost

Aluminum M-Quad 80

Package

• High-Speed Serial Rate

150-1500 MBaud

• Standard TTL Interface

16, 17, 20, or 21 Bits Wide

• Reliable Monolithic Silicon

Bipolar Implementation

• On-Chip Phase-Locked

Loops

- Transmit Clock Generation

- Receive Clock Extraction

Applications

• Backplane/Bus Extender

• Video, Image Acquisition

• Point to Point Data Links

• Implement SCI-FI Standard

• Implement Serial HIPPI

Specification

Description

The HDMP-1022 transmitter and

the HDMP-1024 receiver are used

to build a high-speed data link for

point-to-point communication.

The monolithic silicon bipolar

transmitter chip and receiver chip

are each provided in a standard

aluminum M-Quad 80 package.

From the user’s viewpoint, these

products can be thought of as

providing a “virtual ribbon cable”

interface for the transmission of

data. Parallel data (a frame)

loaded into the Tx (transmitter)

chip is delivered to the Rx

(receiver) chip over a serial

channel, which can be either a

coaxial copper cable or optical

link.

The chip set hides from the user

all the complexity of encoding,

multiplexing, clock extraction,

demultiplexing and decoding.

Unlike other links, the phase-

locked-loop clock extraction

circuit also transparently provides

for frame synchronization–the

user is not troubled with the

periodic insertion of frame syn-

chronization words. In addition,

the dc balance of the line code is

automatically maintained by the

chip set. Thus, the user can

transmit arbitrary data without

restriction. The Rx chip also

includes a state-machine con-

troller (SMC) that provides a

startup handshake protocol for

the duplex link configuration.

The serial data rate of the T/R link

is selectable in four ranges (see

tables on page 5), and extends

from 120 Mbits/s up to 1.25

Gbits/s. The parallel data interface

is 16 or 20 bit TTL, pin select-

able. A flag bit is available and

can be used as an extra 17th or

21st bit under the user’s control.

The flag bit can also be used as an

even or odd frame indicator for

dual-frame transmission. If not

used, the link performs expanded

error detection.

The serial link is synchronous,

and both frame synchronization

and bit synchronization are main-

tained. When data is not available

to send, the link maintains

synchronization by transmitting

fill frames. Two (training) fill

frames are reserved for

handshaking during link startup.

User control space is also sup-

ported. If Control Available is

asserted at the Tx chip, the least

significant 14 or 18 bits of the

data are sent and the Rx Control

Available line will indicate the

data as a Control Word.

It is the intention of this data

sheet to provide the design

engineer all of the information

regarding the HDMP-1022/1024

chipset necessary to design this

product into their application. To

assist you in using this data sheet,

the following Table of Contents is

provided.

(5/97)

615

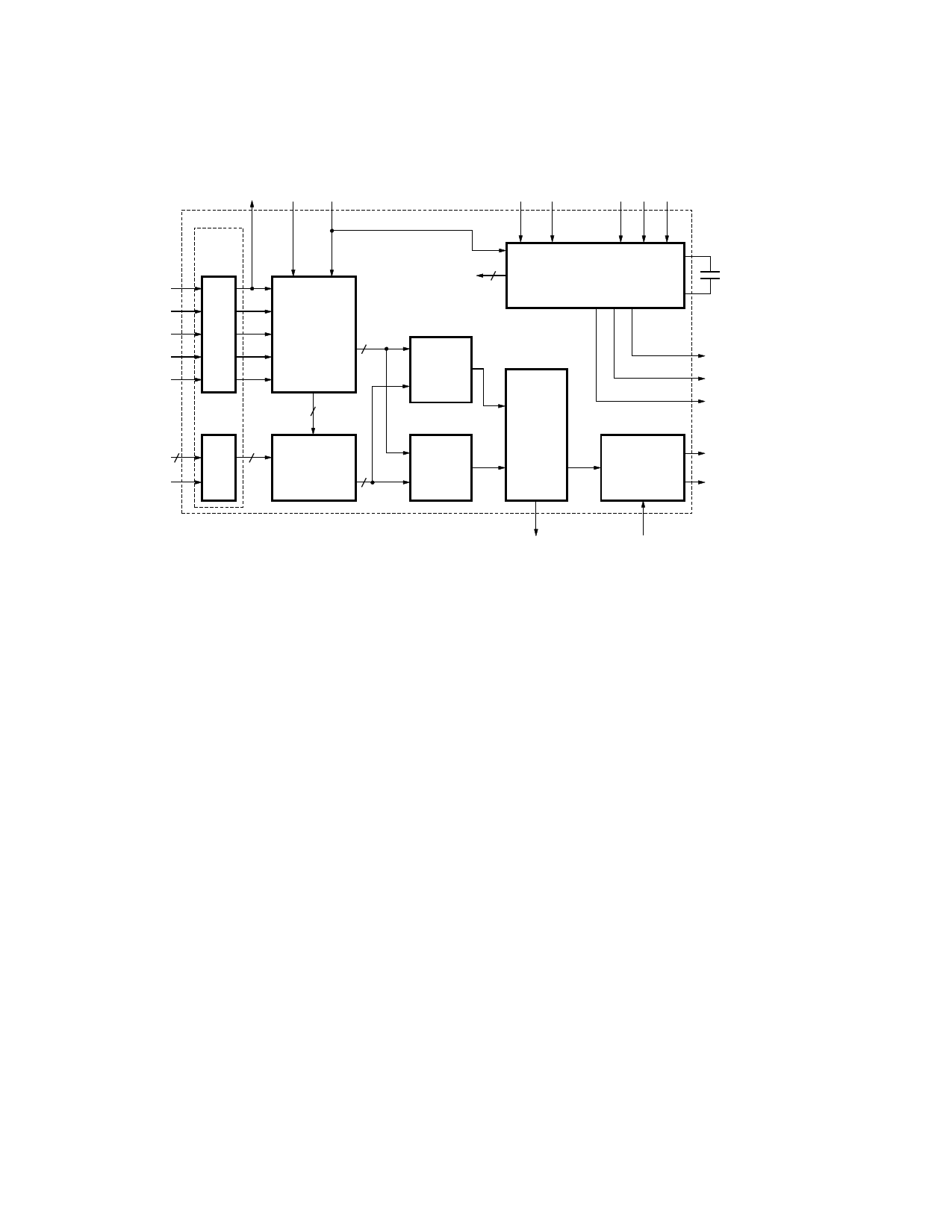

1 page

ED

FF

CAV*

DAV*

FLAG

INPUT

LATCH

CONTROL

LOGIC

+

C-FIELD

ENCODER

D0-D19

RST*

D-FIELD

ENCODER

INTERNAL

CLOCKS

SIGN

FRAME

MUX

PLL / CLOCK

GENERATOR

CAP0

0.1 µF

CAP1

STRBOUT

HCLK

LOCKED

OUTPUT

SELECT

DOUT

LOUT

Figure 4. HDMP-1022 Transmitter Block Diagram.

INV LOOPEN

HDMP-1022 Tx Block

Diagram

The HDMP-1022 was designed to

accept 16 or 20 bit wide parallel

data (frames) and transmit it over

a high speed serial line, while

minimizing the user’s necessary

interface to the high speed cir-

cuitry. In order to accomplish this

task, the HDMP-1022 performs

the following functions:

• Parallel Word Input

• High Speed Clock Multiplication

• Frame Encoding

• Parallel to Serial Multiplexing

PLL/Clock Generator

The Phase Lock-loop and Clock

Generator are responsible for

generating all internal clocks

needed by the transmitter to

perform its functions. These

clocks are based on a supplied

frame clock (STRBIN) and control

signals (M20SEL, MDFSEL,

EHCLKSEL, DIV1, DIV0). In

normal operation (MDFSEL=0),

STRBIN is expected to be the

incoming frame clock. The PLL/

Clock Generator locks on to this

incoming rate and multiplies the

clock up to the needed high speed

serial clock. Based on M20SEL,

which determines whether the

incoming data frame is 16 or 20

bits wide, the PLL/Clock Gener-

ator multiplies the frame rate

clock by 20 or 24 respectively

(data bits + 4 control bits). DIV1/

DIV0 are set to inform the

transmitter of the frequency range

of the incoming data frames. The

internal frame rate clock is

accessible through STRBOUT and

the high speed serial clock is

accessible through HCLK.

When MDFSEL is set high, the

transmitter is in Double Frame

Mode. Using this option, the user

may send a 32 or 40 bit wide data

frame in two segments while

supplying the original 32 or 40 bit

frame clock at STRBIN. Doubling

of the frame rate is performed by

the transmitter. The clock

generator section performs the

clock multiplication to the

necessary serial clock rate.

By setting EHCLKSEL high, the

user may provide an external high

speed serial clock at STRBIN.

This clock is used directly by the

high speed serial circuitry to

output the serial data.

Control Logic and C-Field

Encoder

The Control Logic is responsible

for determining what information

is serially sent to the output. If

CAV* is low, it sends the data at

D0..D8 and D9..D17 as control

word information. If CAV* is high

and DAV* is low, it sends parallel

word data at the data inputs. If

neither CAV* nor DAV* is set low,

then the transmitter assumes the

link is not being used. In this

state, the control logic triggers

the Data Encoder to send Fill

Frames to maintain the link DC

620

5 Page

HDMP-1022 (Tx), HDMP-1024 (Rx)

DC Electrical Specifications

Tc = 0°C to +85°C, VCC = 4.5 V to -5.5 V

Symbol

Parameter

VIH,TTL TTL Input High Voltage Level, Guaranteed high signal for

all inputs

Units Min. Typ.

V 2.0

VIL,TTL

VOH,TTL

VOL,TTL

IIH,TTL

IIL,TTL

VIP,H50

VOP,BLL

TTL Input Low Voltage Level, Guaranteed low signal for all

inputs

TTL Output High Voltage Level, IOH = -400 µA

TTL Output Low Voltage Level, IOL = 1 mA

Input High Current (Magnitude), VIN = VCC

Input Low Current (Magnitude), VIN = 0 Volts

H50 Input Peak-To-Peak Voltage

BLL Output Peak-To-Peak Voltage, Terminated with 50 Ω,

ac coupled

V0

V 2.4

V0

µA 0.004

µA 295

mV 200

mV 500

ICC,Tx Transmitter VCC Supply Current, with HCLKSEL off mA 385

Tc = 50°C

ICC,Rx Receiver VCC Supply Current, Tc = 50°C

mA 500

Note:

1. BLL outputs are measured with external 150 Ω pull-up resistors to ground. Refer to Figure 23 for additional information.

Max.

VCC

0.8

VCC

0.6

40

600

470

600

HDMP-1022 (Tx), HDMP-1024 (Rx)

AC Electrical Specifications

Tc = 25°C

Symbol

Parameter

Units Min. Typ.

tr,TTLin

tf,TTLin

tr,TTLout

tf,TTLout

tr, BLL

tf,BLL

VSWRi,H50

VSWRo,BLL

Input TTL Rise Time, 0.8 to 2.0 Volts

Input TTL Fall Time, 2.0 to 0.8 Volts

Output TTL Rise Time, 0.8 to 2.0 Volts, 10 pF load

Output TTL Fall Time, 2.0 to 0.8 Volts, 10 pF load

BLL Rise Time, Terminated with 50 Ω, ac coupled

BLL Fall Time, Terminated with 50 Ω, ac coupled

H50 Input VSWR

BLL Output VSWR

nsec

nsec

nsec

nsec

psec

psec

2

2

1.1

1.5

240

240

2:1

2:1

Note:

1. BLL outputs are measured with external 150 Ω pull-up resistors to ground. Refer to Figure 23 for additional information.

Max.

2.4

2.4

HDMP-1022 (Tx), HDMP-1024 (Rx)

Typical Lock-Up Time

Tc = 25°C

DIV1

DIV0

HDMP-1022, msec

HDMP-1024, msec

00

2.0

2.2

01

3.0

3.2

10

4.5

4.7

11

8.0

11.0

Note:

1. Measured in Local Loop-Back mode with the state machine engaged and 0 cable length.

626

LINK[1], msec

2.5

3.5

5.0

12.0

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HDSP-4200.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HDSP-4200 | 20 mm (0.8 inch) Seven Segment Displays | Agilent(Hewlett-Packard) |

| HDSP-4200 | (HDSP-xxxx) 7-Segment Displays | Hewlett-Packard |

| HDSP-420X | 20 mm (0.8 inch) Seven Segment Displays | Agilent(Hewlett-Packard) |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |