|

|

PDF FDMF6707B Data sheet ( Hoja de datos )

| Número de pieza | FDMF6707B | |

| Descripción | High-Frequency DrMOS Module | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de FDMF6707B (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

March 2012

FDMF6707B - Extra-Small, High-Performance, High-

Frequency DrMOS Module

Benefits

Ultra-Compact 6x6mm PQFN, 72% Space-Saving

Compared to Conventional Discrete Solutions

Fully Optimized System Efficiency

Clean Switching Waveforms with Minimal Ringing

High-Current Handling

Features

Over 93% Peak-Efficiency

High-Current Handling of 50A

High-Performance PQFN Copper-Clip Package

3-State 3.3V PWM Input Driver

Skip-Mode SMOD# (Low-Side Gate Turn Off) Input

Thermal Warning Flag for Over-Temperature

Condition

Driver Output Disable Function (DISB# Pin)

Internal Pull-Up and Pull-Down for SMOD# and

DISB# Inputs, Respectively

Fairchild PowerTrench® Technology MOSFETs for

Clean Voltage Waveforms and Reduced Ringing

Fairchild SyncFET™ (Integrated Schottky Diode)

Technology in the Low-Side MOSFET

Integrated Bootstrap Schottky Diode

Adaptive Gate Drive Timing for Shoot-through

Protection

Under-Voltage Lockout (UVLO)

Optimized for Switching Frequencies up to 1MHz

Low-Profile SMD Package

Fairchild Green Packaging and RoHS Compliant

Based on the Intel® 4.0 DrMOS Standard

Description

The XS™ DrMOS family is Fairchild’s next-generation,

fully optimized, ultra-compact, integrated MOSFET plus

driver power stage solution for high-current, high-

frequency, synchronous buck DC-DC applications. The

FDMF6707B integrates a driver IC, two power MOSFETs,

and a bootstrap Schottky diode into a thermally

enhanced, ultra-compact 6x6mm PQFN package.

With an integrated approach, the complete switching

power stage is optimized for driver and MOSFET

dynamic performance, system inductance, and power

MOSFET RDS(ON). XS™ DrMOS uses Fairchild's high-

performance PowerTrench® MOSFET technology,

which dramatically reduces switch ringing, eliminating

the snubber circuit in most buck converter applications.

A new driver IC with reduced dead times and

propagation delays further enhances performance. A

thermal warning function warns of potential over-

temperature situations. FDMF6707B also incorporates

features such as Skip Mode (SMOD) for improved light-

load efficiency, along with a 3-state 3.3V PWM input for

compatibility with a wide range of PWM controllers.

Applications

High-Performance Gaming Motherboards

Compact Blade Servers, V-Core and Non-V-Core

DC-DC Converters

Desktop Computers, V-Core and Non-V-Core

DC-DC Converters

Workstations

High-Current DC-DC Point-of-Load (POL)

Converters

Networking and Telecom Microprocessor Voltage

Regulators

Small Form-Factor Voltage Regulator Modules

Ordering Information

Part Number

FDMF6707B

Current Rating

50A

Package

Top Mark

40-Lead, Clipbond PQFN DrMOS, 6.0mm x 6.0mm Package FDMF6707B

© 2011 Fairchild Semiconductor Corporation

FDMF6707B • Rev. 1.0.2

www.fairchildsemi.com

Free Datasheet http://www.datasheet4u.com/

1 page

Electrical Characteristics

Typical values are VIN = 12V, VCIN = 5V, VDRV = 5V, and TA = +25°C unless otherwise noted.

Symbol

Parameter

Basic Operation

IQ

UVLO

Quiescent Current

UVLO Threshold

UVLO_Hyst UVLO Hysteresis

PWM Input (VCIN = VDRV = 5V +/- 10%)

RUP_PWM

RDN_PWM

VIH_PWM

VTRI_HI

VTRI_LO

VIL_PWM

tD_HOLD-OFF

VHiZ_PWM

Pull-Up Impedance

Pull-Down Impedance

PWM High Level Voltage

3-State Upper Threshold

3-State Lower Threshold

PWM Low Level Voltage

3-State Shutoff Time

3-State Open Voltage

PWM Input (VCIN = VDRV = 5V ±5%)

RUP_PWM

RDN_PWM

VIH_PWM

VTRI_HI

VTRI_LO

VIL_PWM

tD_HOLD-OFF

VHiZ_PWM

Pull-Up Impedance

Pull-Down Impedance

PWM High Level Voltage

3-State Upper Threshold

3-State Lower Threshold

PWM Low Level Voltage

3-State Shutoff Time

3-State Open Voltage

DISB# Input

VIH_DISB High-Level Input Voltage

VIL_DISB

IPLD

Low-Level Input Voltage

Pull-Down Current

tPD_DISBL Propagation Delay

tPD_DISBH Propagation Delay

SMOD# Input

VIH_SMOD High-Level Input Voltage

VIL_SMOD Low-Level Input Voltage

IPLU Pull-Up Current

tPD_SLGLL Propagation Delay

tPD_SHGLH Propagation Delay

Condition

Min. Typ. Max. Unit

IQ=IVCIN+IVDRV, PWM=LOW or HIGH or Float

2 mA

VCIN Rising

2.9 3.1 3.3 V

0.4 V

26

12

1.88 2.25 2.61

1.84 2.20 2.56

0.70 0.95 1.19

0.62 0.85 1.13

160 200

1.40 1.60 1.90

kΩ

kΩ

V

V

V

V

ns

V

26

12

2.00 2.25 2.50

1.94 2.20 2.46

0.75 0.95 1.15

0.66 0.85 1.09

160 200

1.45 1.60 1.80

kΩ

kΩ

V

V

V

V

ns

V

PWM=GND, Delay Between DISB# from

HIGH to LOW to GL from HIGH to LOW

PWM=GND, Delay Between DISB# from

LOW to HIGH to GL from LOW to HIGH

2V

0.8 V

10 µA

25 ns

25 ns

2V

0.8 V

10 µA

PWM=GND, Delay Between SMOD# from

HIGH to LOW to GL from HIGH to LOW

10

ns

PWM=GND, Delay Between SMOD# from

LOW to HIGH to GL from LOW to HIGH

10 Ns

Continued on the following page…

© 2011 Fairchild Semiconductor Corporation

FDMF6707B • Rev. 1.0.2

5

www.fairchildsemi.com

Free Datasheet http://www.datasheet4u.com/

5 Page

Functional Description

The FDMF6707B is a driver-plus-FET module optimized

for the synchronous buck converter topology. A single

PWM input signal is all that is required to properly drive

the high-side and the low-side MOSFETs. Each part is

capable of driving speeds up to 1MHz.

VCIN and Disable (DISB#)

The VCIN pin is monitored by an under-voltage lockout

(UVLO) circuit. When VCIN rises above ~3.1V, the driver

is enabled for operation. When VCIN falls below ~2.7V,

the driver is disabled (GH, GL=0). The driver can also

be disabled by pulling the DISB# pin LOW (DISB# <

VIL_DISB), which holds both GL and GH LOW regardless

of the PWM input state. The driver can be enabled by

raising the DISB# pin voltage HIGH (DISB# > VIH_DISB).

Table 1. UVLO and Disable Logic

UVLO

0

1

1

1

DISB#

X

0

1

Open

Driver State

Disabled (GH, GL=0)

Disabled (GH, GL=0)

Enabled (See Table 2)

Disabled (GH, GL=0)

Note:

3. DISB# internal pull-down current source is 10µA.

Thermal Warning Flag (THWN#)

The FDMF6707B provides a thermal warning flag

(THWN#) to advise of over-temperature conditions. The

thermal warning flag uses an open-drain output that

pulls to CGND when the activation temperature (150°C)

is reached. The THWN# output returns to high-

impedance state once the temperature falls to the reset

temperature (135°C). For use, the THWN# output

requires a pull-up resistor, which can be connected to

VCIN. THWN# does NOT disable the DrMOS module.

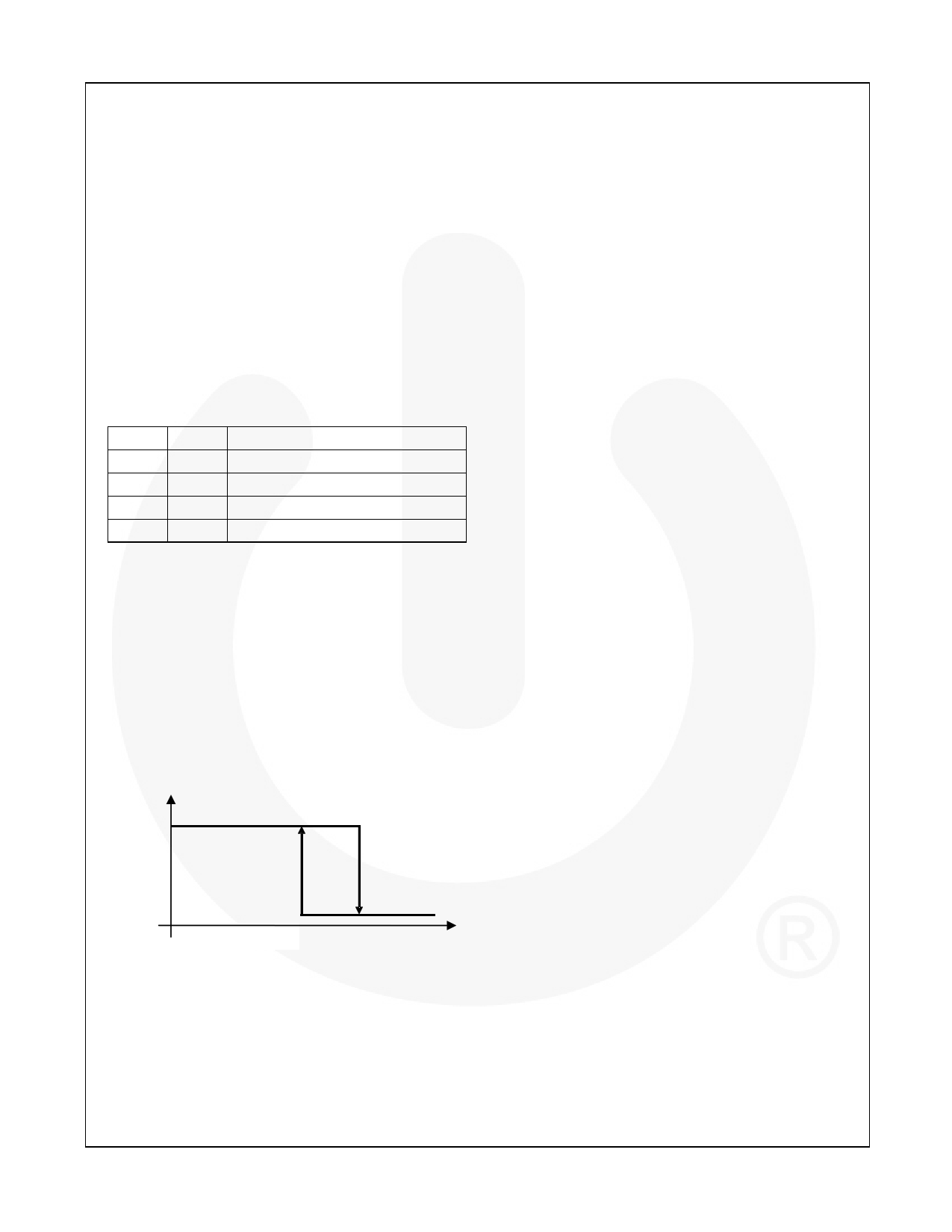

THWN#

Logic

State

HIGH

135°C Reset

Temperature

150°C

Activation

Temperature

Normal

Operation

Thermal

Warning

LOW

TJ_driver IC

Figure 24. THWN Operation

3-State PWM Input

The FDMF6707B incorporates a 3-state 3.3V PWM

input gate drive design. The 3-state gate drive has both

logic HIGH level and LOW level, along with a 3-state

shutdown window. When the PWM input signal enters

and remains within the 3-state window for a defined

hold-off time (tD_HOLD-OFF), both GL and GH are pulled

LOW. This feature enables the gate drive to shut down

both high-and low-side MOSFETs to support features

such as phase shedding, a common feature on multi-

phase voltage regulators.

Exiting 3-State Condition

When exiting a valid 3-state condition, the FDMF6707B

design follows the PWM input command. If the PWM

input goes from 3-state to LOW, the low-side MOSFET

is turned on. If the PWM input goes from 3-state to

HIGH, the high-side MOSFET is turned on, as illustrated

in Figure 25. The FDMF6707B design allows for short

propagation delays when exiting the 3-state window

(see Electrical Characteristics).

Low-Side Driver

The low-side driver (GL) is designed to drive a ground-

referenced low RDS(ON) N-channel MOSFET. The bias

for GL is internally connected between VDRV and

CGND. When the driver is enabled, the driver's output is

180° out of phase with the PWM input. When the driver

is disabled (DISB#=0V), GL is held LOW.

High-Side Driver

The high-side driver is designed to drive a floating N-

channel MOSFET. The bias voltage for the high-side

driver is developed by a bootstrap supply circuit

consisting of the internal Schottky diode and external

bootstrap capacitor (CBOOT). During startup, VSWH is

held at PGND, allowing CBOOT to charge to VDRV

through the internal diode. When the PWM input goes

HIGH, GH begins to charge the gate of the high-side

MOSFET (Q1). During this transition, the charge is

removed from CBOOT and delivered to the gate of Q1.

As Q1 turns on, VSWH rises to VIN, forcing the BOOT

pin to VIN + VBOOT, which provides sufficient VGS

enhancement for Q1. To complete the switching cycle,

Q1 is turned off by pulling GH to VSWH. CBOOT is then

recharged to VDRV when VSWH falls to PGND. GH

output is in-phase with the PWM input. The high-side

gate is held LOW when the driver is disabled or the

PWM signal is held within the 3-state window for

longer than the 3-state hold-off time, tD_HOLD-OFF.

© 2011 Fairchild Semiconductor Corporation

FDMF6707B • Rev. 1.0.2

11

www.fairchildsemi.com

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet FDMF6707B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FDMF6707B | High-Frequency DrMOS Module | Fairchild Semiconductor |

| FDMF6707C | High-Frequency DrMOS Module | Fairchild Semiconductor |

| FDMF6707V | High-Frequency DrMOS Module | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |