|

|

PDF AD9639 Data sheet ( Hoja de datos )

| Número de pieza | AD9639 | |

| Descripción | 170 MSPS/210 MSPS Serial Output 1.8 V ADC | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9639 (archivo pdf) en la parte inferior de esta página. Total 36 Páginas | ||

|

No Preview Available !

Data Sheet

Quad, 12-Bit, 170 MSPS/210 MSPS

Serial Output 1.8 V ADC

AD9639

FEATURES

4 ADCs in one package

JESD204 coded serial digital outputs

On-chip temperature sensor

−95 dB channel-to-channel crosstalk

SNR: 65 dBFS with AIN = 85 MHz at 210 MSPS

SFDR: 77 dBc with AIN = 85 MHz at 210 MSPS

Excellent linearity

DNL: ±0.28 LSB (typical)

INL: ±0.7 LSB (typical)

780 MHz full power analog bandwidth

Power dissipation: 325 mW per channel at 210 MSPS

1.25 V p-p input voltage range, adjustable up to 1.5 V p-p

1.8 V supply operation

Clock duty cycle stabilizer

Serial port interface features

Power-down modes

Digital test pattern enable

Programmable header

Programmable pin functions (PGMx, PDWN)

APPLICATIONS

Communication receivers

Cable head end equipment/M-CMTS

Broadband radios

Wireless infrastructure transceivers

Radar/military-aerospace subsystems

Test equipment

GENERAL DESCRIPTION

The AD9639 is a quad, 12-bit, 210 MSPS analog-to-digital con-

verter (ADC) with an on-chip temperature sensor and a high

speed serial interface. It is designed to support the digitizing

of high frequency, wide dynamic range signals with an input

bandwidth of up to 780 MHz. The output data is serialized

and presented in packet format, consisting of channel-specific

information, coded samples, and error code correction.

The ADC requires a single 1.8 V power supply. The input clock

can be driven differentially with a sine wave, LVPECL, CMOS,

or LVDS. A clock duty cycle stabilizer allows high performance

at full speed with a wide range of clock duty cycles. The on-chip

reference eliminates the need for external decoupling and can

be adjusted by means of SPI control.

Various power-down and standby modes are supported. The

ADC typically consumes 150 mW per channel with the digital

link still in operation when standby operation is enabled.

FUNCTIONAL BLOCK DIAGRAM

AVDD

PDWN

DRVDD DRGND

VIN + A

VIN – A

VCM A

VIN + B

VIN – B

VCM B

VIN + C

VIN – C

VCM C

VIN + D

VIN – D

VCM D

RBIAS

TEMPOUT

AD9639

BUF SHA

PIPELINE

ADC

12

DOUT + A

CHANNEL A

DOUT – A

BUF SHA

PIPELINE

ADC

12

DOUT + B

CHANNEL B

DOUT – B

BUF SHA

PIPELINE

ADC

12

DOUT + C

CHANNEL C

DOUT – C

BUF SHA

PIPELINE

ADC

12

DOUT + D

CHANNEL D

DOUT – D

REFERENCE

SERIAL

PORT

DATA RATE

MULTIPLIER

PGM3

PGM2

PGM1

PGM0

RESET

SCLK SDI/ SDO CSB CLK+ CLK–

SDIO

Figure 1.

Fabricated on an advanced CMOS process, the AD9639 is avail-

able in a Pb-free/RoHS-compliant, 72-lead LFCSP package. It is

specified over the industrial temperature range of −40°C to +85°C.

PRODUCT HIGHLIGHTS

1. Four ADCs are contained in a small, space-saving package.

2. An on-chip PLL allows users to provide a single ADC

sampling clock; the PLL distributes and multiplies up to

produce the corresponding data rate clock.

3. The JESD204 coded data rate supports up to 4.2 Gbps

per channel.

4. The AD9639 operates from a single 1.8 V power supply.

5. Flexible synchronization schemes and programmable

mode pins are available.

6. An on-chip temperature sensor is included.

Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2009–2013 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

Free Datasheet http://www.datasheet4u.com/

1 page

Data Sheet

AD9639

DIGITAL SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, TMIN = −40°C, TMAX = +85°C, 1.25 V p-p differential input, AIN = −1.0 dBFS, DCS enabled, unless

otherwise noted.

Table 3.

Parameter1

CLOCK INPUTS (CLK+, CLK−)

Logic Compliance

Differential Input Voltage

Input Voltage Range

Temp

Full

Full

Full

Internal Common-Mode Bias

Input Common-Mode Voltage

High Level Input Voltage (VIH)

Low Level Input Voltage (VIL)

High Level Input Current (IIH)

Low Level Input Current (IIL)

Differential Input Resistance

Input Capacitance

LOGIC INPUTS (PDWN, CSB, SDI/SDIO,

SCLK, RESET, PGMx)2

Logic 1 Voltage

Full

Full

Full

Full

Full

Full

25°C

25°C

Full

Logic 0 Voltage

Full

Logic 1 Input Current (CSB)

Logic 0 Input Current (CSB)

Logic 1 Input Current

(PDWN, SDI/SDIO, SCLK,

RESET, PGMx)

Logic 0 Input Current

(PDWN, SDI/SDIO, SCLK,

RESET, PGMx)

Input Resistance

Input Capacitance

LOGIC OUTPUT (SDO)

Logic 1 Voltage

Full

Full

Full

Full

25°C

25°C

Full

Logic 0 Voltage

DIGITAL OUTPUTS (DOUT + x, DOUT − x)

Logic Compliance

Differential Output Voltage

Common-Mode Voltage

Full

Full

Full

AD9639BCPZ-170

Min Typ

Max

LVPECL/LVDS/CMOS

0.2 6

AVDD −

0.3

AVDD +

1.6

1.2

1.1 AVDD

1.2 3.6

0 0.8

−10 +10

−10 +10

16 20

24

4

0.8 ×

AVDD

0

−60

55

0.2 ×

AVDD

0

30

4

1.2 AVDD +

0.3

0 0.3

CML

0.8

DRVDD/2

AD9639BCPZ-210

Min Typ

Max

LVPECL/LVDS/CMOS

0.2 6

AVDD −

0.3

AVDD +

1.6

1.2

1.1 AVDD

1.2 3.6

0 0.8

−10 +10

−10 +10

16 20

24

4

0.8 ×

AVDD

0

−60

55

0.2 ×

AVDD

0

30

4

1.2 AVDD +

0.3

0 0.3

CML

0.8

DRVDD/2

Unit

V p-p

V

V

V

V

µA

µA

kΩ

pF

V

V

µA

µA

µA

µA

kΩ

pF

V

V

V

V

1 See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for definitions and details on how these tests were completed.

2 Specified for 13 SDI/SDIO pins on the same SPI bus.

Rev. B | Page 5 of 36

Free Datasheet http://www.datasheet4u.com/

5 Page

Data Sheet

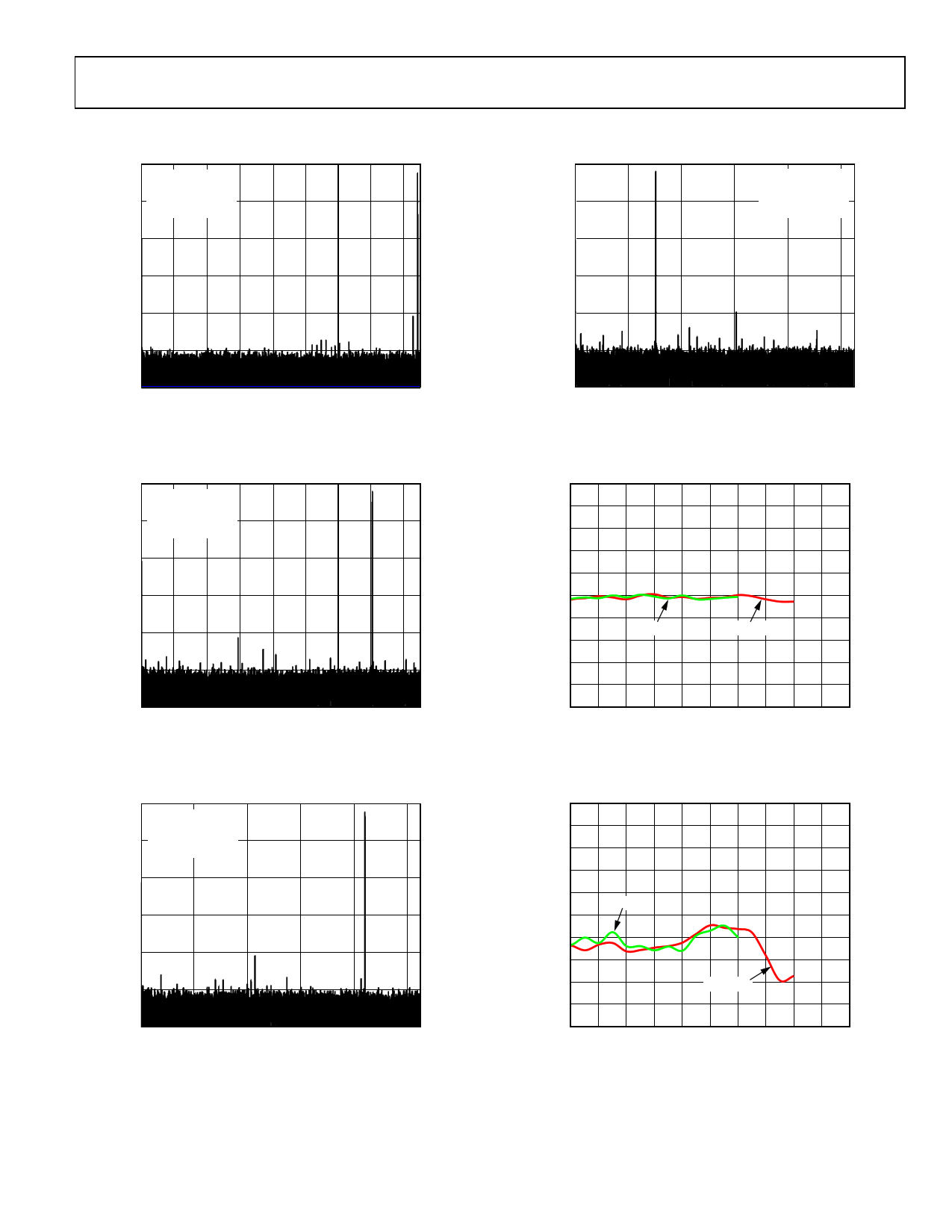

TYPICAL PERFORMANCE CHARACTERISTICS

0

AIN = –1.0dBFS

SNR = 64.88dB

–20 ENOB = 10.49 BITS

SFDR = 77.57dBc

–40

–60

–80

–100

–120

0 10 20 30 40 50 60 70 80

FREQUENCY (MHz)

Figure 4. Single-Tone 32k FFT with fIN = 84.3 MHz, fSAMPLE = 170 MSPS

0

AIN = –1.0dBFS

SNR = 63.95dB

–20 ENOB = 10.33 BITS

SFDR = 78.90dBc

–40

–60

–80

–100

–120

0 10 20 30 40 50 60 70 80

FREQUENCY (MHz)

Figure 5. Single-Tone 32k FFT with fIN = 240.3 MHz, fSAMPLE = 170 MSPS

0

AIN = –1.0dBFS

SNR = 64.65dB

–20 ENOB = 10.44 BITS

SFDR = 77.54dBc

–40

–60

–80

–100

–120

0

20 40 60 80

FREQUENCY (MHz)

100

Figure 6. Single-Tone 32k FFT with fIN = 84.3 MHz, fSAMPLE = 210 MSPS

AD9639

0

AIN = –1.0dBFS

SNR = 63.13dB

–20 ENOB = 10.19 BITS

SFDR = 76.07dBc

–40

–60

–80

–100

–120

0

20 40 60 80

FREQUENCY (MHz)

100

Figure 7. Single-Tone 32k FFT with fIN = 240.3 MHz, fSAMPLE = 210 MSPS

70

69

68

67

66

65

64

170MSPS

210MSPS

63

62

61

60

50 70 90 110 130 150 170 190 210 230 250

ENCODE (MSPS)

Figure 8. SNR vs. Encode, fIN = 84.3 MHz

90

88

86

84

82

170MSPS

80

78

76

74 210MSPS

72

70

50 70 90 110 130 150 170 190 210 230 250

ENCODE (MSPS)

Figure 9. SFDR vs. Encode, fIN = 84.3 MHz

Rev. B | Page 11 of 36

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 36 Páginas | |

| PDF Descargar | [ Datasheet AD9639.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD9630 | Low Distortion 750 MHz Closed-Loop Buffer Amp | Analog Devices |

| AD9631 | Wide Bandwidth Voltage Feedback Op Amps | Analog Devices |

| AD9632 | Wide Bandwidth Voltage Feedback Op Amps | Analog Devices |

| AD9633 | Serial LVDS 1.8 V ADC | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |