|

|

PDF MAX1122 Data sheet ( Hoja de datos )

| Número de pieza | MAX1122 | |

| Descripción | 170Msps Analog-to-Digital Converter | |

| Fabricantes | Maxim Integrated | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX1122 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

19-3027; Rev 2; 8/08

1.8V, 10-Bit, 170Msps Analog-to-Digital Converter

with LVDS Outputs for Wideband Applications

General Description

The MAX1122 is a monolithic 10-bit, 170Msps analog-

to-digital converter (ADC) optimized for outstanding

dynamic performance at high IF frequencies up to

500MHz. The product operates with conversion rates of

up to 170Msps while consuming only 460mW.

At 170Msps and an input frequency of 100MHz, the

MAX1122 achieves a spurious-free dynamic range

(SFDR) of 72dBc. Its excellent signal-to-noise ratio

(SNR) of 57.5dB at 10MHz remains flat (within 1dB) for

input tones up to 500MHz. This makes the MAX1122

ideal for wideband applications such as digital predis-

tortion in cellular base-station transceiver systems.

The MAX1122 requires a single 1.8V supply. The ana-

log input is designed for either differential or single-

ended operation and can be AC- or DC-coupled. The

ADC also features a selectable on-chip divide-by-2

clock circuit, which allows the user to apply clock fre-

quencies as high as 340MHz. This helps to reduce the

phase noise of the input clock source. A differential

LVDS sampling clock is recommended for best perfor-

mance. The converter’s digital outputs are LVDS com-

patible, and the data format can be selected to be

either two’s complement or offset binary.

The MAX1122 is available in a 68-pin QFN with

exposed pad (EP) and is specified over the industrial

(-40°C to +85°C) temperature range.

For pin-compatible, higher speed versions of the

MAX1122, refer to the MAX1123 (210Msps) and the

MAX1124 (250Msps) data sheets. For a higher speed,

pin-compatible 8-bit version of the MAX1122, refer to

the MAX1121 data sheet.

Applications

Wireless and Wired Broadband Communication

Cable-Head End Systems

Digital Predistortion Receivers

Communications Test Equipment

Radar and Satellite Subsystems Antenna Array

Processing

Features

♦ 170Msps Conversion Rate

♦ SNR = 57.1dB/56.5dB at fIN = 100MHz/500MHz

♦ SFDR = 72dBc/63.5dBc at fIN = 100MHz/500MHz

♦ NPR = 53.7dB at fNOTCH = 28.8MHz

♦ Single 1.8V Supply

♦ 460mW Power Dissipation at 170Msps

♦ On-Chip Track-and-Hold and Internal Reference

♦ On-Chip Selectable Divide-by-2 Clock Input

♦ LVDS Digital Outputs with Data Clock Output

♦ Evaluation Kit Available (Order MAX1124EVKIT)

Ordering Information

PART

MAX1122EGK

*EP = Exposed pad.

TEMP RANGE

-40°C to +85°C

PIN-PACKAGE

68 QFN-EP*

TOP VIEW

Pin Configuration

68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52

AVCC 1

AGND 2

REFIO 3

REFADJ 4

AGND 5

AVCC 6

AGND 7

INP 8

INN 9

AGND 10

AVCC

AVCC

AVCC

AVCC

AGND

11

12

13

14

15

AGND 16

CLKDIV 17

EP

MAX1122

51 D6P

50 D6N

49 D5P

48 D5N

47 D4P

46 D4N

45 OGND

44 OVCC

43 DCLKP

42 DCLKN

41 OVCC

40 D3P

39 D3N

38 D2P

37 D2N

36 D1P

35 D1N

18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34

________________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

Free Datasheet http://www.datasheet4u.com/

1 page

1.8V, 10-Bit, 170Msps Analog-to-Digital Converter

with LVDS Outputs for Wideband Applications

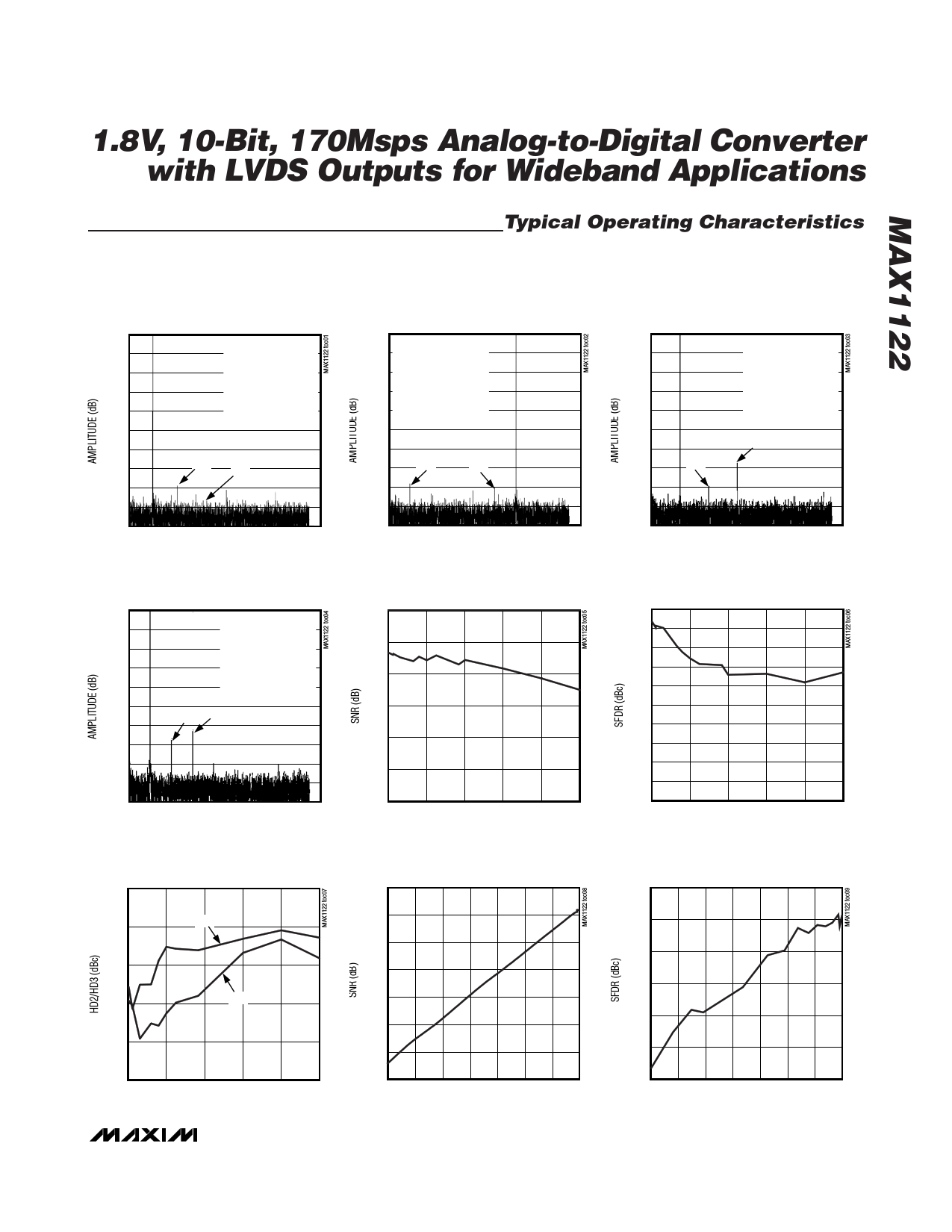

Typical Operating Characteristics

(AVCC = OVCC = 1.8V, VAGND = VOGND = 0, fSAMPLE = 170.0057MHz, -0.5dBFS; see TOCs for detailed information on test condi-

tions, differential input drive, differential sine-wave clock input drive, 0.1µF capacitor on REFIO, internal reference, digital output pins

differential RL = 100Ω, TA = +25°C.)

FFT PLOT (8192-POINT DATA RECORD,

COHERENT SAMPLING)

0

-10

fSAMPLE = 170.0057MHz

fIN = 11.5177MHz

-20 AIN = -0.5065dBFS

SNR = 57.7dB

-30 SFDR = 77.7dBc

-40 HD2 = -77.7dBc

HD3 = -86.3dBc

-50

-60

-70 HD2 HD3

-80

-90

-100

0

10 20 30 40 50 60 70 80 90

ANALOG INPUT FREQUENCY (MHz)

FFT PLOT (8192-POINT DATA RECORD,

COHERENT SAMPLING)

0

-10

fSAMPLE = 170.0057MHz

fIN = 500.516MHz

-20 AIN = -0.5155dBFS

SNR = 55.9dB

-30 SFDR = 63.5dBc

-40 HD2 = -68.6dBc

HD3 = -63.5dBc

-50

HD2 HD3

-60

-70

-80

-90

-100

0

10 20 30 40 50 60 70 80 90

ANALOG INPUT FREQUENCY (MHz)

FFT PLOT (8192-POINT DATA RECORD,

COHERENT SAMPLING)

0

-10

fSAMPLE = 170.0057MHz

fIN = 60.0374MHz

-20 AIN = -0.4795dBFS

SNR = 57.5dB

-30 SFDR = 77.7dBc

-40 HD2 = -79.8dBc

HD3 = -77.7dBc

-50

-60

-70 HD3 HD2

-80

-90

-100

0

10 20 30 40 50 60 70 80 90

ANALOG INPUT FREQUENCY (MHz)

SNR vs. ANALOG INPUT FREQUENCY

(fSAMPLE = 169.984MHz, AIN = -0.5dBFS)

59

58

57

56

55

54

53

0

100 200 300 400 500

fIN (MHz)

FFT PLOT (8192-POINT DATA RECORD,

COHERENT SAMPLING)

0

-10

fSAMPLE = 170.0057MHz

fIN = 183.5157MHz

-20 AIN = -0.4706dBFS

SNR = 56.7dB

-30 SFDR = 66.8dBc

-40 HD2 = -79.3dBc

HD3 = -66.8dBc

-50

HD3

-60

-70 HD2

-80

-90

-100

0

10 20 30 40 50 60 70 80 90

ANALOG INPUT FREQUENCY (MHz)

SFDR vs. ANALOG INPUT FREQUENCY

(fSAMPLE = 169.984MHz, AIN = -0.5dBFS)

80

75

70

65

60

55

50

45

40

35

30

0

100 200 300 400 500

fIN (MHz)

HD2/HD3 vs. ANALOG INPUT FREQUENCY

(fSAMPLE = 169.984MHz, AIN = -0.5dBFS)

-50

SNR vs. ANALOG INPUT AMPLITUDE

(fSAMPLE = 170.0057MHz, fIN = 60.0374MHz)

62

SFDR vs. ANALOG INPUT AMPLITUDE

(fSAMPLE = 170.0057MHz, fIN = 60.0374MHz)

80

-60 HD3

-70

-80 HD2

-90

57

52

47

42

37

32

75

70

65

60

55

-100

0

100 200 300 400 500

fIN (MHz)

27

-28

-24 -20 -16 -12 -8 -4

ANALOG INPUT AMPLITUDE (dBFS)

0

50

-28

-24 -20 -16 -12 -8 -4

ANALOG INPUT AMPLITUDE (dBFS)

0

_______________________________________________________________________________________ 5

Free Datasheet http://www.datasheet4u.com/

5 Page

1.8V, 10-Bit, 170Msps Analog-to-Digital Converter

with LVDS Outputs for Wideband Applications

SAMPLING EVENT

INN

SAMPLING EVENT

SAMPLING EVENT

SAMPLING EVENT

INP

CLKN

CLKP

DCLKP

DCLKN

tAD

N

tCPDL

N-8

tPDL

N+1

tLATENCY

N-7

tCH

N+8

tCL

N+9

N

tCPDL - tPDL

N+1

D0P/N–D9P/N

ORP/N

N-8

N-7 N-1

N

tCPDL - tPDL ~ 0.4 x tSAMPLE with tSAMPLE = 1/fSAMPLE

NOTE: THE ADC SAMPLES ON THE RISING EDGE OF CLKP. THE RISING EDGE OF DCLKP CAN BE USED TO EXTERNALLY LATCH THE OUTPUT DATA.

Figure 4. System and Output Timing Diagram

N+1

Analog Inputs (INP, INN)

INP and INN are the fully differential inputs of the

MAX1122. Differential inputs usually feature good rejec-

tion of even-order harmonics, which allows for enhanced

AC performance as the signals are progressing through

the analog stages. The MAX1122 analog inputs are self-

biased at a common-mode voltage of 1.4V and allow a

differential input voltage swing of 1.25VP-P. Both inputs

are self-biased through 2.2kΩ resistors, resulting in a

typical differential input resistance of 4.4kΩ. It is recom-

mended to drive the analog inputs of the MAX1122 in

AC-coupled configuration to achieve best dynamic per-

formance. See the AC-Coupled Analog Inputs section for

a detailed discussion of this configuration.

On-Chip Reference Circuit

The MAX1122 features an internal 1.23V bandgap ref-

erence circuit (Figure 3), which, in combination with an

internal reference-scaling amplifier, determines the full-

scale range of the MAX1122. Bypass REFIO with a

0.1µF capacitor to AGND. To compensate for gain

errors or increase the ADC’s full-scale range, the volt-

age of this bandgap reference can be indirectly adjust-

ed by adding an external resistor (e.g., 100kΩ trim

potentiometer) between REFADJ and AGND or REFADJ

and REFIO. See the Applications Information section for

a detailed description of this process.

OVCC

VOP

2.2kΩ

VON

2.2kΩ

Figure 5. Simplified LVDS Output Architecture

OGND

Clock Inputs (CLKP, CLKN)

Designed for a differential LVDS clock input drive, it is

recommended to drive the clock inputs of the MAX1122

with an LVDS-compatible clock to achieve the best

______________________________________________________________________________________ 11

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet MAX1122.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX11200 | Delta- Sigma ADCs | Maxim Integrated Products |

| MAX11201 | Delta- Sigma ADC | Maxim Integrated Products |

| MAX11202 | Delta- Sigma ADC with 2-Wire Serial Interface | Maxim Integrated Products |

| MAX11203 | Delta- Sigma ADCs | Maxim Integrated Products |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |