|

|

PDF ADL5303 Data sheet ( Hoja de datos )

| Número de pieza | ADL5303 | |

| Descripción | Low Cost Logarithmic Converter | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADL5303 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

Data Sheet

FEATURES

Optimized for fiber optic photodiode interfacing

8 full decades of range

Law conformance: 0.1 dB from 1 nA to 1 mA

Single-supply operation: 3.0 V to 5.5 V

Complete and temperature stable

Accurate laser trimmed scaling

Logarithmic slope of 10 mV/dB (at the VLOG pin)

Basic logarithmic intercept at 100 pA

Easy adjustment of slope and intercept

Output bandwidth of 10 MHz, 15 V/μs slew rate

Miniature 16-lead package (LFCSP)

Low power: ~4.5 mA quiescent current (enabled)

APPLICATIONS

High accuracy optical power measurement

Wide range baseband log compression

Versatile detector for APC loops

160 dB Range 100 pA to 10 mA

Low Cost Logarithmic Converter

ADL5303

SIMPLIFIED BLOCK DIAGRAM

VPDB

5

2 VSUM

IPD

3

INPT

VSUM

4

VPS2

10

PDB

PWDN

16

BIAS

VPS1

12

ADL5303

VREF

VREF

6

~10kΩ

0.5V

VLOG

TEMPERATURE

8

COMPENSATION

5kΩ

BFIN

9

BFNG

13

15

GND

7

ACOM

14

GND

Figure 1.

11

VOUT

GENERAL DESCRIPTION

The ADL5303 is a monolithic logarithmic detector optimized

for the measurement of low frequency signal power in fiber

optic systems and offers a large dynamic range in a versatile and

easily used form. Wide measurement range and accuracy are

achieved using proprietary design and precise laser trimming.

The ADL5303 requires only a single positive supply, VPS, of 5 V.

When using low supply voltages, the log slope can be altered to

fit the available span. Low quiescent current and chip disable

facilitate use in battery-operated applications.

The input current, IPD, flows in the collector of an optimally

scaled NPN transistor, connected in a feedback path around a

low offset JFET amplifier. The current summing input node

operates at a constant voltage, independent of current, with

a default value of 0.5 V; this may be adjusted over a wide range.

An adaptive biasing scheme is provided for reducing photo-

diode dark current at very low light input levels. The VPDB pin

applies approximately 0.1 V reverse bias across the photodiode

for IPD = 100 pA, rising linearly to 2.0 V of reverse bias at IPD =

10 mA to improve response time at higher power levels. The

input pin INPT is flanked by the VSUM guard pins that track

the voltage at the summing node. Connecting the exposed pad

http://www.DataSheet4U.net/

of the device to the VSUM pins provides a continuous guard to

minimize leakage into the INPT pin.

The default value of the logarithmic slope at the VLOG output

is set by an internal 5 kΩ resistor. Logarithmic slope can be

lowered with an external shunt resistor or increased using the

buffer and a pair of external feedback resistors. The addition of

a capacitor at the VLOG pin provides a simple low-pass filter.

The intermediate voltage, VLOG, is buffered in an output stage

that can swing to within about 100 mV of ground and the posi-

tive supply, VPS, and provides a peak current drive capacity of

±20 mA. An on-board 2 V reference is provided to facilitate

the repositioning of the intercept. The incremental bandwidth

of a translinear logarithmic amplifier inherently diminishes

for small input currents. At IPD =1 nA, the bandwidth of the

ADL5303 is approximately 2 kHz increasing in proportion to

IPD up to a maximum value of 10 MHz.

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

©2013 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

datasheet pdf - http://www.DataSheet4U.net/

1 page

Data Sheet

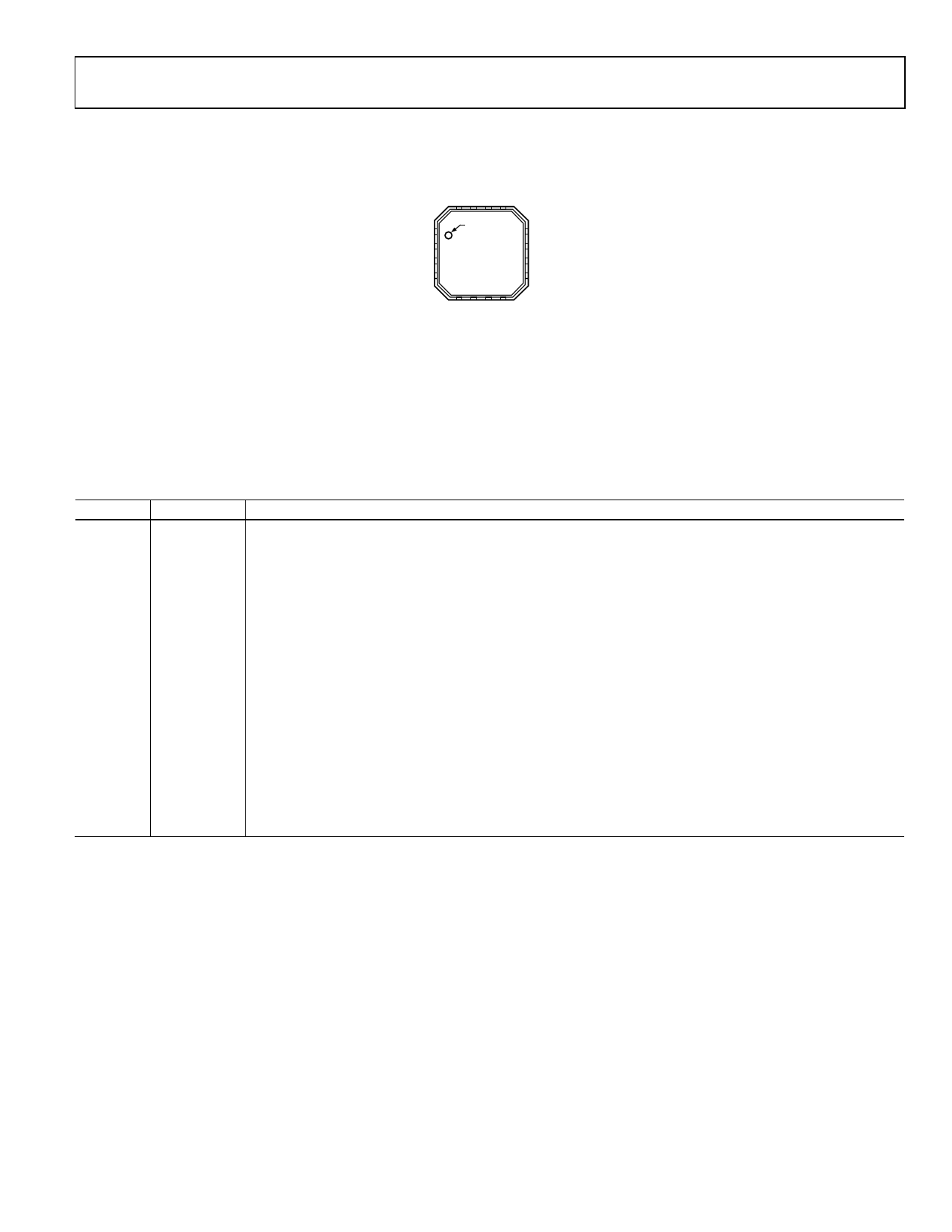

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

ADL5303

NC 1

VSUM 2

INPT 3

VSUM 4

PIN 1

INDICATOR

ADL5303

TOP VIEW

(Not to Scale)

12 VPS1

11 VOUT

10 VPS2

9 BFIN

NOTES

1. PINS LABELED NC CAN BE ALLOWED TO FLOAT, BUT

IT IS BETTER TO CONNECT THESE PINS TO GROUND.

AVOID ROUTING HIGH SPEED SIGNALS THROUGH

THESE PINS BECAUSE NOISE COUPLING MAY RESULT.

2. EXPOSED PAD. CONNECT THE EXPOSED PAD TO THE

VSUM PINS TO PROVIDE LOW LEAKAGE GUARD.

Figure 2. Pin Configuration

Table 3. Pin Function Descriptions

Pin No. Mnemonic Description

1 NC

Pins labeled NC can be allowed to float, but it is better to connect these pins to ground. Avoid routing high

speed signals through these pins because noise coupling may result.

2, 4 VSUM

Guard Pins. VSUM is used to shield the INPT current line.

3 INPT Photodiode Current Input. Connect this pin to the photodiode anode (the photo current flows toward INPT).

5

VPDB

Photodiode Biaser Output. Connect this pin to the photodiode cathode when using adaptive bias control;

otherwise, leave this pin floating.

6 VREF Voltage Reference Output of 2 V. http://www.DataSheet4U.net/

7

ACOM

Analog Reference Ground.

8

VLOG

Output of the Logarithmic Front-End Processor. ROUT = 5 kΩ to ground.

9 BFIN Buffer Amplifier Noninverting Input (High Impedance).

10 VPS2

Positive Supply, VPS (3.0 V to 5.5 V).

11 VOUT Buffer Output; Low Impedance.

12 VPS1

Positive Supply, VPS (3.0 V to 5.5 V).

13 BFNG Buffer Amplifier Inverting Input.

14, 15

GND

Power Supply Ground Connection.

16

PWDN

Power-Down Control Input. Device is active when PWDN is taken low.

17 EPAD

Exposed Pad. Connect the exposed pad to the VSUM pins to provide low leakage guard.

Rev. 0 | Page 5 of 24

datasheet pdf - http://www.DataSheet4U.net/

5 Page

Data Sheet

For an input of 1 nA, SNSD evaluates to almost 0.5 μV/√Hz;

assuming a 20 kHz bandwidth at this current, the integrated

noise voltage is 70 μV rms. However, this calculation is not

complete. The basic scaling of the VBE is approximately

3 mV/dB; translated to 10 mV/dB, the noise predicted by

Equation 7 must be multiplied by approximately 3.33. The

additive noise effects associated with the reference transistor,

Q2, and the temperature compensation circuitry must also be

included. The final voltage noise spectral density presented at

the VLOG pin varies inversely with IPD, but is not a simple

ADL5303

square root relationship. Figure 10 shows the measured noise

spectral density vs. frequency at the VLOG output, for the same

nine-decade spaced values of IPD.

CHIP ENABLE

Power down the ADL5303 by taking the PWDN pin to a high

logic level. The residual supply current in the disabled mode is

typically 60 μA.

http://www.DataSheet4U.net/

Rev. 0 | Page 11 of 24

datasheet pdf - http://www.DataSheet4U.net/

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet ADL5303.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADL5303 | Low Cost Logarithmic Converter | Analog Devices |

| ADL5304 | Logarithmic Converter | Analog Devices |

| ADL5306 | 60 dB Range (100 nA to 100 UA) Low Cost Logarithmic Converter | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |