|

|

PDF 92HD95 Data sheet ( Hoja de datos )

| Número de pieza | 92HD95 | |

| Descripción | FOUR CHANNEL HD AUDIO CODEC | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 92HD95 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DATASHEET

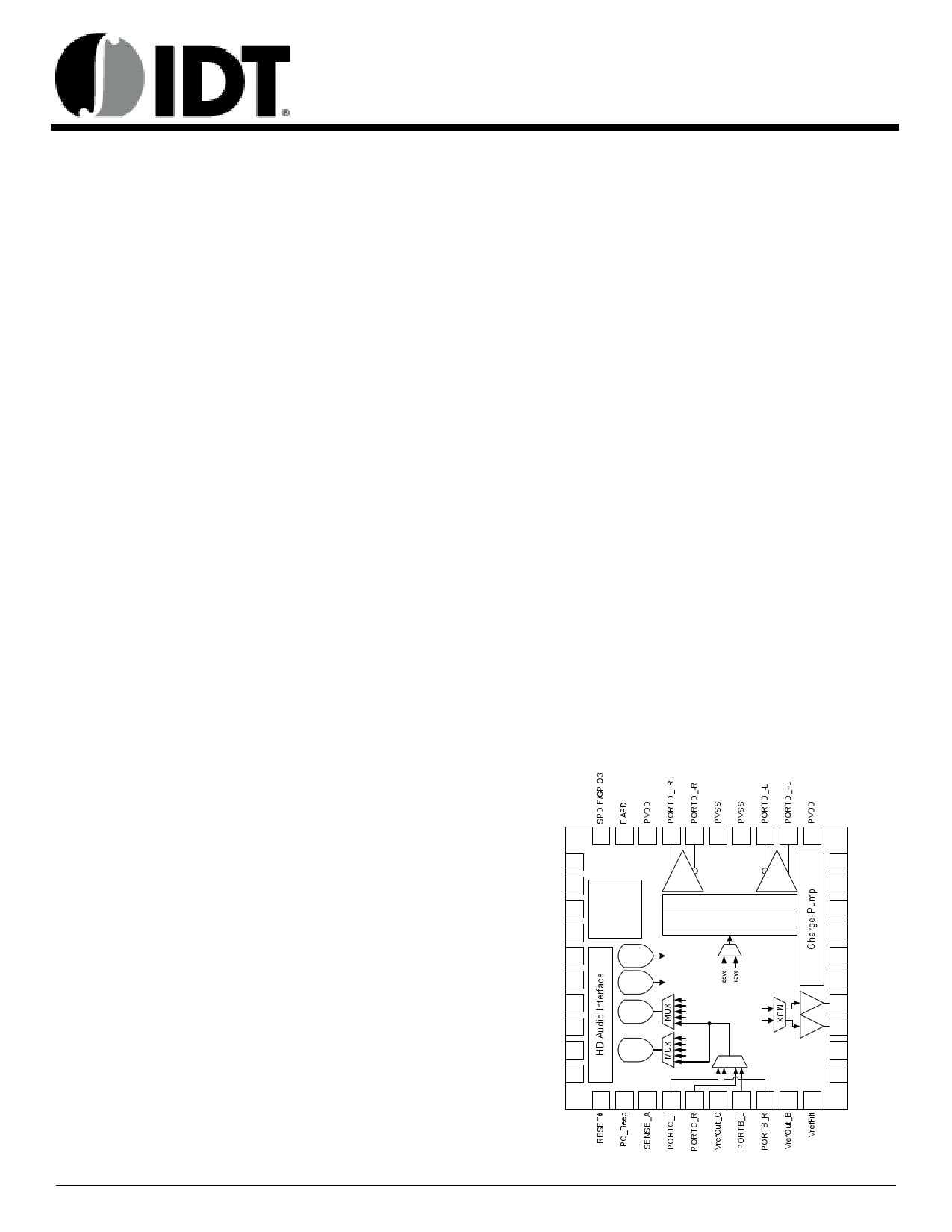

FOUR CHANNEL HD AUDIO CODEC

OPTIMIZED FOR LOW POWER/LOW COST

DESCRIPTION

The 92HD95 is a low power optimized, high fidelity,

4-channel audio codec compatible with Intel’s High Defini-

tion (HD) Audio Interface. The 92HD95 provides high qual-

ity, HD Audio capability to notebook and desktop PC

applications.

FEATURES

• 4 Channel (2 stereo DACs, 2 stereo ADCs) with

24-bit resolution

• Microsoft WLP premium logo compliant

• 2W(4ohm)/1W(8ohm) Class-D Stereo BTL Amplifier

at <1% THD+N and 5V

• Selectable frequency hardware high-pass filter for

speaker protection.

• 10 band hardware parametric equalizer (5 bands per

channel) for speaker optimization in ALL operating

scenarios

• Hardware compressor limiter allows higher average

volume level without resonances or damage to

speakers.

• Integrated Class-G true capless stereo headphone

amplifier with charge pump/LDO

• 4 analog ports with port presence detect (3 single

ended, 1 BTL)

• Combo Jack Support allowing for dual-function

headphone and headset detection

• 2 Voltage adjustable VREF_Out pins for

microphone bias

• 2 Digital microphone inputs (4 mic support)

• Microphone Mute Input

• Selectable 1.5V and 3.3V HDA signaling

• Internal DVDD LDO voltage regulator

• Supports Runtime D3 (RTD3) low power mode

• Capable of MSLync Compliance

• Full HDA015-B and EuP low power support

• Audio inactivity transitions codec from D0 to D3 low

power mode

• Resume from D3 to D0 with audio activity in < 10 msec

• D3 to D0 transition with < -65dB pop/click

• Port presence detect in D3 with or without bit clock

• PC beep wake up in D3

• Additional vendor specific modes for even lower power

• 3.3 V analog power supply

• Digital and Analog PC Beep to all outputs

• 40-pin 5mm x 5mm QFN RoHS package

92HD95

SOFTWARE SUPPORT

• Intuitive IDT HD Sound graphical user interface

that allows configurability and preference settings

• Output Path Processing

• 12 band fully parametric equalizer

• Compressor/limiter allows higher average volume level

without resonances or damage to speakers.

• Enables improved voice articulation

• Constant, system-level effects tuned to optimize a

particular platform can be combined with user-mode

“presets” tailored for specific acoustical environments

and applications

• System-level effects automatically disabled when

external audio connections made

• Input Path Processing

• 2 band fully parametric equalizer to allow for shaping of

microphone response

• Compressor/limiter allows higher average volume level

• Available near-field and far-field voice capture

algorithms to support conference room/lecture hall

applications

• Microphone Beam Forming, Acoustic Echo

Cancellation, and Noise Suppression

• IDT APO wrapper

www.DataSheet.net/

•

Enables multiple APOs to be used with the IDT Driver

• Dynamic Stream Switching

• Improved multi-streaming (Real Time Communication)

user experience with less support calls

• Broad 3rd party branded software including

Creative, Dolby, DTS, Waves, Sonic Focus & SRS

40 39 38 37 36 35 34 33 32 31

DVDD_LV 1

30 AVDD2

DMIC_CLK/GPIO 1 2

DMIC_0/GPIO 2 3

DMIC_1/GPIO 0 4

Digital Mic

Interface

BTL BTL

Digital PWM controller

Stereo 5-band EQ

Highpass Filter

29 CPVreg

28 FCap1

27 FCap2

SDATA_OUT 5

BITCLK 6

DVDDIO 7

SDATA_IN 8

DVDD 9

SYNC 10

Stereo

DAC 0

Stereo

DAC 1

Stereo

ADC0

Stereo

ADC1

DAC0

DAC1

DMIC0

DMIC1

DAC0

DAC1

DMIC0

DMIC1

DAC0

DAC1

MUX

DAC0

DAC1

MUX

26 VNeg

25 VPos

HP 24 PORTA_R

HP 23 PORTA_L

22 AVDD1

21 CAP2

11 12 13 14 15 16 17 18 19 20

©2012 INTEGRATED DEVICE TECHNOLOGY, INC.

1

V 0.91 06/12

92HD95

Datasheet pdf - http://www.DataSheet4U.co.kr/

1 page

92HD95

Four Channel HD Audio Codec

7.14.4. ADC1 (NID = 13h): ProcState ........................................................................................151

7.14.5. ADC1 (NID = 13h): PwrState .........................................................................................152

7.14.6. ADC1 (NID = 1Bh): CnvtrID ...........................................................................................153

7.15. ADC0Mux (NID = 14h): WCap .....................................................................................................153

7.15.1. ADC0Mux (NID = 14h): ConLst ......................................................................................155

7.15.2. ADC0Mux (NID = 14h): ConLstEntry4 ...........................................................................155

7.15.3. ADC0Mux (NID = 14h): ConLstEntry0 ...........................................................................156

7.15.4. ADC0Mux (NID = 14h): OutAmpCap .............................................................................156

7.15.5. ADC0Mux (NID = 14h): OutAmpLeft ..............................................................................157

7.15.6. ADC0Mux (NID = 14h): OutAmpRight ...........................................................................157

7.15.7. ADC0Mux (NID = 14h): ConSelectCtrl ...........................................................................158

7.15.8. ADC0Mux (NID = 14h): PwrState ..................................................................................158

7.15.9. ADC0Mux (NID = 14h): EAPDBTLLR ............................................................................159

7.16. ADC1Mux (NID = 15h): WCap .....................................................................................................160

7.16.1. ADC1Mux (NID = 15h): ConLst ......................................................................................161

7.16.2. ADC1Mux (NID = 15h): ConLstEntry4 ...........................................................................162

7.16.3. ADC1Mux (NID = 15h): ConLstEntry0 ...........................................................................162

7.16.4. ADC1Mux (NID = 15h): OutAmpCap .............................................................................163

7.16.5. ADC1Mux (NID = 15h): OutAmpLeft ..............................................................................163

7.16.6. ADC1Mux (NID = 15h): OutAmpRight ...........................................................................164

7.16.7. ADC1Mux (NID = 15h): ConSelectCtrl ...........................................................................164

7.16.8. ADC1Mux (NID = 15h): PwrState ..................................................................................165

7.16.9. ADC1Mux (NID = 15h): EAPDBTLLR ............................................................................166

7.17. PortMux (NID = 16h): WCap ........................................................................................................166

7.17.1. PortMux (NID = 16h): ConLst .........................................................................................168

7.17.2. PortMux (NID = 16h): ConLstEntry0 ..............................................................................168

7.17.3. PortMux (NID = 16h): ConSelectCtrl ..............................................................................169

7.17.4. PortMux (NID = 16h): PwrState .....................................................................................169

7.18. SPDIFOut0 (NID = 17h): WCap ...................................................................................................170

7.18.1. SPDIFOut0 (NID = 17h): PCMCap ................................................................................171

7.18.2. SPDIFOut0 (NID = 17h): StreamCap ........www..Data.Sheet..net/.................................................................. 173

7.18.3. SPDIFOut0 (NID = 17h): OutAmpCap ...........................................................................173

7.18.4. SPDIFOut0 (NID = 17h): Cnvtr ......................................................................................174

7.18.5. SPDIFOut0 (NID = 17h): OutAmpLeft ............................................................................175

7.18.6. SPDIFOut0 (NID = 17h): OutAmpRight .........................................................................176

7.18.7. SPDIFOut0 (NID = 1Dh): PwrState ................................................................................176

7.18.8. SPDIFOut0 (NID = 17h): CnvtrID ...................................................................................177

7.18.9. SPDIFOut0 (NID = 17h): DigCnvtr .................................................................................178

7.19. Dig0Pin (NID = 18h): WCap .........................................................................................................179

7.19.1. Dig0Pin (NID = 18h): PinCap .........................................................................................180

7.19.2. Dig0Pin (NID = 18h): ConLst .........................................................................................181

7.19.3. Dig0Pin (NID = 18h): ConLstEntry0 ...............................................................................182

7.19.4. Dig0Pin (NID = 18h): PwrState ......................................................................................182

7.19.5. Dig0Pin (NID = 18h): PinWCntrl .....................................................................................183

7.19.6. Dig0Pin (NID = 18h): UnsolResp ..................................................................................184

7.19.7. Dig0Pin (NID = 18h): ChSense ......................................................................................184

7.19.8. Dig0Pin (NID = 18h): ConfigDefault ...............................................................................185

7.20. DigBeep (NID = 19h): WCap .......................................................................................................187

7.20.1. DigBeep (NID = 19h): OutAmpCap ................................................................................188

7.20.2. DigBeep (NID = 19h): OutAmpLeft ................................................................................189

7.20.3. DigBeep (NID = 19h): PwrState .....................................................................................190

7.20.4. DigBeep (NID = 19h): Gen .............................................................................................190

7.20.5. DigBeep (NID = 19h): Gain ............................................................................................191

7.21. AdvancedFunctions (NID = 1Ah): WCap .....................................................................................191

7.21.1. AdvancedFunctions (NID = 1Ah): Cntrl0 ........................................................................193

7.21.2. AdvancedFunctions (NID = 1Ah): Cntrl1 ........................................................................193

7.21.3. AdvancedFunctions (NID = 1Ah): Cntrl2 ........................................................................194

7.21.4. AdvancedFunctions (NID = 1Ah): Cntrl3 ........................................................................194

8. PINOUT AND PACKAGING .................................................................................................. 208

IDT CONFIDENTIAL

©2012 INTEGRATED DEVICE TECHNOLOGY, INC.

5

V 0.91 06/12

92HD95

Datasheet pdf - http://www.DataSheet4U.co.kr/

5 Page

92HD95

Four Channel HD Audio Codec

AFG

Power

State

D0-D2

D3

D3cold

D4

D5

Input Output Used as output

Enable Enable for DAC/Mixer

Used as output

for analog

PC_Beep

Used as

input for

ADC, mixer

Port Behavior

1 1 Don't care Don't care

Yes Not allowed. Port is active as input.

No

Not allowed. Inactive (Power Down) - Port keeps

output coupling caps charged if port uses caps.

10

NA

NA Yes

Active - Port enabled as input

10

NA

NA

No

Inactive (Power Down) - Port keeps output coupling

caps charged if port uses caps.

currently used by DAC, mixer,

01

beep, or is traditional line or

headphone output

NA

0

1

not currently used by DAC, mixer,

beep and is capless HP/BTL port

Active - Port enabled as output

Inactive (Power Down)

00

NA

NA

NA

Inactive (Power Down) - Port keeps output coupling

caps charged if port uses caps.

11

NA

NA

Don't care

Not allowed. Inactive (Power Down) - Port keeps

output coupling caps charged if port uses caps.

10

NA

NA

Don't care

Inactive (Power Down) - Port keeps output coupling

caps charged if port uses caps.

0

1

currently used by DAC, mixer,

beep, or is traditional line or

headphone output

Don't care

Low power state. If enabled, Beep will output from

the port

0

1

not currently used by DAC, mixer,

beep and is capless HP/BTL port

Don't carewww.DataSheet.net/

Inactive (Power Down)

00

NA

NA

Don't care

Inactive (Power Down) - Port keeps output coupling

caps charged if port uses caps.

--

Inactive (lower power) - Port keeps output coupling

caps charged if port uses caps.

--

Inactive (lower power) - Port keeps output coupling

caps charged if port uses caps.

--

Off - Charge on coupling caps (if used) will not be

maintained.

Table 2. Analog Output Port Behavior

2.1.2.

Vref_Out

Ports B & C support Vref_Out pins for biasing electret cartridge microphones. Settings of 80%

AVDD, 50% AVDD, GND, and Hi-Z are supported. Attempting to program a pin widget control with a

reserved or unsupported value will cause the associated Vref_Out pin to assume a Hi-Z state and

the pin widget control Vref_En field will return a value of ‘000’ (Hi-Z) when read.

2.1.3.

Jack Detect

Plugs inserted to a jack on Ports A, B, C & SPDIFOUT are detected using SENSE_A. Per

HDA015-B, the detection circuit operates when the CODEC is in D0 - D3 and can also operate if

both the CODEC and Controller are in D3 (no bus clock.) Jack detection requires that all supplies

IDT CONFIDENTIAL

©2012 INTEGRATED DEVICE TECHNOLOGY, INC.

11

V 0.91 06/12

92HD95

Datasheet pdf - http://www.DataSheet4U.co.kr/

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 92HD95.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 92HD90 | SINGLE CHIP PC AUDIO SYSTEM | IDT |

| 92HD91 | SINGLE CHIP PC AUDIO SYSTEM | IDT |

| 92HD92 | SINGLE CHIP PC AUDIO SYSTEM | IDT |

| 92HD93 | SINGLE CHIP PC AUDIO SYSTEM | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |