|

|

PDF QS5919T Data sheet ( Hoja de datos )

| Número de pieza | QS5919T | |

| Descripción | LOW SKEW TTL PLL CLOCK DRIVER | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de QS5919T (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

www.DataSheet.co.kr

QS5919T

LOW SKEW TTL PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

LOW SKEW TTL PLL

CLOCK DRIVER WITH

INTEGRATED LOOP FILTER

INDUSTRIALTEMPERATURERANGE

QS5919T

FEATURES:

• 5V operation

• Low noise TTL level outputs

• < 350ps output skew, Q0–Q4

• 2xQ output, Q outputs, Q output, Q/2 output

• Outputs 3-state and reset while OE/RST low

• PLL disable feature for low frequency testing

• Internal loop filter RC network

• Functional equivalent to Motorola MC88915

• Positive or negative edge synchronization (PE)

• Balanced drive outputs ±24mA

• 160MHz maximum frequency (2xQ output)

• Available in QSOP and PLCC packages

DESCRIPTION

The QS5919T Clock Driver uses an internal phase locked loop (PLL)

to lock low skew outputs to one of two reference clock inputs. Eight outputs

are available: 2xQ, Q0-Q4, Q5, Q/2. Careful layout and design ensure <

350ps skew between the Q0-Q4, and Q/2 outputs. The QS5919T includes

an internal RC filter which provides excellent jitter characteristics and

eliminates the need for external components. Various combinations of

feedback and a divide-by-2 in the VCO path allow applications to be

customized for linear VCO operation over a wide range of input SYNC

frequencies. The PLL can also be disabled by the PLL_EN signal to allow

low frequency or DC testing. The LOCK output asserts to indicate when

phase lock has been achieved. The QS5919T is designed for use in high-

performance workstations, multi-board computers, networking hardware,

and mainframe systems. Several can be used in parallel or scattered

throughout a system for guaranteed low skew, system-wide clock distribu-

tion networks.

For more information on PLL clock driver products, see Application Note

AN-227.

FUNCTIONAL BLOCK DIAGRAM

O E /R S T

SYNC0

SYNC1

REF_SEL

0

LOCK PE FEEDBACK

1

PHASE

LOOP

DETECTOR

F IL T E R

VCO

PLL_EN

FREQ_SEL

01

1 /2 0

RDRDRDRDRDRDRD

Q Q Q Q Q Q QQ

Q/2 Q5 Q4 Q3 Q2

INDUSTRIAL TEMPERATURE RANGE

c 2000 Integrated Device Technology, Inc.

1

Q1 Q0

2xQ

SEPTEMBER 2000

DSC-5815/-

Datasheet pdf - http://www.DataSheet4U.net/

1 page

www.DataSheet.co.kr

QS5919T

LOW SKEW TTL PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

INDUSTRIALTEMPERATURERANGE

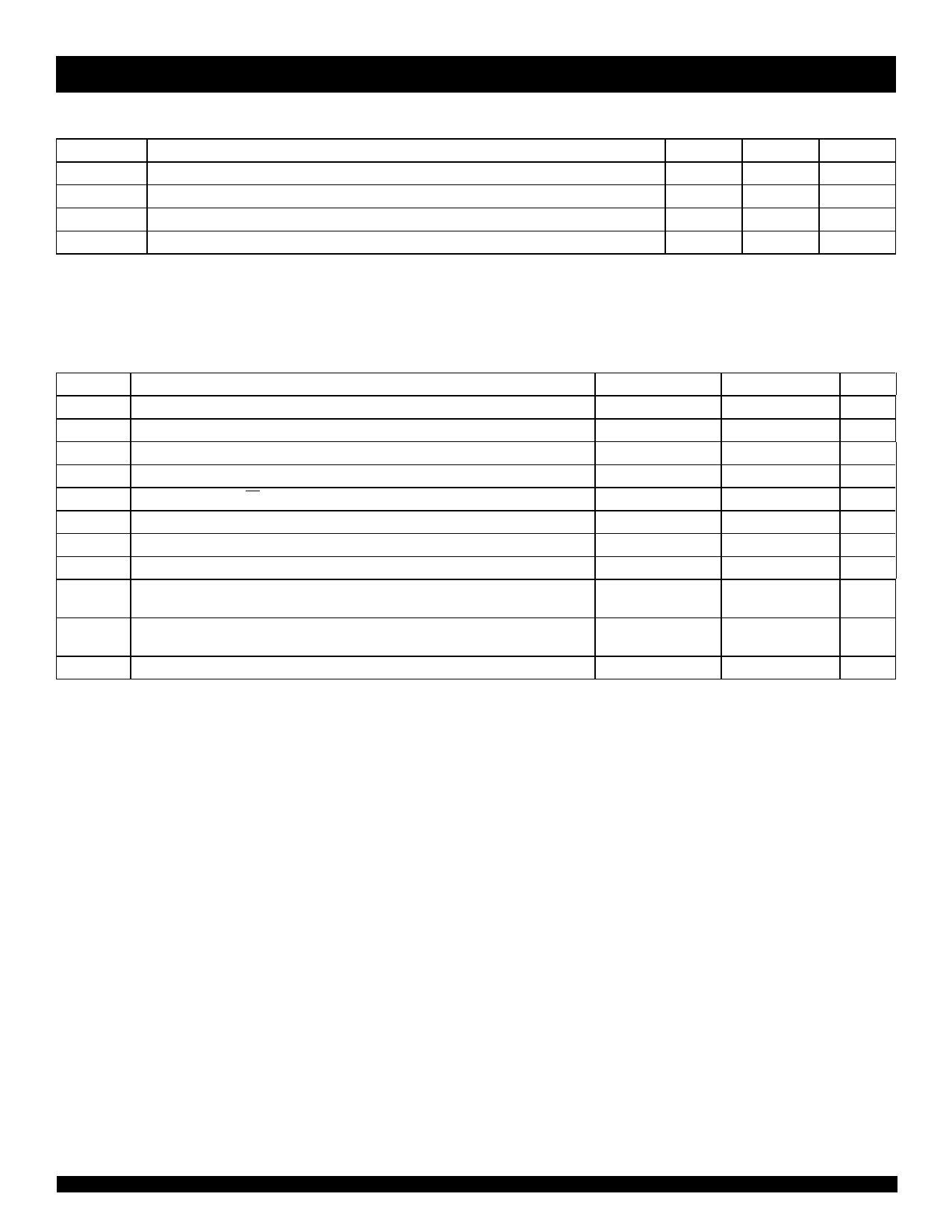

INPUT TIMING REQUIREMENTS

Symbol

tR, tF

FI

tPWC

DH

Description (1)

Maximum input rise and fall times, 0.8V to 2V

Input Clock Frequency, SYNC0, SYNC1 (1)

Input clock pulse, HIGH or LOW (2)

Input duty cycle (2)

Min. Max. Unit

— 3 ns

2.5

FMAX _2XQ

MHz

2 — ns

25 75 %

NOTES:

1. See Output Frequency and Frequency Selection tables for more detail on allowable SYNC input frequencies for different speed grades with

different FEEDBACK and FREQ_SEL combinations.

2. Where pulse witdh implied by DH is less than tWPC limit, tWPC limit applies

SWITCHING CHARACTERISTICS OVER OPERATING RANGE

Symbol

tSKR

tSKF

tSKALL

tPW

tPW

tJ

tPD

Parameter (1)

Output Skew Between Rising Edges, Q0-Q4 and Q/2 (2)

Output Skew Between Falling Edges, Q0-Q4 and Q/2 (2)

Output Skew, All Outputs (2,5)

Pulse Width, 2xQ output, >40MHz

Pulse Width, Q0-Q4, Q5, Q/2 outputs, 80MHz

Cycle-to-Cycle Jitter (4)

SYNC Input to Feedback Delay (6)

Min.

—

—

—

TCY/2 − 0.4

TCY/2 − 0.4

− 0.15

− 500

Max.

350

350

500

TCY/2 + 0.4

TCY/2 + 0.4

0.15

0

Unit

ps

ps

ps

ns

ns

ns

ps

tLOCK

tPZH

tPZL

tPHZ

tPLZ

tR, tF

SYNC to Phase Lock

Output Enable Time, OE/RST LOW to HIGH (3)

Output Enable Time, OE/RST HIGH to LOW (3)

Output Rise/Fall Times, 0.8V ∼ 2V

— 10 ms

0 7 ns

0 6 ns

0.3 1.5 ns

NOTES:

1. See Test Loads and Waveforms for test load and termination. Test circuit 1 is used for output enable/disable parameters. Test circuit 2 is used for all

other timing parameters.

2. Skew specifications apply under identical environments (loading, temperature, VCC, device speed grade).

3. Measured in open loop mode PLL_EN = 0.

4. Jitter is characterized with Q output at 20MHz. See FREQUENCY SELECTION TABLE for information on proper FREQ_SEL level for specified input

frequencies.

5. Skew measured at selected synchronization edge.

6. tPD measured at device inputs at 1.5V, Q output at 80MHz.

5

Datasheet pdf - http://www.DataSheet4U.net/

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet QS5919T.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| QS5919T | LOW SKEW TTL PLL CLOCK DRIVER | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |