|

|

PDF K9T1G08U0M Data sheet ( Hoja de datos )

| Número de pieza | K9T1G08U0M | |

| Descripción | 128M x 8 Bits NAND Flash Memory | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de K9T1G08U0M (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.net

K9T1G08U0M

Document Title

128M x 8 Bits NAND Flash Memory

Revision History

Revision No. History

0.0 Initial issue.

0.1 tR is changed. [Old : 12µs(Max.), New :15µs(Max.)]

0.2 CE must be held low during tR added.

0.3 1. Add the Protrusion/Burr value in WSOP1 PKG Diagram.

0.4 1. PKG(TSOP1, WSOP1) Dimension Change

0.5 1. Technical note is changed

2.Note1 of Program/Erase characteristics is added

Preliminary

FLASH MEMORY

Draft Date

Aug. 7th 2003

Oct. 20th 2003

Mar. 9th 2004

Apr. 24th 2004

May. 24th 2004

Oct. 25th 2004

Remark

Advanced

Preliminary

Preliminary

Preliminary

Preliminary

Preliminary

Note : For more detailed features and specifications including FAQ, please refer to Samsung’s Flash web site.

http://www.samsung.com/Products/Semiconductor/

The attached datasheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right

to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have

any questions, please contact the SAMSUNG branch office near you.

1

1 page

www.DataSheet4U.net

K9T1G08U0M

Preliminary

FLASH MEMORY

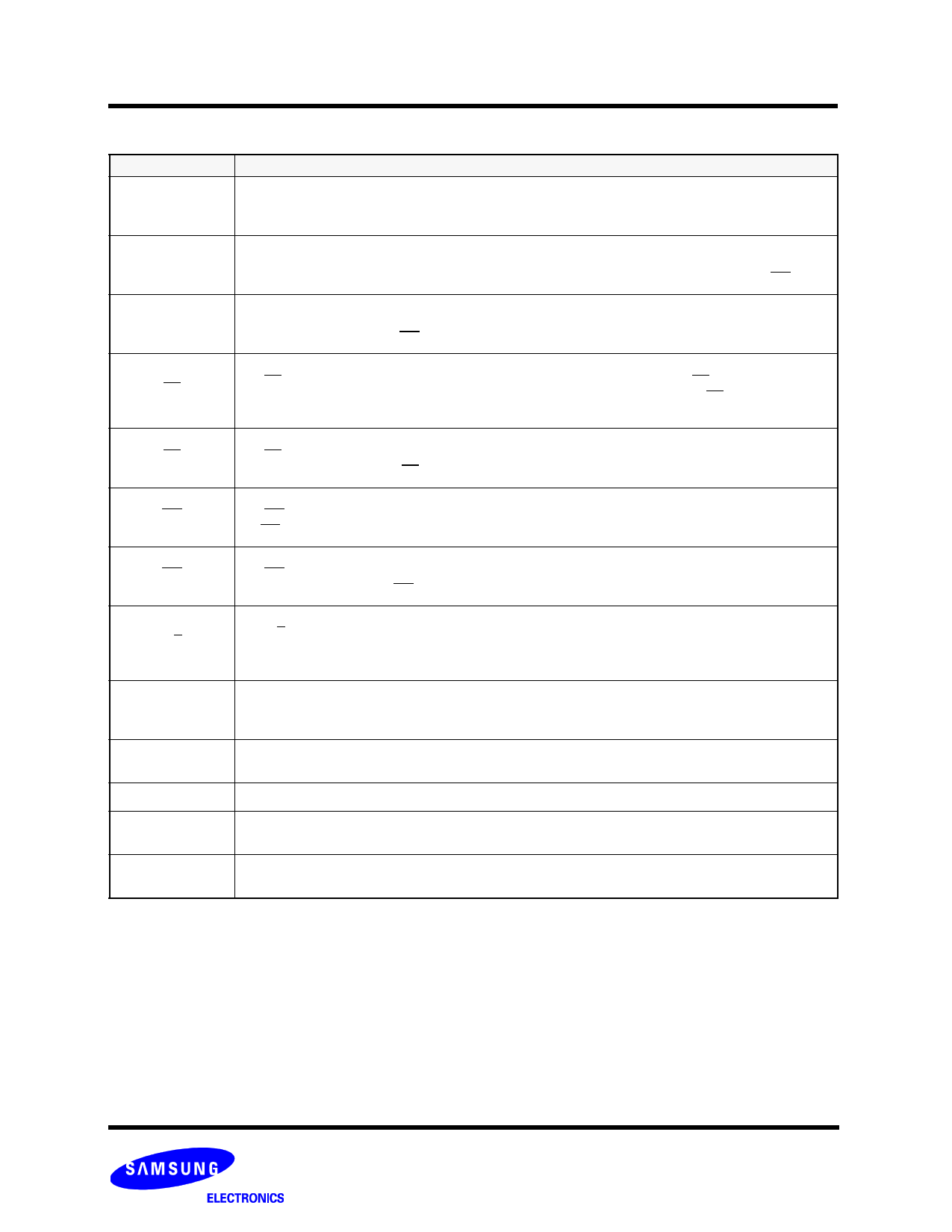

PIN DESCRIPTION

Pin Name

I/O0 ~ I/O7

Pin Function

DATA INPUTS/OUTPUTS

The I/O pins are used to input command, address and data, and to output data during read operations. The I/

O pins float to high-z when the chip is deselected or when the outputs are disabled.

COMMAND LATCH ENABLE

CLE The CLE input controls the activating path for commands sent to the command register. When active high,

commands are latched into the command register through the I/O ports on the rising edge of the WE signal.

ADDRESS LATCH ENABLE

ALE The ALE input controls the activating path for address to the internal address registers. Addresses are

latched on the rising edge of WE with ALE high.

CHIP ENABLE

CE

The CE input is the device selection control. When the device is in the Busy state, CE high is ignored, and

the device does not return to standby mode in program or erase opertion. Regarding CE control during read

operation, refer to ’Page read’ section of Device operation .

READ ENABLE

RE The RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid

tREA after the falling edge of RE which also increments the internal column address counter by one.

WRITE ENABLE

WE The WE input controls writes to the I/O port. Commands, address and data are latched on the rising edge of

the WE pulse.

WRITE PROTECT

WP The WP pin provides inadvertent write/erase protection during power transitions. The internal high voltage

generator is reset when the WP pin is active low.

READY/BUSY OUTPUT

R/B

The R/B output indicates the status of the device operation. When low, it indicates that a program, erase or

random read operation is in process and returns to high state upon completion. It is an open drain output and

does not float to high-z condition when the chip is deselected or when outputs are disabled.

VccQ

OUTPUT BUFFER POWER

VCCQ is the power supply for Output Buffer.

VccQ is internally connected to Vcc, thus should be biased to Vcc.

Vcc

POWER

VCC is the power supply for device.

Vss GROUND

N.C

NO CONNECTION

Lead is not internally connected.

DNU

DO NOT USE

Leave it disconnected.

NOTE : Connect all VCC and VSS pins of each device to common power supply outputs.

Do not leave VCC or VSS disconnected.

5

5 Page

www.DataSheet4U.net

K9T1G08U0M

Preliminary

FLASH MEMORY

AC Timing Characteristics for Command / Address / Data Input

CLE Set-up Time

CLE Hold Time

CE Setup Time

CE Hold Time

WE Pulse Width

ALE Setup Time

ALE Hold Time

Data Setup Time

Data Hold Time

Write Cycle Time

WE High Hold Time

Parameter

Symbol

tCLS

tCLH

tCS

tCH

tWP

tALS

tALH

tDS

tDH

tWC

tWH

Min

0

5

0

5

25 (1)

0

5

20

5

45

15

NOTE :

1. If tCS is set less than 10ns, tWP must be minimum 35ns, otherwise, tWP may be minimum 25ns.

Max Unit

- ns

- ns

.- ns

- ns

- ns

- ns

- ns

- ns

- ns

- ns

- ns

AC Characteristics for Operation

Parameter

Data Transfer from Cell to Register

ALE to RE Delay

CLE to RE Delay

Ready to RE Low

RE Pulse Width

WE High to Busy

Read Cycle Time

CE Access Time

RE Access Time

RE High to Output Hi-Z

CE High to Output Hi-Z

RE or CE High to Output hold

RE High Hold Time

Output Hi-Z to RE Low

WE High to RE Low

Device Resetting Time(Read/Program/Erase)

Last RE High to Busy(at sequential read)

CE High to Ready(in case of interception by CE at read)

CE High Hold Time(at the last serial read)(2)

Symbol

tR

tAR

tCLR

tRR

tRP

tWB

tRC

tCEA

tREA

tRHZ

tCHZ

tOH

tREH

tIR

tWHR

tRST

tRB

tCRY

tCEH

NOTE :

1. If reset command(FFh) is written at Ready state, the device goes into Busy for maximum 5us.

2. To break the sequential read cycle, CE must be held high for longer time than tCEH.

3. The time to Ready depends on the value of the pull-up resistor tied R/B pin.

Min Max Unit

- 15 µs

10 - ns

10 - ns

20 - ns

25 - ns

- 100 ns

50 - ns

- 45 ns

- 30 ns

- 30 ns

- 20 ns

15 - ns

15 - ns

0 - ns

60 - ns

-

5/10/500(1)

µs

- 100 ns

-

50 + tr(R/B)(3)

ns

100 - ns

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet K9T1G08U0M.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K9T1G08U0M | 128M x 8 Bits NAND Flash Memory | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |