|

|

PDF L4992 Data sheet ( Hoja de datos )

| Número de pieza | L4992 | |

| Descripción | TRIPLE OUTPUT POWER SUPPLY CONTROLLER | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de L4992 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

® L4992

TRIPLE OUTPUT POWER SUPPLY CONTROLLER

DUAL PWM BUCK CONTROLLERS (3.3V

and 5.1V)

12V/120mA LINEAR REGULATOR

DUAL SYNCH RECTIFIERS DRIVERS

96% EFFICIENCY ACHIEVABLE

50µA (@ 12V) STAND BY CONSUMPTION

5.5V TO 25V SUPPLY VOLTAGE

EXCELLENT LOAD TRANSIENT RESPONSE

DISABLE PULSE SKIPPING FUNCTION

POWER MANAGEMENT:

- UNDER AND OVERVOLTAGE OUTPUT

DETECTION

- POWER GOOD SIGNAL

- SEPARATED DISABLE

THERMAL SHUTDOWN

PACKAGE: TQFP32

APPLICATION

NOTEBOOK AND SUBNOTEBOOK COM-

PUTERS

PEN TOP AND PORTABLE EQUIPMENT

COMMUNICATING COMPUTERS

DESCRIPTION

The L4992 is a sophisticated dual PWM step-

down controller and power monitor intended for

Notebook computer and/or battery powered

equipment. The device produces regulated

+3.3V, +5.1V and 12V supplies for use in portable

SYSTEM BLOCK DIAGRAM

TQFP32

ORDERING NUMBER: L4992

and PCMCIA applications.

The internal architecture allows to operate with

minimum external components count. A very high

switching frequency (200/300 KHz or externally

synchronizable) optimizes their physical dimen-

sions.

Synchronous rectification and pulse skipping

mode for the buck sections optimise the overall

efficiency over a wide load current range (96% ef-

ficiency @1A/5.1V and 93% efficiency @

0.05A/5.1V.

The two high performance PWM controllers for

+3.3V and +5.1V lines are monitored for overvol-

tage, undervoltage and overcurrent conditions.

On detection of a fault, a POWER GOOD signal

is generated and a specific shutdown procedure

takes place to prevent physical damage and data

corruption.

A disable function allows to manage the output

power sections separately, optimising the quies-

cent consumption of the IC in stand-by conditions.

5.5V

to

25V

SYNC

L4992

D96IN429A

June 2000

POWER

MANAGEMENT

& SYSTEM

SUPERVISOR

POWER

SECTION

3.3V

5.1V

12V LDO

5.1V LDO

3.39V REF

POWER GOOD

µP

MEMORY

PERIPHERALS

1/26

1 page

L4992

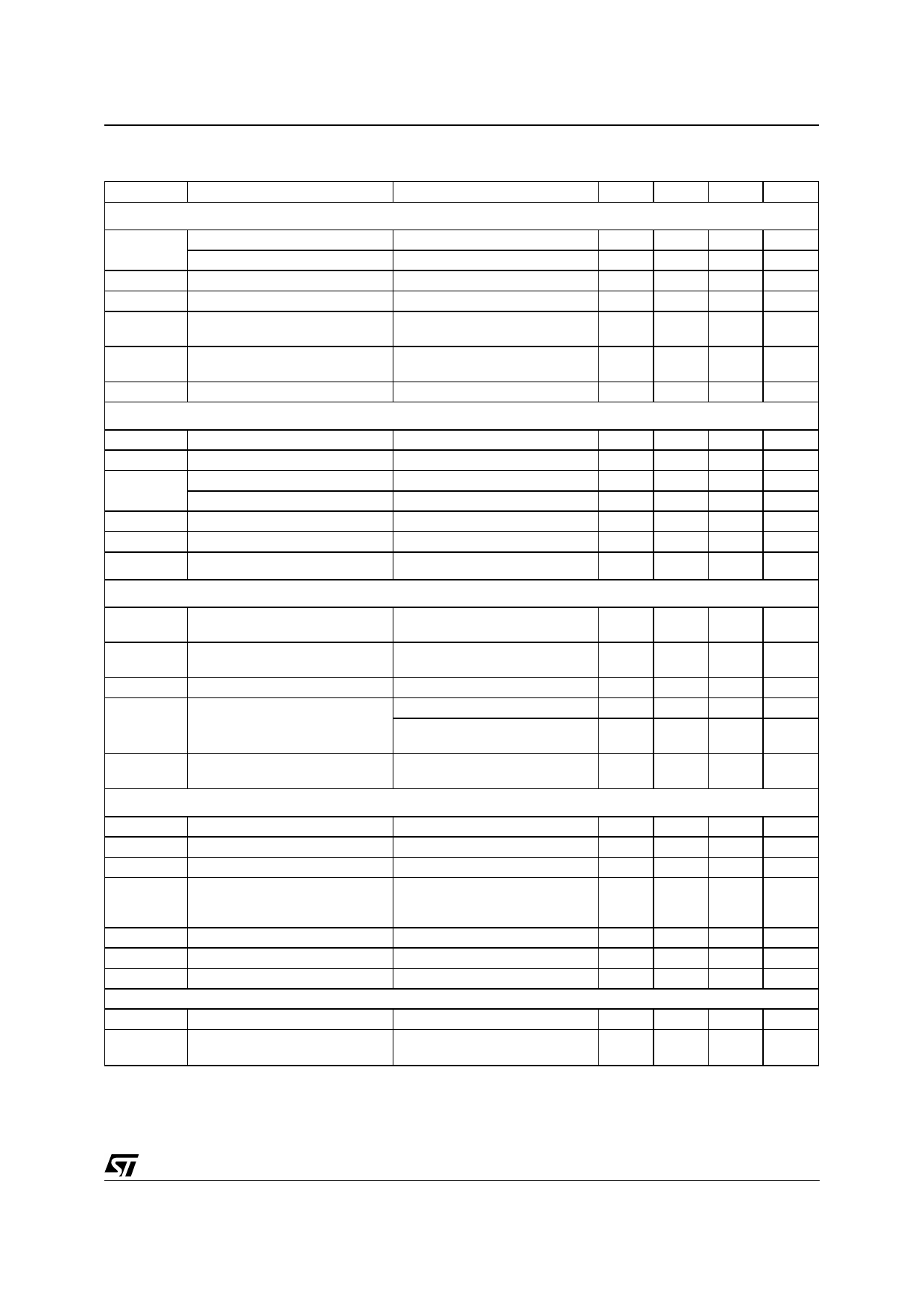

ELECTRICAL CHARACTERISTICS (Continued)

Symbol

Parameter

Test Condition

Min.

HIGH AND LOW SIDE GATE DRIVER (BOTH SECTIONS)

I25, I27,

I32, I30

Source Output Peak Current

Sink Output Peak Current

CLOAD = 1nF

CLOAD = 1nF

RH RDSON Resistance (or Impedance) Driver OUT HIGH

RL RDSON resistance (or Impedance) Driver OUT LOW

VOH Output High Voltage

HSTRAP = REG5

ISOURCE = 10mA; HSRC = GND

VOL Output Low Voltage

HSTRAP = REG5

ISINK = 10mA HSRC = GND

TCC Cross-Conduction Delay

0.2

0.2

4.40

30

12V LINEAR REGULATOR SECTION

V21 Input Voltage Range

V22 Output Voltage

I22 Current Limiting

Short Circuit Current

VCP Input Voltage Clamp

"One Shot" Activation Threshold

"One Shot" Pulse

I22 = 0 to 120mA

VREG12 = 12V

VREG12 = 0V

ICLAMP = 100µA

V13IN Falling

13

11.54

120

150

16

12.88

Typ.

0.5

0.5

5.3

75

12.0

13.7

Max.

7

5

5.61

0.5

130

20

12.48

14.52

1.5

Unit

A

A

Ω

Ω

V

V

ns

V

V

mA

mA

V

V

µs

INTERNAL REGULATOR (VREG5) AND REFERENCE VOLTAGE

V3 VREG5 Output Voltage

VIN = 5.5 to 20V

ILOAD = 0 to 5mA

I3 Total Current Capability

VREG5 = 5.3V

VREG5 = 6V

Switch-Over Threshold Voltage

V12 Reference Voltage

VIN = 5.5 to 20V

ILOAD = 1 to 5mA

I12 Source Current at Reference

Voltage

POWER GOOD AND ENABLE FUNCTION

V16, V11 RUN3, RUN5, Enable Voltage HIGH LEVEL

V16, V11 RUN3, RUN5, Disable Voltage LOW LEVEL

T10 Power Good Delay

CCRST = 100nF

T27, T30

Shutdown Delay Time before

Low Side Activation

(Except Over-Voltage Fault)

CCRST = 100nF,

CRST Timing Rate

Power Good High Level

Power Good LowLevel

SYNCHRONIZATION

IPWROK = 40µA

IPWROK = 320µA

Synchronisation Pulse Width

Synchronisation Input Voltage

(Falling Edge Transition)

4.5

25

70

4.3

3.35

3.32

5

5.3 5.61

4.53

3.39

3.39

4.7

3.43

3.46

V

mA

V

V

V

mA

2.4 V

0.8 V

160 200 240 ms

160 200 240 ms

2 ms/nF

4.1 V

0.4 V

400 ns

5V

5/26

5 Page

L4992

DETAILED FUNCTIONAL DESCRIPTION (continued)

+5 V LINEAR REGULATOR & +3.3 V REFERENCE VOLTAGE GENERATOR

This low drop-out regulator powers almost all the internal circuitry, that is the +3.3V reference voltage

generator, amplifiers, comparators, digital logic, and MOSFET drivers. Its output is externally available

through pin REG5.

The typical external use of this generator is to charge the bootstrap capacitors used to produce the gate-

drive voltage for the high-side MOSFET’s of both PWM converters.

At start-up and when the 5V section is not operating, this regulator is powered by the chip input voltage.

To reduce power consumption, the linear regulator is turned off and the REG5 pin is internally connected

to the 5V PWM regulator output via V5SW pin, when the 5V PWM regulator is active and its output volt-

age is above the switchover threshold, 4.5V.

The 5V regulator is always active, even if both PWM regulators are disabled, as long as power is applied

to the chip.

The 3.3V reference voltage generator, which is active only when either PWM converter is enabled, pro-

vides comparison levels for threshold detection and device operation. It is allowed to source up to 5mA

to an external load from its buffered output, externally available through pin VREF.

If either REG5 or VREF does not deliver the correct voltage, the device is shut down.

POWER MANAGEMENT

The L4992 is provided with some control pins suitable to perform some functions which are commonly

used or sometimes required in battery-operated equipment. Besides, it features controlled timing se-

quences in case of turn-on/off and device shutdown for a safe and reliable behaviour under all condi-

tions.

As above mentioned, RUN3 and RUN5 pins allow to disable separately both PWM converters by means

of logic signals (likely coming from a µP) as mentioned earlier.

NOSKIP can disable the pulse-skipping feature: when it is held high neither of the PWM regulators is al-

lowed to enter this kind of operation.

The PWROK output signal drives low immediately when either PWM regulator output falls below its own

undervoltage threshold or when either of them is disabled. It is high when both regulator run properly.

A capacitor connected between CRST and ground fixes a time, in the order of 2ms/nF, which delays the

transition low-high of PWROK. This happens at start-up or after recovering an undervoltage condition,

provided both RUN3 and RUN5 are high. The delay starts from the moment in which the output voltage

has reached its correct value for both sections.

The same delay intervenes also in another circumstance: when a section is disabled (because its RUN is

driven low or owing to a thermal shutdown), the relevant synchronous rectifier is turned on after the

above delay in order to make sure that the load is no longer supplied.

This delay, however, does not intervene in case of overvoltage: the synchronous rectifier is immediately

turned on after the shutdown, thus acting as a built-in "crowbar".

All these timing sequences are illustrated in Fig 7.

11/26

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet L4992.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| L4990 | PRIMARY CONTROLLER | STMicroelectronics |

| L4990A | PRIMARY CONTROLLER | STMicroelectronics |

| L4990AD | PRIMARY CONTROLLER | STMicroelectronics |

| L4990D | PRIMARY CONTROLLER | STMicroelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |