|

|

PDF K7N323631C Data sheet ( Hoja de datos )

| Número de pieza | K7N323631C | |

| Descripción | 1Mx36 & 2Mx18 Pipelined NtRAM | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de K7N323631C (archivo pdf) en la parte inferior de esta página. Total 25 Páginas | ||

|

No Preview Available !

K7N323631C

K7N321831C

1Mx36 & 2Mx18 Pipelined NtRAMTM

36Mb NtRAMTM Specification

100TQFP/165FBGA with Pb / Pb-Free

(RoHS compliant)

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,

AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,

EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY.

ALL INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or simi-

lar applications where Product failure couldresult in loss of life or personal or physical harm, or any military

or defense application, or any governmental procurement to which special terms or provisions may apply.

* Samsung Electronics reserves the right to change products or specification without notice.

www.DataSheet4U.com

- 1 - Rev. 1.2 September 2008

1 page

K7N323631C

K7N321831C

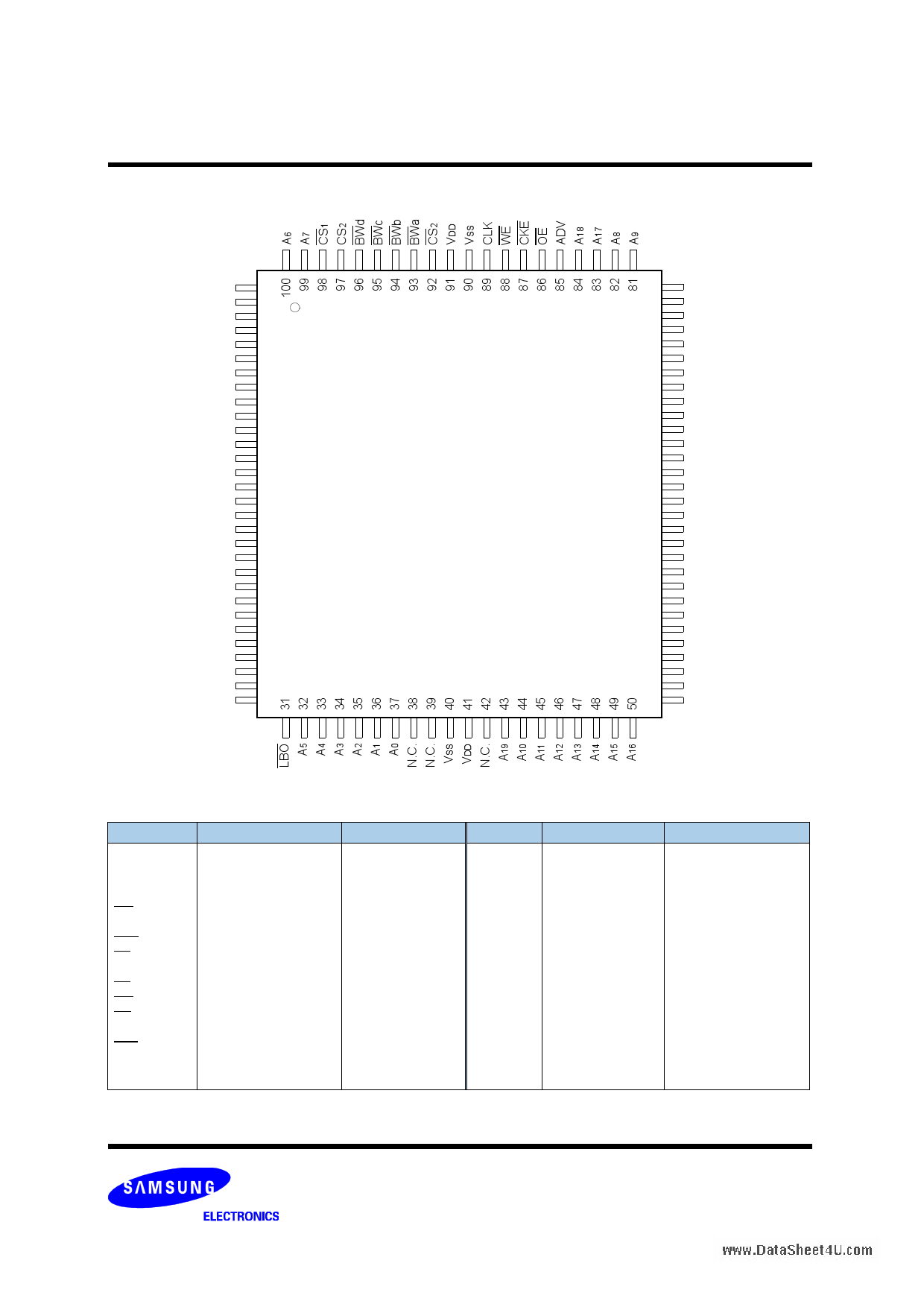

PIN CONFIGURATION(TOP VIEW)

1Mx36 & 2Mx18 Pipelined NtRAMTM

DQPc

DQc0

DQc1

VDDQ

VSSQ

DQc2

DQc3

DQc4

DQc5

VSSQ

VDDQ

DQc6

DQc7

VDD

VDD

VDD

VSS

DQd0

DQd1

VDDQ

VSSQ

DQd2

DQd3

DQd4

DQd5

VSSQ

VDDQ

DQd6

DQd7

DQPd

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

100 Pin TQFP

(20mm x 14mm)

K7N323631C (1Mx36)

80 DQPb

79 DQb7

78 DQb6

77 VDDQ

76 VSSQ

75 DQb5

74 DQb4

73 DQb3

72 DQb2

71 VSSQ

70 VDDQ

69 DQb1

68 DQb0

67 VSS

66 VDD

65 VDD

64 ZZ

63 DQa7

62 DQa6

61 VDDQ

60 VSSQ

59 DQa5

58 DQa4

57 DQa3

56 DQa2

55 VSSQ

54 VDDQ

53 DQa1

52 DQa0

51 DQPa

PIN NAME

SYMBOL

PIN NAME

TQFP PIN NO.

SYMBOL

A0 - A19

Address Inputs

ADV

Address Advance/Load

WE Read/Write Control Input

CLK Clock

CKE

Clock Enable

CS1 Chip Select

CS2 Chip Select

CS2 Chip Select

BWx(x=a,b,c,d) Byte Write Inputs

OE Output Enable

ZZ Power Sleep Mode

LBO

Burst Mode Control

32,33,34,35,36,37,43, VDD

44,45,46,47,48,49,50, VSS

81,82,83,84,99,100

85 N.C.

88

89 DQa0~a7

87 DQb0~b7

98 DQc0~c7

97 DQd0~d7

92

93,94,95,96

DQPa~Pd

86 VDDQ

64

31 VSSQ

PIN NAME

TQFP PIN NO.

Power Supply(+3.3V) 14,15,16,41,65,66,91

Ground

17,40,67,90

No Connect

38,39,42

Data Inputs/Outputs

Data Inputs/Outputs

Data Inputs/Outputs

Data Inputs/Outputs

Data Inputs/Outputs

52,53,56,57,58,59,62,63

68,69,72,73,74,75,78,79

2,3,6,7,8,9,12,13

18,19,22,23,24,25,28,29

51,80,1,30

Output Power Supply 4,11,20,27,54,61,70,77

(3.3V or 2.5V)

Output Ground

5,10,21,26,55,60,71,76

www.DataSheet4U.com

Note : 1. A0 and A1 are the two least significant bits(LSB) of the address field and set the internal burst counter if burst is desired.

- 5 - Rev. 1.2 September 2008

5 Page

K7N323631C

K7N321831C

1Mx36 & 2Mx18 Pipelined NtRAMTM

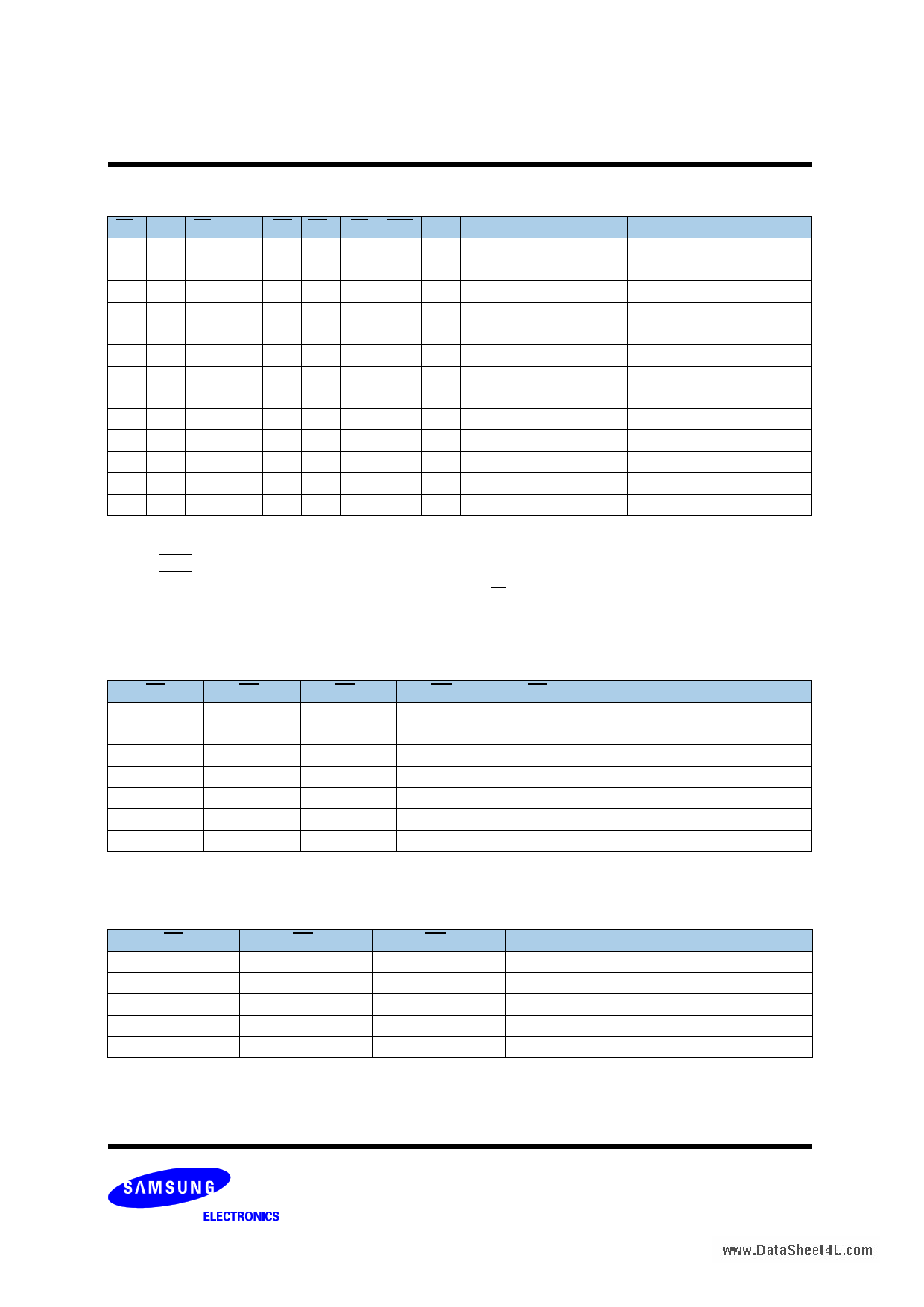

TRUTH TABLES

SYNCHRONOUS TRUTH TABLE

CS1 CS2 CS2 ADV WE BWx OE CKE CLK

HXXLXXX L ↑

ADDRESS ACCESSED

N/A

XLXLXXX L ↑

XXHLXXX L ↑

XXXHXXX L ↑

LHL LHXL L ↑

N/A

N/A

N/A

External Address

XXXHXXL L ↑

LHL LHXH L ↑

XXXHXXH L ↑

LHLLLLX L ↑

Next Address

External Address

Next Address

External Address

XXXHXLX L ↑

Next Address

LHL L LHX L ↑

XXXHXHX L ↑

XXXXXXX H ↑

N/A

Next Address

Current Address

Notes : 1. X means "Don′t Care". 2. The rising edge of clock is symbolized by (↑).

3. A continue deselect cycle can only be enterd if a deselect cycle is executed first.

4. WRITE = L means Write operation in WRITE TRUTH TABLE.

WRITE = H means Read operation in WRITE TRUTH TABLE.

5. Operation finally depends on status of asynchronous input pins(ZZ and OE).

Operation

Not Selected

Not Selected

Not Selected

Not Selected Continue

Begin Burst Read Cycle

Continue Burst Read Cycle

NOP/Dummy Read

Dummy Read

Begin Burst Write Cycle

Continue Burst Write Cycle

NOP/Write Abort

Write Abort

Ignore Clock

WRITE TRUTH TABLE(x36)

WE

BWa

BWb

BWc

BWd

HXXXX

L LHHH

L H L HH

L HH L H

L HHH L

LLLLL

L HHHH

Notes : 1. X means "Don′t Care".

2. All inputs in this table must meet setup and hold time around the rising edge of CLK(↑).

WRITE TRUTH TABLE(x18)

WE

BWa

BWb

HXX

LLH

LHL

LLL

LHH

www.DataNSohteese:t214..UAX.llcmionepmauntssi"nDtohnis′ttaCbalreem". ust meet setup and hold time around the rising edge of CLK(↑).

OPERATION

READ

WRITE BYTE a

WRITE BYTE b

WRITE BYTE c

WRITE BYTE d

WRITE ALL BYTEs

WRITE ABORT/NOP

OPERATION

READ

WRITE BYTE a

WRITE BYTE b

WRITE ALL BYTEs

WRITE ABORT/NOP

- 11 - Rev. 1.2 September 2008

11 Page | ||

| Páginas | Total 25 Páginas | |

| PDF Descargar | [ Datasheet K7N323631C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K7N323631C | 1Mx36 & 2Mx18 Pipelined NtRAM | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |