|

|

PDF CE5037 Data sheet ( Hoja de datos )

| Número de pieza | CE5037 | |

| Descripción | Digital Satellite Tuner | |

| Fabricantes | Intel Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CE5037 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

CE5037

Digital Satellite Tuner

with RF Bypass

Data Sheet

Features

• Direct conversion tuner for quadrature down

conversion from L-band to Zero IF

• Symbol rate 1-45 MS/s

• High sensitivity < -83 dBm at 27.5 MS/s Code rate

7/8

• Independent RF AGC and baseband gain control

• Fifth order baseband filters with bandwidth

adjustable from 6 to 43 MHz

• Fully integrated alignment-free low phase noise

local oscillator

• Selectable RF Bypass

• Low power consumption 0.5W at 3.3V.

• 28 pin 5x5 mm QFN Package

Applications

• DVB-S PayTV satellite receivers

• DSS satellite receivers

• DVB-S2 8PSK satellite receivers

January 2007

Ordering Information

WGCE5037 882557

28 Pin QFN* Trays

WGCE5037 S L9FV 882558 28 Pin QFN* Tape & Reel

*Pb Free Matte Tin

-10°C to +85°C

Description

The CE5037 is a fully integrated direct conversion

tuner for digital satellite receiver systems. It provides

excellent immunity to composite undesired channels.

The device also contains a RF Bypass for connecting

to a second receiver module.

The CE5037 is simple to use, requiring no alignment or

tuning algorithms and uses a minimum number of

external components. The device is programmable via

a I2C compatible bus.

The CE5037 is qualified for DVB-S2 8PSK receiver

applications

A complete reference design (CE9542) is available

using CE6313 demodulator.

RF Input

CE5037

Bypass

Output

Quadrature

VCO

PLL

RF AGC

I

Q

I2C

Control

www.DataSheet4U.com

Loop

Filter

Crystal

Figure 1 - Basic Block Diagram

1

Intel Corporation

Order Number: D55745-002

Intel and the Intel logo are registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others. Copyright © 2007 Intel Corporation. All rights reserved.

1 page

CE5037

Data Sheet

1.0 Circuit Description

1.1 Functional Description

The CE5037 is a single chip wide band direct conversion tuner with integral RF bypass optimised for digital satellite

receiver systems. It provides excellent signal handling capability in the presence of high composite signal levels.

The device offers a highly integrated solution for a satellite tuner incorporating a low phase noise PLL frequency

synthesizer, the quadrature down converter, a fully integrated local oscillator, and programmable baseband channel

filters. A minimal number of additional peripheral components are required. The crystal reference source can be

also used as the reference for the demodulator.

An I2C compatible bus interface controls all of the tuner functionality.

The CE5037 contains both hardware and software power down modes.

1.2 Signal Path

1.2.1 RF Input

The tuner RF input signal at a frequency of 950 – 2150 MHz is fed to the CE5037 RF input pre-amplifier stage.

The signal handling is designed such that no tracking filter is required to offer immunity to input signal composite

overload.

The RF input amplifier feeds an AGC stage, which provides RF gain control. There is additional gain adjustment in

the baseband section. The total AGC gain range will guarantee an operating dynamic range of –92 to –10 dBm.

The RF AGC in the CE5037 is divided into two stages. The first stage is a continually variable gain control stage,

and provides the main system AGC set under control of the analogue AGC signal generated by the demodulator

section. The second stage is a programmable gain stage to reduce RF gain by 10 dB. This would normally be used

when an external LNA is being used to improve system sensitivity.

The analogue RF AGC is optimised for S/N and S/I performance across the full dynamic range. Typical RF AGC

characteristic and variation of IIP3, IIP2 and NF are shown in Section 8 - Typical Performance Curves.

The output of the AGC stage is coupled to the quadrature mixer where the RF signal is mixed with quadrature local

oscillator signals generated by the on-board local oscillator.

1.2.2 Baseband

The outputs of the quadrature down converter are passed through the baseband filters followed by a programmable

baseband gain stage.

The baseband paths are DC coupled. An integrated DC correction loop prevents saturation due to local oscillator

self-mixing in the converter section. No external components are required for dc correction.

The baseband filters are 5th order Chebychev and provide excellent matching in both amplitude and phase

between the I and Q channels. The filters are fully programmable for 3 dB bandwidths from 6 MHz to 43 MHz. The

recommended filter bandwidth is related to the required symbol rate by the following equation.

www.DataSheet4U.com

− 3dBFilterBandwidth

fc

=

SymbolRate × 1.35

2 × 0.8

This equation makes no allowance for LNB tuning offset at low symbol rates < 10 MS/s.

5

Intel Corporation

5 Page

CE5037

Data Sheet

The LEN bit enables the RFBYPASS output. With this bit set, the RF Bypass is active even if ‘software’ or

‘hardware’ power down has been selected.

The RFG bit controls the gain of the second section of RF gain control. With this bit set, the RF gain is reduced by

10dB. This setting would normally used when an external LNA is being used.

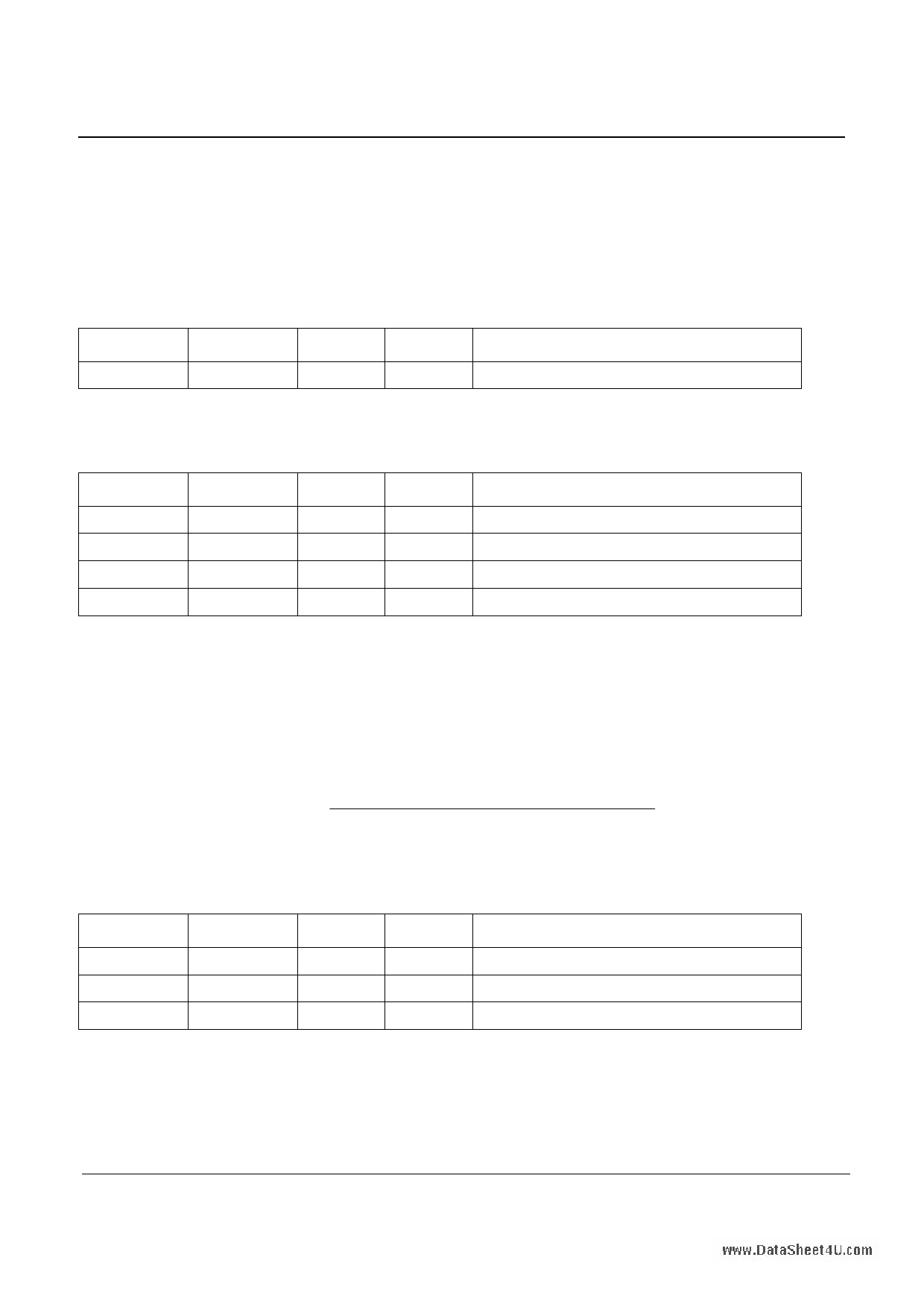

2.3 Base Band Registers

There are three registers that control the Base Band:

Bit Field

Name

Default

Type

Description

7:0

BF[7:0]

0X3C

R/W

Base Band Filter Cut-Off Frequency

Table 10 - Register 5

The bits BF[7:0] control the bandwidth of the baseband filter. An automatic adjustment routine synchronizes the

filter bandwidth to a reference frequency derived from the crystal.

Bit Field

Name

Default

Type

Description

7 - 0 R/W Test Mode

6

LF

0

R/W

Baseband Filter Adjust Disable

5

SF

0

R/W

Baseband Filter Adjust Disable

4:0

BR[4:0]

1000

R/W

Base Band Reference Division Ratio

Table 11 - Register 6

The LF and SF bits disable the baseband filter adjustment. It is recommended that these bits are set after

programming the filter bandwidth to prevent interactions within the circuit. These bits must be reset to enable the

baseband filter bandwidth to be reprogrammed.

The BR[4:0] bits set the crystal reference divide ratio. This effectively determines the resolution setting of the

baseband filters. The baseband filter settings (BF[7:0]) can be calculated from the following equation.

BF[7 :

0]

=

(Filter

bandwidth(MHz)* 5.088 * BR[4 :

CrystalFrequency (MHz)

0])

−1

See Section 3 Applications Information, for a typical programming example.

BR[4:0] = 0 is invalid

Bit Field

Name

Default

Type

Description

7 BLF - R Base Band Lock Flag

6:3

BG[3:0]

0111

R/W Base Band Gain Select

2:0 - 000 R/W Test Modes

Table 12 - Register 7

The BLF bit indicates that the baseband adjustment has completed and locked.

www.DataSheet4U.com

The control bits BG[3:0] define the gain of the Base Band post-filter amplifier. The following table shows the gain -

note this is relative gain. The 1.5 dB gain steps enable the baseband output level to be adjusted and optimise gain

distribution for different symbol rates.

11

Intel Corporation

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CE5037.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CE5037 | Digital Satellite Tuner | Intel Corporation |

| CE5038 | DVB-S2 Advanced Modulation Satellite Tuner | Intel Corporation |

| CE5039 | DVB-S Digital Satellite Tuner | Intel Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |