|

|

PDF HY5S7B6LFP-S Data sheet ( Hoja de datos )

| Número de pieza | HY5S7B6LFP-S | |

| Descripción | 512MBit MOBILE SDR SDRAMs based on 8M x 4Bank x16I/O | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HY5S7B6LFP-S (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

512MBit MOBILE SDR SDRAMs based on 8M x 4Bank x16I/O

Document Title

4Bank x 8M x 16bits Synchronous DRAM

Revision History

Revision No.

0.1

0.2

0.3

0.4

1.0

History

Initial Draft

Package size (10 x 13 [mm2])

Defined DC Chatacteristics (Page 10 ~ 11)

Modified Address # in Ball Description and Figures

Final Version

Draft Date

Oct. 2004

May. 2005

Aug. 2006

Aug. 2006

Jan. 2007

Remark

Preliminary

Preliminary

Preliminary

Preliminary

www.DataSheet4U.com

This document is a general product description and is subject to change without notice. Hynix does not assume any responsibility for

use of circuits described. No patent licenses are implied.

Rev 1.0 / Jan. 2007

1

1 page

11

512Mbit (32Mx16bit) Mobile SDR Memory

HY5S7B6LF(P) Series

BALL DESCRIPTION

98

7

A

B

C

D

E

F

G

H

J

3 21

54 Ball

FBGA

0.8mm

Ball Pitch

1

VSS

DQ14

DQ12

DQ10

DQ8

UDQM

A12

A8

www.DataSheet4U.com

VSS

Rev 1.0 / Jan. 2007

2

DQ15

DQ13

DQ11

DQ9

NC

CLK

A11

A7

A5

<Bottom View>

37

VSSQ A VDDQ

VDDQ B VSSQ

VSSQ C VDDQ

VDDQ D VSSQ

VSS E VDD

CKE F /CAS

A9 G BA0

A6 H A0

A4 J A3

< Top View >

8

DQ0

DQ2

DQ4

DQ6

LDQM

/RAS

BA1

A1

A2

9

VDD

DQ1

DQ3

DQ5

DQ7

/WE

/CS

A10

VDD

5

5 Page

11

512Mbit (32Mx16bit) Mobile SDR Memory

HY5S7B6LF(P) Series

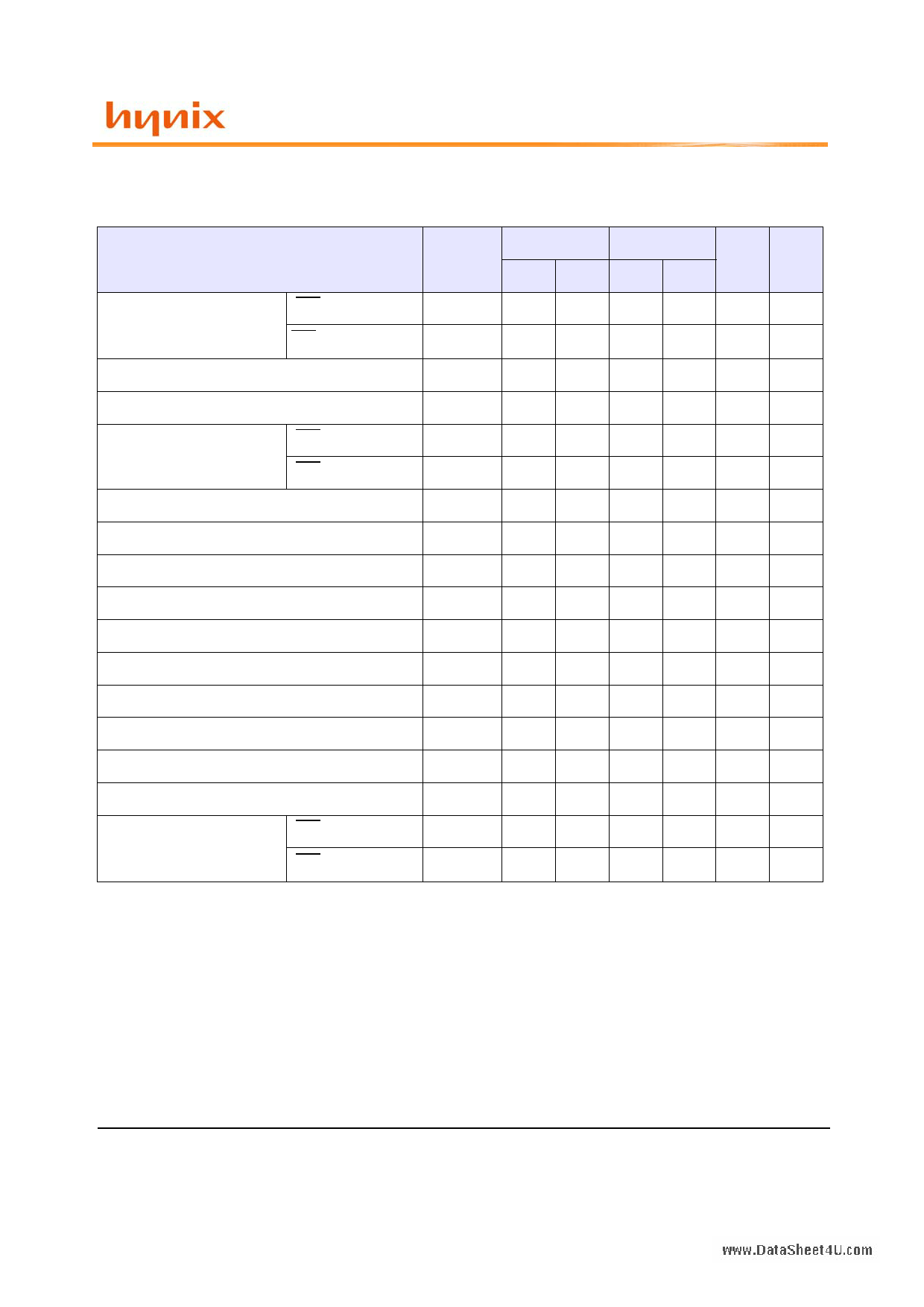

AC CHARACTERISTICS I (AC operating conditions unless otherwise noted)

Parameter

System Clock

Cycle Time

CAS Latency=3

CAS Latency=2

Clock High Pulse Width

Clock Low Pulse Width

Access Time From Clock

CAS Latency=3

CAS Latency=2

Data-out Hold Time

Data-Input Setup Time

Data-Input Hold Time

Address Setup Time

Address Hold Time

CKE Setup Time

CKE Hold Time

Command Setup Time

Command Hold Time

CLK to Data Output in Low-Z Time

CLK to Data Output in

High-Z Time

CAS Latency=3

CAS Latency=2

Symbol

tCK3

tCK2

tCHW

tCLW

tAC3

tAC2

tOH

tDS

tDH

tAS

tAH

tCKS

tCKH

tCS

tCH

tOLZ

tOHZ3

tOHZ2

H

Min Max

7.5 1000

12 1000

2.5 -

2.5 -

- 6.5

- 9.0

2.0 -

2.0 -

1.0 -

2.0 -

1.0 -

2.0 -

1.0 -

2.0 -

1.0 -

1.0 -

6.5

9.0

S

Min Max

9.5 1000

15 1000

3.0 -

3.0 -

- 7.0

- 10

2.0 -

3.0 -

1.5 -

3.0 -

1.5 -

3.0 -

1.5 -

3.0 -

1.5 -

1.0 -

7.0

10

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Note

1

1

2

2

1

1

1

1

1

1

1

1

Note :

1. Assume tR / tF (input rise and fall time) is 1ns. If tR & tF > 1ns, then [(tR+tF)/2-1]ns should be added to the parameter.

2. Access time to be measured with input signals of 1V/ns edge rate, from 0.8V to 0.2V. If tR > 1ns,

then (tR/2-0.5)ns should be added to the parameter.

www.DataSheet4U.com

Rev 1.0 / Jan. 2007

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HY5S7B6LFP-S.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HY5S7B6LFP-H | 512MBit MOBILE SDR SDRAMs based on 8M x 4Bank x16I/O | Hynix Semiconductor |

| HY5S7B6LFP-S | 512MBit MOBILE SDR SDRAMs based on 8M x 4Bank x16I/O | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |