|

|

PDF HY5S7B6ALFP-H Data sheet ( Hoja de datos )

| Número de pieza | HY5S7B6ALFP-H | |

| Descripción | 512MBit MOBILE SDR SDRAMs based on 8M x 4Bank x16I/O | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HY5S7B6ALFP-H (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

512MBit MOBILE SDR SDRAMs based on 8M x 4Bank x16I/O

Document Title

4Bank x 8M x 16bits Synchronous DRAM

Revision History

Revision No.

0.1

0.2

1.0

1.1

History

Initial Draft

Inserted 166MHz Product

Release

Insert (Page10)

DPD specification [IDD7 : 10uA min]

Draft Date

Aug. 2006

Sep. 2006

May. 2007

July. 2007

Remark

Preliminary

Preliminary

This document is a general product description and is subject to change without notice. Hynix does not assume any responsibility for

use of circuits described. No patent licenses are implied.

Rev 1.1 / July. 2007

1

1 page

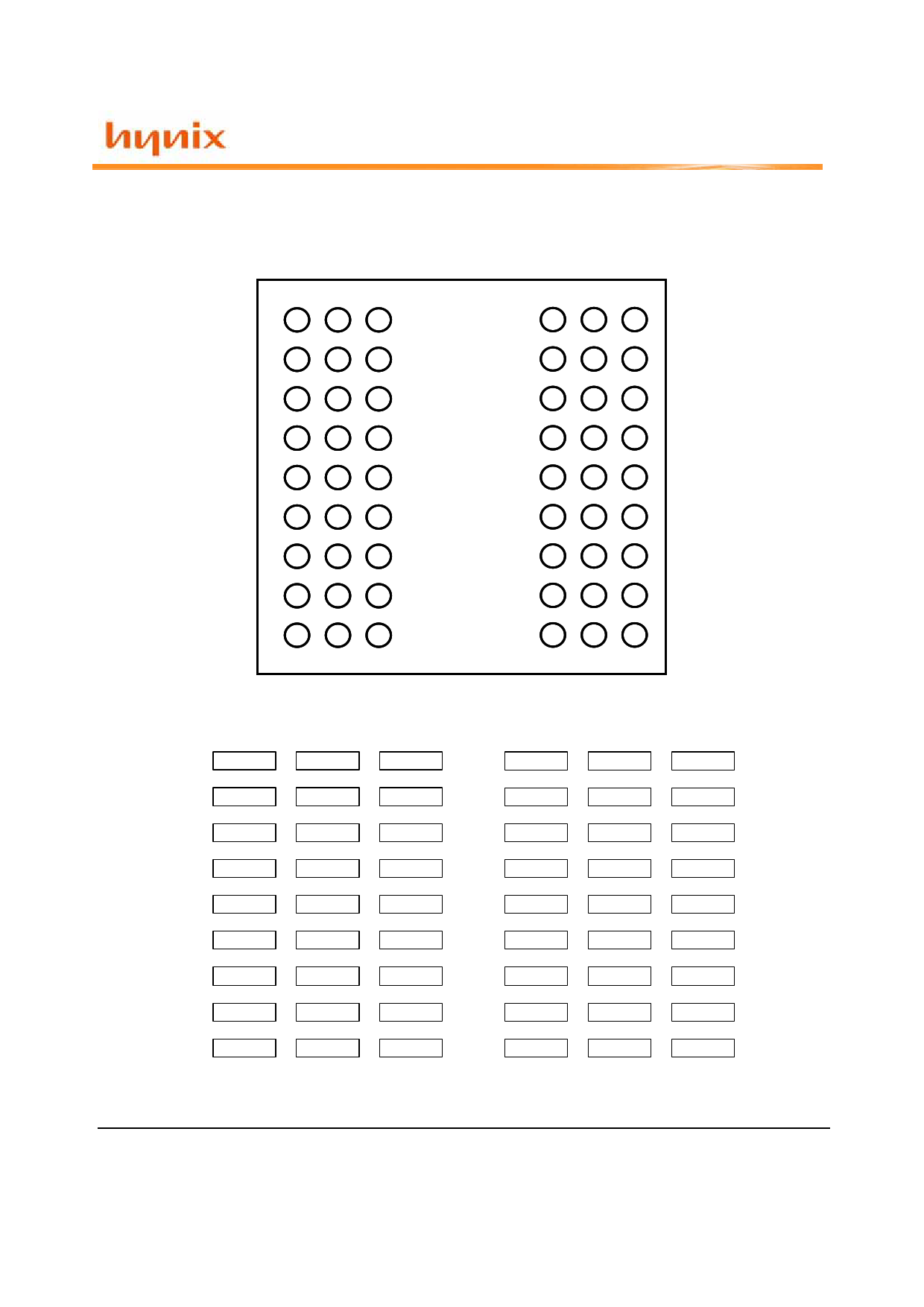

BALL DESCRIPTION

98

7

A

B

C

D

E

F

G

H

J

11

512Mbit (32Mx16bit) Mobile SDR Memory

HY5S7B6ALF(P) Series

3 21

54 B all

FBGA

0.8m m

B all Pitch

< B ottom View >

Rev 1.1 / July. 2007

< Top View >

5

5 Page

11

512Mbit (32Mx16bit) Mobile SDR Memory

HY5S7B6ALF(P) Series

AC CHARACTERISTICS I (AC operating conditions unless otherwise noted)

Parameter

System Clock

Cycle Time

CAS Latency=3

CAS Latency=2

Clock High Pulse Width

Clock Low Pulse Width

CAS Latency=3

Access Time From Clock

CAS Latency=2

Data-out Hold Time

Data-Input Setup Time

Data-Input Hold Time

Address Setup Time

Address Hold Time

CKE Setup Time

CKE Hold Time

Command Setup Time

Command Hold Time

CLK to Data Output in Low-Z Time

CLK to Data Output in

High-Z Time

CAS Latency=3

CAS Latency=2

Symbol

166MHz

Min Max

133MHz

Min Max

105MHz

Unit Note

Min Max

tCK3 6.0 1000 7.5 1000 9.5 1000 ns

tCK2 12 1000 12 1000 15 1000 ns

tCHW

tCLW

2.0 - 2.5 - 3.0 - ns 1

2.0 - 2.5 - 3.0 - ns 1

tAC3 - 5.4 - 6.0 - 7.0 ns 2, 3

tAC2 - 6.0 - 8.0 - 10 ns 2, 3

tOH 2.6 - 2.6 - 2.6 - ns 3

tDS 2.0 - 2.0 - 3.0 - ns 1

tDH 1.0 - 1.0 - 1.5 - ns 1

tAS 2.0 - 2.0 - 3.0 - ns 1

tAH 1.0 - 1.0 - 1.5 - ns 1

tCKS 2.0 - 2.0 - 3.0 - ns 1

tCKH

1.0 - 1.0 - 1.5 - ns 1

tCS 2.0 - 2.0 - 3.0 - ns 1

tCH 1.0 - 1.0 - 1.5 - ns 1

tOLZ 1.0 - 1.0 - 1.0 - ns

tOHZ3

5.4 6.0 7.0 ns

tOHZ2

6.0 8.0 10 ns

Notes :

1. Assume tR / tF (input rise and fall time) is 1ns. If tR & tF > 1ns, then [(tR+tF)/2-1]ns should be added to the parameter.

2. Access time to be measured with input signals of 1V/ns edge rate, from 0.8V to 0.2V. If tR > 1ns,

then (tR/2-0.5)ns should be added to the parameter.

3. Output Load : 30pF+No termination

AC high level input voltage / low level input voltage : 1.6 / 0.2V

Input timing measurement reference level : 0.9V

Output

Z = 50

Transition time (input rise and fall time) : 0.5ns

Output timing measurement reference level : 0.9V

Output Load

Output load : CL = 30pF

CLK

30pF

1.6V

0.9V

0.2V

Input

1.6V

0.9V

0.2V

Output

tCK

tCH

tCL

tSETUP tHOLD

tAC

tOH

Rev 1.1 / July. 2007

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HY5S7B6ALFP-H.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HY5S7B6ALFP-6 | 512MBit MOBILE SDR SDRAMs based on 8M x 4Bank x16I/O | Hynix Semiconductor |

| HY5S7B6ALFP-H | 512MBit MOBILE SDR SDRAMs based on 8M x 4Bank x16I/O | Hynix Semiconductor |

| HY5S7B6ALFP-S | 512MBit MOBILE SDR SDRAMs based on 8M x 4Bank x16I/O | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |