|

|

PDF HYMP112S64CR6 Data sheet ( Hoja de datos )

| Número de pieza | HYMP112S64CR6 | |

| Descripción | 1200pin Unbuffered DDR2 SDRAM SO-DIMMs | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HYMP112S64CR6 (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

200pin Unbuffered DDR2 SDRAM SO-DIMMs based on 1Gb version C

This Hynix unbuffered Small Outline Dual In-Line Memory Module(DIMM) series consists of 1Gb version C DDR2

SDRAMs in Fine Ball Grid Array(FBGA) packages on a 200pin glass-epoxy substrate. This Hynix 1Gb version C based

Unbuffered DDR2 SO-DIMM series provide a high performance 8 byte interface in 67.60mm width form factor of indus-

try standard. It is suitable for easy interchange and addition.

FEATURES

• JEDEC standard Double Data Rate 2 Synchronous

DRAMs (DDR2 SDRAMs) with 1.8V +/- 0.1V Power

Supply

• All inputs and outputs are compatible with SSTL_1.8

interface

• Posted CAS

• Programmable CAS Latency 3 ,4 ,5, and 6

• OCD (Off-Chip Driver Impedance Adjustment) and

ODT (On-Die Termination)

• Fully differential clock operations (CK & CK)

• Programmable Burst Length 4 / 8 with both

sequential and interleave mode

• Auto refresh and self refresh supported

• 8192 refresh cycles / 64ms

• Serial presence detect with EEPROM

• DDR2 SDRAM Package: 60 ball(x8) , 84 ball(x16)

FBGA

• 67.60 x 30.00 mm form factor

• RoHS compliant

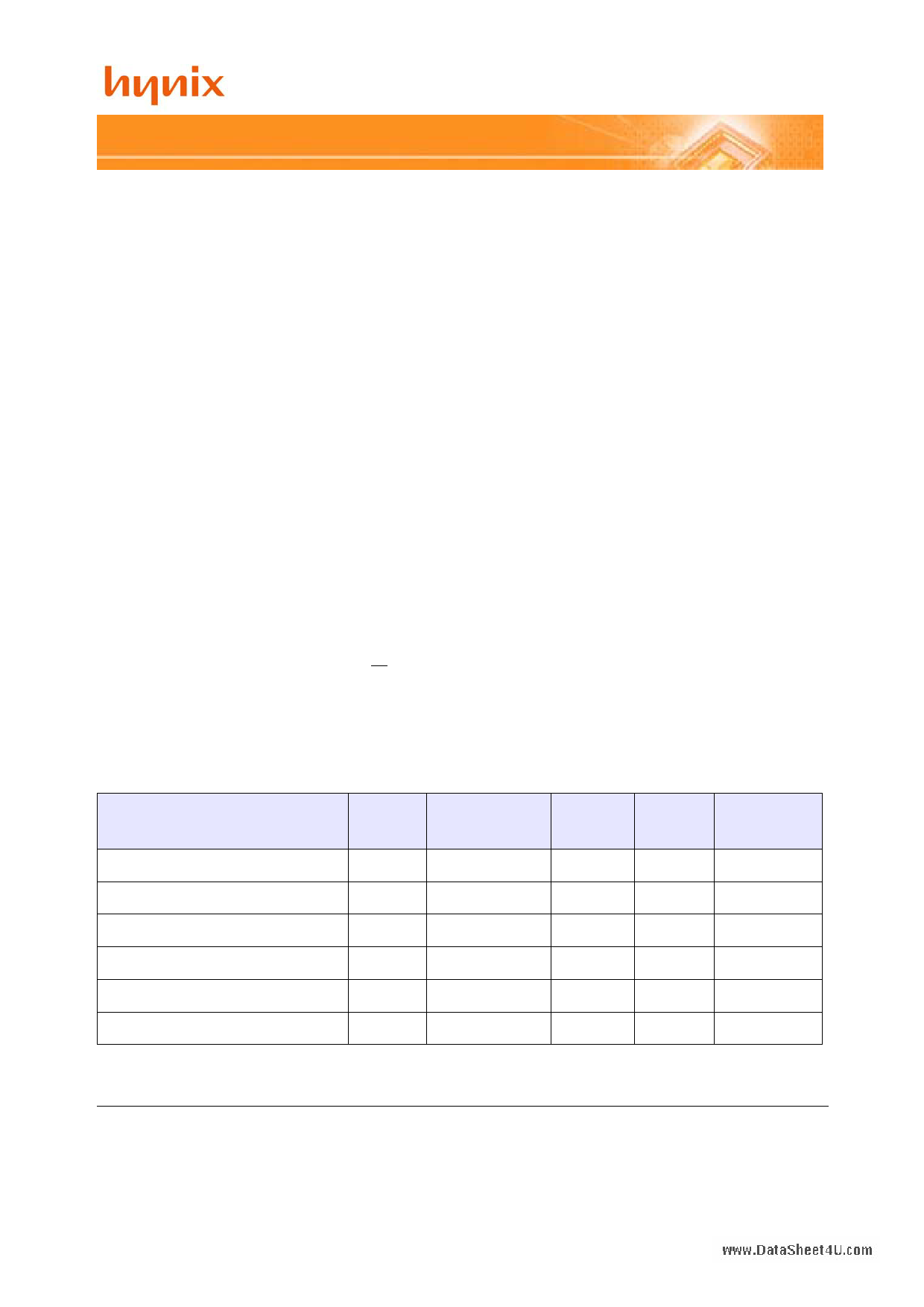

ORDERING INFORMATION

Part Name

HYMP164S64CP6-C4/Y5/S5/S6

HYMP164S64CR6-C4/Y5/S5/S6

HYMP112S64CP6-C4/Y5/S5/S6

HYMP112S64CR6-C4/Y5/S5/S6

HYMP125S64CP8-C4/Y5/S5/S6

HYMP125S64CR8-C4/Y5/S5/S6

Density Organization

512MB

512MB

1GB

1GB

2GB

2GB

64Mx64

64Mx64

128Mx64

128Mx64

256Mx64

256Mx64

# of

DRAMs

4

4

8

8

16

16

# of

ranks

1

1

2

2

2

2

Materials

Lead free

Halogen free

Lead free

Halogen free

Lead free

Halogen free

This document is a general product description and is subject to change without notice. Hynix Semiconductor does not assume any

responsibility for use of circuits described. No patent licenses are implied.

Rev. 1.0 / Dec. 2009

1

1 page

www.DataSheet4U.com

1200pin Unbuffered DDR2 SDRAM SO-DIMMs

FUNCTIONAL BLOCK DIAGRAM

512MB(64Mbx64) : HYMP164S64CP(R)6

DQS0

/DQS0

DM0

DQS2

/DQS2

DM2

CKE0

ODT0

/S0

3Ω +/-5%

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

LDQS

/UDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

UDQS

/UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

/S1

ODT1

CKE1

/CS ODT CKE

D0

DQS2

/DQS2

DM2

DQS3

/DQS3

DM3

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

LDQS

/UDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

UDQS

/UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

/CS ODT CKE

D1

DQS4

/DQS4

DM4

DQS5

/DQS5

DM5

DQS6

/DQS6

DM6

DQS7

/DQS7

DM7

N.C.

N.C.

N.C.

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

LDQS

/UDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

UDQS

/UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

LDQS

/UDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

UDQS

/UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

/CS ODT CKE

D2

/CS ODT CKE

D3

BA0-BA2

A0-AN

/RAS

/CAS

/WE

3Ω +/-5%

SDRAMS D0-3

SDRAMS D0-3

SDRAMS D0-3

SDRAMS D0-3

SDRAMS D0-3

CK0

/CK0

CK1

/CK1

2 loads

2 loads

Rev. 1.0 / Dec. 2009

SCL

SA0

SCL

A0

Serial PD

SDA

SDA

SA1 A1

A2 WP

VDDSPD

VREF

VDD

VSS

Serial PD

SDRAMS D0-D3

SDRAMS D0-D3, VDD and VDDQ

SDRAMS D0-D3, SPD

Note:

1.Resistor values are 22 ohm +/-5%.

5

5 Page

www.DataSheet4U.com

1200pin Unbuffered DDR2 SDRAM SO-DIMMs

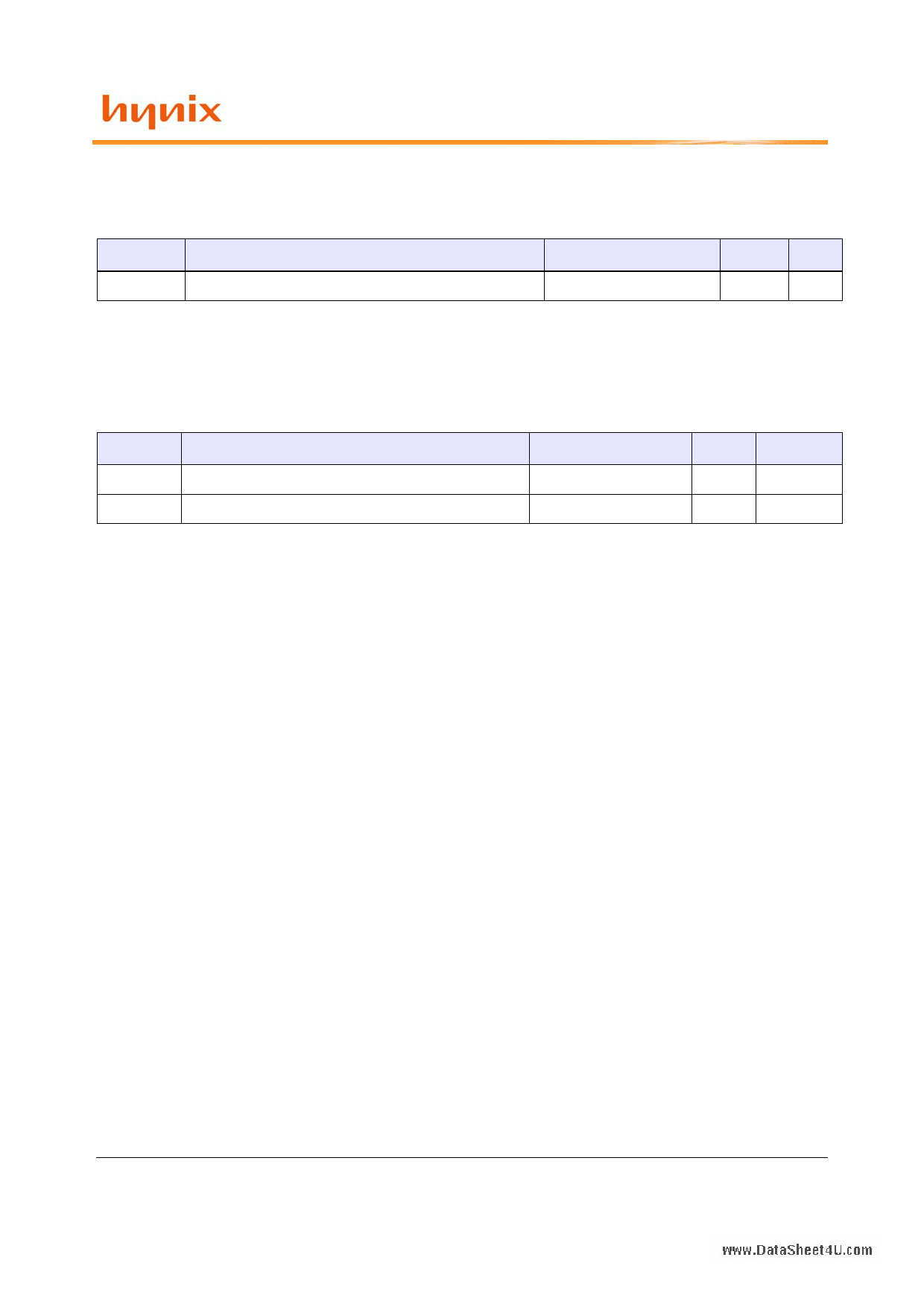

OUTPUT BUFFER LEVELS

OUTPUT AC TEST CONDITIONS

Symbol

VOTR

Parameter

Output Timing Measurement Reference Level

Notes:

1. The VDDQ of the device under test is referenced.

SSTL_18

0.5 * VDDQ

Units

V

Notes

1

OUTPUT DC CURRENT DRIVE

Symbol

Parameter

SSTl_18

Units

Notes

IOH(dc)

IOL(dc)

Output Minimum Source DC Current

Output Minimum Sink DC Current

- 13.4

13.4

mA 1, 3, 4

mA 2, 3, 4

Notes:

1. VDDQ = 1.7 V; VOUT = 1420 mV. (VOUT - VDDQ)/IOH must be less than 21 ohm for values of VOUT between VDDQ and

VDDQ - 280 mV.

2. VDDQ = 1.7 V; VOUT = 280 mV. VOUT/IOL must be less than 21 ohm for values of VOUT between 0 V and 280 mV.

3. The dc value of VREF applied to the receiving device is set to VTT

4. The values of IOH(dc) and IOL(dc) are based on the conditions given in Notes 1 and 2. They are used to test device

drive current capability to ensure VIH min plus a noise margin and VIL max minus a noise margin are delivered to an

SSTL_18 receiver.

The actual current values are derived by shifting the desired driver operating point along a 21 ohm load line to define

a convenient driver current for measurement.

Rev. 1.0 / Dec. 2009

11

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet HYMP112S64CR6.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HYMP112S64CR6 | 1200pin Unbuffered DDR2 SDRAM SO-DIMMs | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |