|

|

PDF LV8092GQ Data sheet ( Hoja de datos )

| Número de pieza | LV8092GQ | |

| Descripción | Bi-CMOS LSI Piezo Actuator Driver IC | |

| Fabricantes | Sanyo Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de LV8092GQ (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

Ordering number : ENA0844A

www.DataSheet4U.com

LV8092GQ

Bi-CMOS LSI

Piezo Actuator Driver IC

Overview

The LV8092GQ is a piezoelectric actuator driver IC. It internally generates drive waveforms and this makes it possible to

control piezoelectric actuators with simple instructions.

Features

• Actuators using piezoelectric elements can be driven simply by I2C communication.

• The piezoelectric drive waveforms are set externally by serial input signals using the I2C interface.

• The rising and falling timings are determined with clock count.

• EN input that controls the startup/stop of the IC.

• The time for which the actuator is driven is determined with the drive frequency setting based on I2C communication.

• Provides a busy signal output during periods when the actuator is being driven by OUT pin output so that applications can

be aware of the actuator operating/stopped state.

• Built-in thermal protection and undervoltage protection circuits

Specifications

Absolute Maximum Ratings at Ta = 25°C

Parameter

Symbol

Conditions

Supply voltage

Signal system supply voltage

Output current

Input signal voltage

Allowable power dissipation

VCC max

VDD max

IO max

VIN max

Pd

*Mounted on a specified board.

Operating temperature

Topr

Storage temperature

Tstg

* Specified board : 50mm×40mm×0.8mm, 4-layer glass epoxy circuit board.

Ratings

-0.5 to 6.0

-0.5 to 6.0

300

-0.5 to VDD+0.5

700

-30 to +85

-55 to +150

Unit

V

V

mA

V

mW

°C

°C

Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to

"standard application", intended for the use as general electronics equipment (home appliances, AV equipment,

communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be

intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace

instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety

equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case

of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee

thereof. If you should intend to use our products for applications outside the standard applications of our

customer who is considering such use and/or outside the scope of our intended standard applications, please

consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our

customer shall be solely responsible for the use.

Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate

the performance, characteristics, and functions of the described products in the independent state, and are not

guarantees of the performance, characteristics, and functions of the described products as mounted in the

customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent

device, the customer should always evaluate and test devices mounted in the customer's products or

equipment.

83107 MS / 71807 MS PC 20070402-S00001 No.A0844-1/12

1 page

LV8092GQ

www.DataSheet4U.com

I2C bus transfer method

Start and stop conditions

The I2C bus requires that the state of SDA be preserved while SCL is high as shown in the timing diagram below during

a data transfer operation.

SCL

SDA

ts2

th2

When data is not being transferred, both SCL and SDA are in the high state. The start condition is generated and access is

started when SDA is changed from high to low while SCL and SDA are high.

Conversely, the stop condition is generated and access is ended when SDA is changed from low to high while SCL is

high.

Start condition

Stop condition

SCL

SDA

th1

th3

Data transfer and acknowledgement response

After the start condition is generated, data is transferred one byte (8 bits) at a time. Any number of data bytes can be

transferred consecutively.

An ACK signal is sent to the sending side from the receiving side every time 8 bits of data are transferred. The

transmission of an ACK signal is performed by setting the receiving side SDA to low after SDA at the sending side is

released immediately after the clock pulse of SCL bit 8 in the data transferred has fallen low.

After the receiving side has sent the ACK signal, if the next byte transfer operation is to receive only the byte, the

receiving side releases SDA on the falling edge of the 9th clock of SCL.

There are no CE signals in the I2C bus ; instead, a 7-bit slave address is assigned to each device, and the first byte of the

transfer data is allocated to the 7-bit slave address and to the command (R/W) which specifies the direction of subsequent

data transfer.

The LB8092GQ is a drive IC with a dedicated write function and it does not have a read function.

The 7-bit address is transferred in sequence starting with MSB, and the eighth bit is set to low. The second and subsequent

bytes are transferred in write mode.

In the LV8092GQ, the slave address is stipulated to be “1110010.”.

Start

M

S

Slave address

L

S

A

WC

M

S

Register address

L

S

A

C

M

S

B B KB

BKB

Data

LA

SC

BK

Stop

SCL

SDA

1110101

00000010 00010001

No.A0844-5/12

5 Page

LV8092GQ

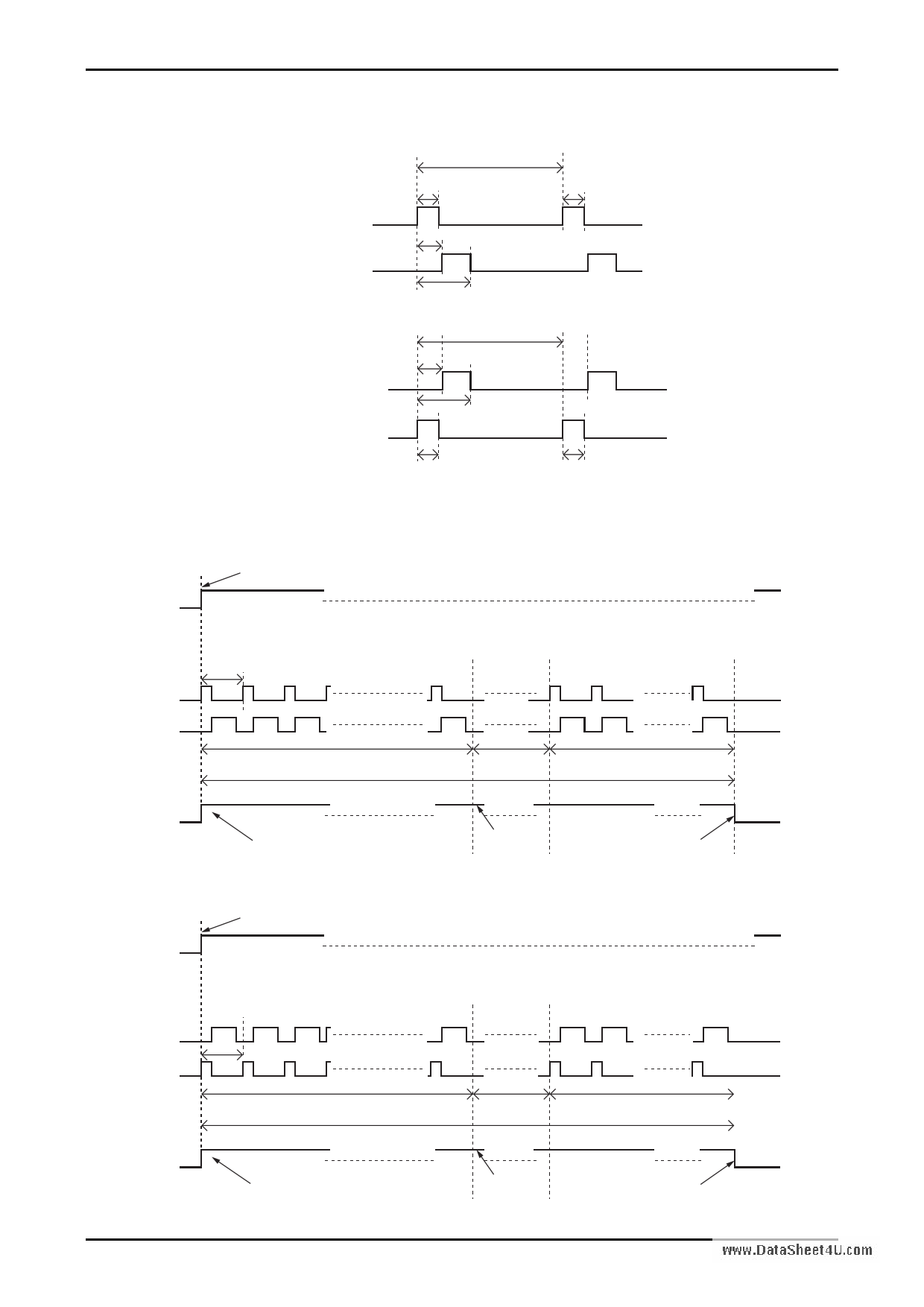

Timing charts

Enlarged view of the sequence of output signals

Operation toward infinity

(RST setting + 1) ×

number of clock pulses

(GTAS setting - 1) ×

number of clock pulses

(GTAS setting - 1) ×

number of clock pulses

OUT1

(GTAS setting - 1) × number of clock pulses

OUT2

Operation toward macro

OUT1

OUT2

(GTBR setting -1) × number of clock pulses

(RST setting + 1) ×

number of clock pulses

(GTBR setting -1) × number of clock pulses

(GTBS setting - 1) × number of clock pulses

www.DataSheet4U.com

(GTAS setting - 1) ×

number of clock pulses

(GTAS setting - 1) ×

number of clock pulses

Sequence of initial setting operation (“on” or “off” can be set by the I2C settings.)

When M/I register = 00 → Movement toward infinity position

Startup when EN is high, initial setting sequence starts

EN

OUT1

OUT2

BUSY

1 period

Operation toward infinity

STP period × INIT times

Standby state

Operation toward macro

STP period × 4 STP period × RET setting times

Initial setting operation time

High during initial setting in wait state too

BUSY output is high during initial setting operation.

BUSY output is low after initial setting.

When M/I register = 01 → Movement toward macro position

Startup when EN is high, initial setting sequence starts

EN

OUT1

OUT2

BUSY

1 period

Operation toward macro

STP period × INIT times

Standby state Operation toward infinity

STP period × 4 STP period × RET setting times

Initial setting operation time

High during initial setting in wait state too

BUSY output is high during initial setting operation.

BUSY output is low after initial setting.

No.A0844-11/12

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet LV8092GQ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LV8092GQ | Bi-CMOS LSI Piezo Actuator Driver IC | Sanyo Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |