|

|

PDF M24L28256SA Data sheet ( Hoja de datos )

| Número de pieza | M24L28256SA | |

| Descripción | 2-Mbit (256K x 8) Pseudo Static RAM | |

| Fabricantes | Elite Semiconductor Memory Technology | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de M24L28256SA (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

ESMT

www.DataSheet4U.com

M24L28256SA

PSRAM

2-Mbit (256K x 8)

Features

•Advanced low-power architecture

•High speed: 55 ns, 70 ns

•Wide voltage range: 2.7V to 3.6V

•Typical active current: 1 mA @ f = 1 MHz

•Low standby power

•Automatic power-down when deselected

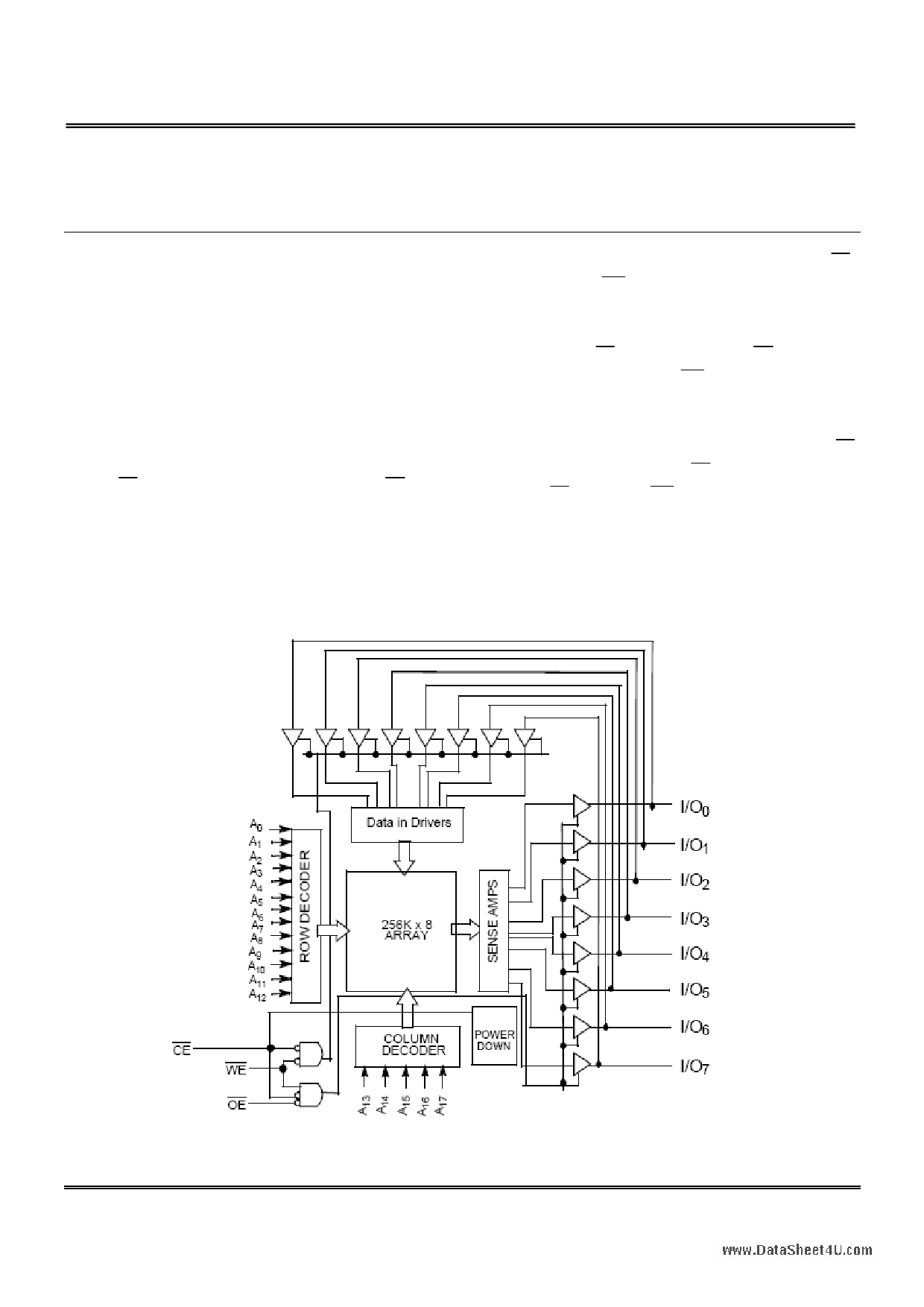

Functional Description

The M24L28256SA is a high-performance CMOS pseudo

static RAM (PSRAM) organized as 256K words by 8 bits.

Easy memory expansion is provided by an active LOW Chip

Enable( CE ) and active LOW Output Enable ( OE ).This

device has an automatic power-down feature that reduces

power consumption dramatically when deselected. Writing to

Pseudo Static RAM

the device is accomplished by asserting Chip Enable ( CE )

and Write Enable ( WE ) inputs LOW .Data on the eight I/O

pins(I/O0 through I/O7) is then written into the location

specified on the address pins (A0 through A17).

Reading from the device is accomplished by asserting the

Chip Enable One ( CE ) and Output Enable ( OE ) inputs LOW

while forcing Write Enable ( WE ) HIGH. Under these

conditions, the contents of the memory location specified by

the address pins will appear on the I/O pins.

The eight input/output pins (I/O0 through I/O7) are placed in a

high-impedance state when the device is deselected ( CE

HIGH ), the outputs are disabled ( OE HIGH), or during write

operation ( CE LOW and WE LOW). See the Truth Table

for a complete description of read and write modes.

Logic Block Diagram

Elite Semiconductor Memory Technology Inc.

Publication Date : Jul. 2008

Revision : 1.1

1/12

1 page

ESMT

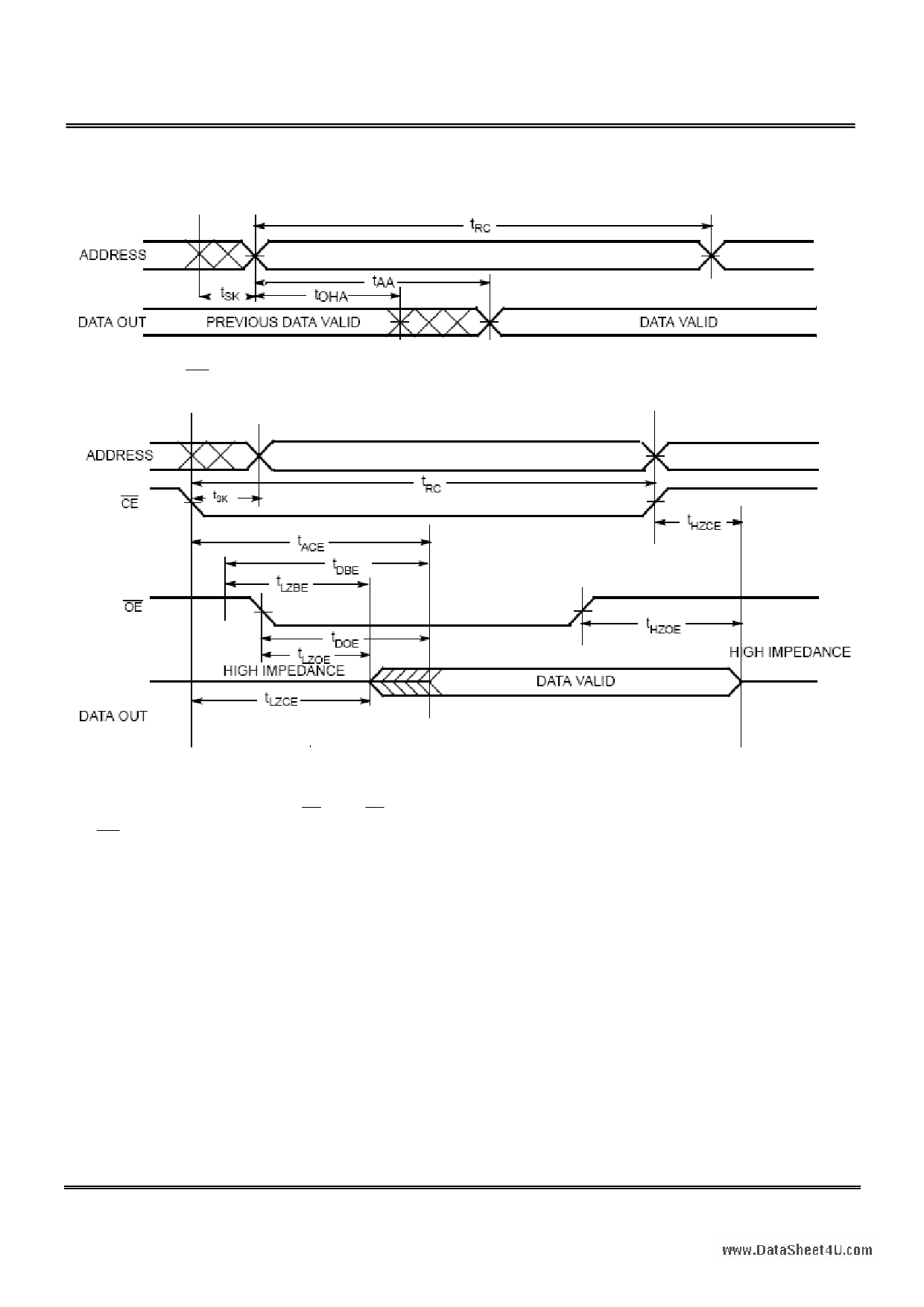

Switching Waveforms

Read Cycle 1 (Address Transition Controlled)[12, 13, 14]

www.DataSheet4U.com

M24L28256SA

Read Cycle 2 ( OE Controlled)[12, 14]

Notes:

13. Device is continuously selected. OE and CE = VIL.

14. WE is HIGH for Read Cycle.

Elite Semiconductor Memory Technology Inc.

Publication Date : Jul. 2008

Revision : 1.1

5/12

5 Page

ESMT

Revision History

Revision

1.0

1.1

www.DataSheet4U.com

M24L28256SA

Date

2007.07.19

2008.07.04

Description

Original

1. Move Revision History to the last

2. Modify voltage range 2.7V~3.3V to 2.7V~3.6V

3.Correct type error for Extended Temperature (-40~85°C

=> -25~85°C)

4. Add Industrial grade

5. Add Avoid timing

Elite Semiconductor Memory Technology Inc.

Publication Date : Jul. 2008

Revision : 1.1

11/12

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet M24L28256SA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M24L28256SA | 2-Mbit (256K x 8) Pseudo Static RAM | Elite Semiconductor Memory Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |