|

|

PDF M24L16161DA Data sheet ( Hoja de datos )

| Número de pieza | M24L16161DA | |

| Descripción | 16-Mbit (1M x 16) Pseudo Static RAM | |

| Fabricantes | Elite Semiconductor Memory Technology | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de M24L16161DA (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

ESMT

Revision History :

Revision 1.0 (Jul. 4, 2007)

- Original

www.DataSheet4U.com

M24L16161DA

Elite Semiconductor Memory Technology Inc.

Publication Date : Jul. 2007

Revision : 1.0

1/12

1 page

ESMT

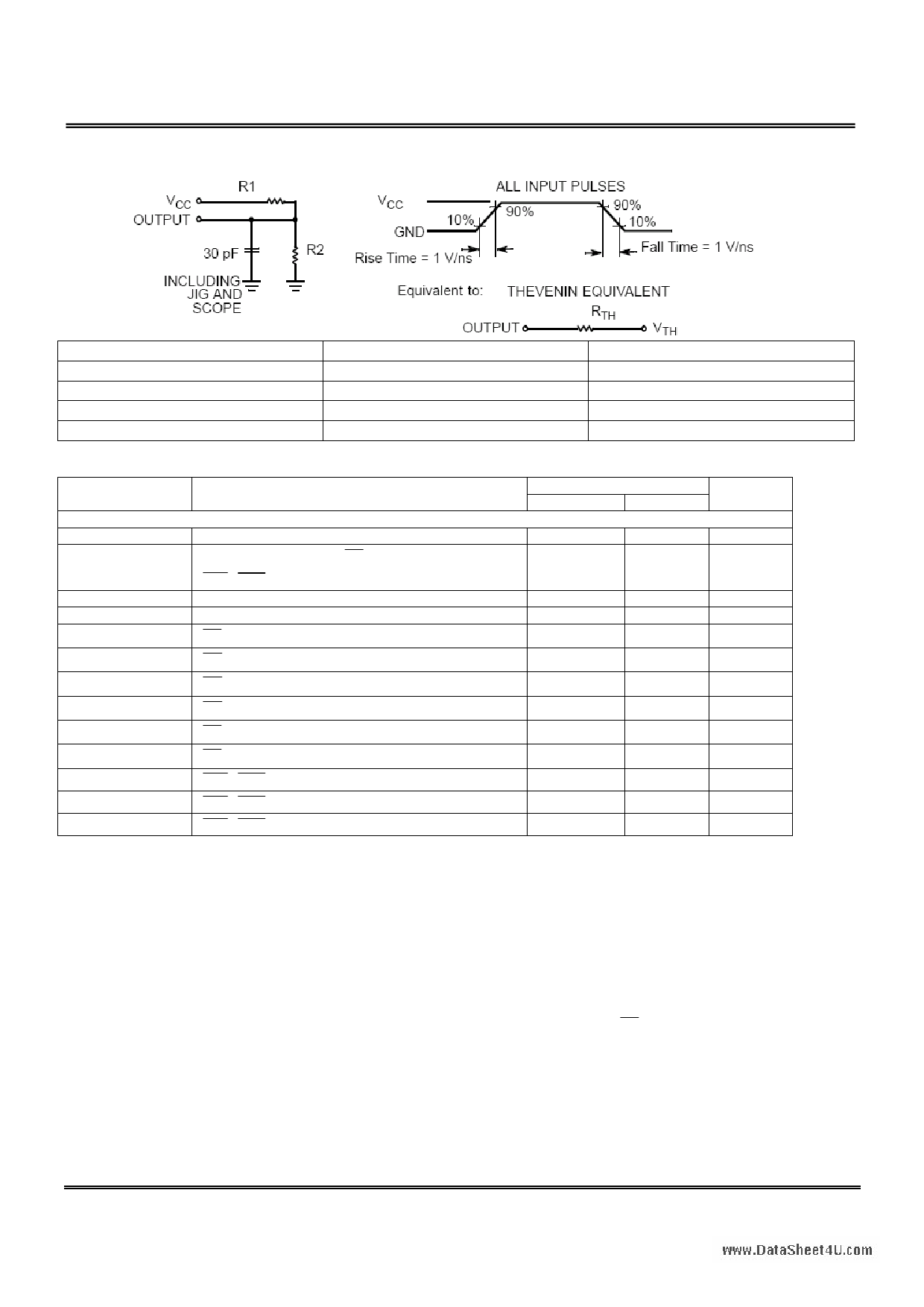

AC Test Loads and Waveforms

www.DataSheet4U.com

M24L16161DA

Parameters

R1

R2

RTH

VTH

3.0V VCC

26000

26000

13000

1.50

Unit

Ω

Ω

Ω

V

Switching Characteristics Over the Operating Range[9, 10, 11, 14, 15]

Parameter

Read Cycle

tRC[13]

tCD

tAA

tOHA

tACE

tDOE

tLZOE

tHZOE

tLZCE

tHZCE

tDBE

tLZBE

tHZBE

Description

Read Cycle Time

Chip Deselect Time CE1 =HIGH or CE2=LOW,

BLE / BHE High Pulse Time

Address to Data Valid

Data Hold from Address Change

CE LOW to Data Valid

OE LOW to Data Valid

OE LOW to Low Z[10, 11, 12]

OE HIGH to High Z[10, 11, 12]

CE LOW to Low Z[10, 11, 12]

CE HIGH to High Z[10, 11, 12]

BLE / BHE LOW to Data Valid

BLE / BHE LOW to Low Z[10, 11, 12]

BLE / BHE HIGH to High Z[10, 11, 12]

Min.

70

15

5

5

10

5

-70

Max.

40000

70

70

35

25

25

70

25

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Notes:

9. Test conditions for all parameters other than tri-state parameters assume signal transition time of 1 ns/V, timing reference

levels of VCC(typ.)/2, input pulse levels of 0V to VCC, and output loading of the specified IOL/IOH as shown in the “AC Test Loads

and Waveforms” section.

10. At any given temperature and voltage conditions tHZCE is less than tLZCE, tHZBE is less than tLZBE, tHZOE is less than tLZOE, and

tHZWE is less than tLZWE for any given device. All low-Z parameters will be measured with a load capacitance of 30 pF (3V).

11. tHZOE, tHZCE, tHZBE, and tHZWE transitions are measured when the outputs enter a high-impedance state.

12. High-Z and Low-Z parameters are characterized and are not 100% tested.

13 .If invalid address signals shorter than min. tRC are continuously repeated for 40 µs, the device needs a normal read timing

(tRC) or needs to enter standby state at least once in every 40 µs.

14. In order to achieve 70-ns performance, the read access must be Chip Enable ( CE1 or CE2) controlled. That is, the

addresses must be stable prior to Chip Enable going active.

Elite Semiconductor Memory Technology Inc.

Publication Date : Jul. 2007

Revision : 1.0

5/12

5 Page

ESMT

Ordering Information

Speed (ns) Ordering Code

70 M24L16161DA -70BIG

www.DataSheet4U.com

M24L16161DA

Package Type

48-ball Very Fine Pitch BGA (6 x 8 x 1 mm) (Pb-Free)

Operating Range

Industrial

Package Diagrams

48-ball VFBGA (6 x 8 x 1 mm)

Elite Semiconductor Memory Technology Inc.

Publication Date : Jul. 2007

Revision : 1.0

11/12

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet M24L16161DA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M24L16161DA | 16-Mbit (1M x 16) Pseudo Static RAM | Elite Semiconductor Memory Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |