|

|

PDF PCA9703 Data sheet ( Hoja de datos )

| Número de pieza | PCA9703 | |

| Descripción | 18 V Tolerant SPI 16-bit GPI With Maskable INT | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PCA9703 (archivo pdf) en la parte inferior de esta página. Total 27 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

PCA9703

18 V tolerant SPI 16-bit GPI with maskable INT

Rev. 01 — 23 February 2010

Product data sheet

1. General description

The PCA9703 is a low power 18 V tolerant SPI General Purpose Input (GPI) shift register

designed to monitor the status of switch inputs. It generates an interrupt when one or

more of the switch inputs change state but allows selected inputs to not generate

interrupts using the interrupt masking feature. The input level is recognized as a HIGH

when it is greater than 0.8 × VDD and as a LOW when it is less than 0.55 × VDD (minimum

LOW threshold of 2.5 V at 5 V node). The PCA9703 can monitor up to 16 switch inputs.

The falling edge of the CS pin samples the input port status and clears the interrupt. When

CS is LOW, the rising edge of the SCLK loads the shift register and shifts the value out of

the shift register. The serial input is sampled on the falling edge of SCLK. The contents of

the shift register are loaded into the interrupt mask register of the device on the rising

edge of CS.

Each of the input ports has a 18 V breakdown ESD protection circuit, which dumps the

ESD/overvoltage current to ground. When used with a series resistor (minimum 100 kΩ),

the input can connect to a 12 V battery and support double battery, reverse battery, 27 V

jump start and 40 V load dump conditions in automotive applications. Higher voltages can

be tolerated on the inputs depending on the series resistor used to limit the input current.

The INT_EN pin is used to both enable the GPI pins and to enable the INT output pin to

minimize battery drain in pull-up cycled applications. The SDIN pull-down prevents

floating nodes when the device is used in daisy-chain applications.

With both the high breakdown voltage and high ESD, this device is useful for both

automotive (AEC-Q100 compliance available) and mobile applications.

2. Features

16 general purpose input ports

18 V tolerant input ports with 100 kΩ external series resistor

Input LOW threshold 0.55 × VDD with minimum of 2.5 V at VDD = 4.5 V

Input hysteresis 0.04 × VDD with minimum of 180 mV at VDD = 4.5 V

Open-drain interrupt output

Interrupt enable pin (INT_EN) disables GPI pins and interrupt output

Interrupt-masking feature allows no interrupt generation from selected inputs

VDD range: 4.5 V to 5.5 V

IDD is very low 2.5 μA maximum

SPI serial interface with speeds up to 5 MHz

SPI supports daisy-chain connection for large switch numbers

AEC-Q100 compliance available

1 page

NXP Semiconductors

www.DataSheet4U.com

PCA9703

18 V tolerant SPI 16-bit GPI with maskable INT

7. Functional description

PCA9703 is a 16-bit General Purpose Input (GPI) with an open-drain interrupt output

designed to monitor switch status. By putting an external 100 kΩ series resistor at the

input port, the device allows the input to tolerate momentary double 12 V battery, reverse

battery, 27 V jump start or 40 V load dump conditions. The interrupt output is asserted

when an input port status changes, the input is not masked and the interrupt output is

enabled. The open-drain interrupt output is enabled when INT_EN is HIGH and disabled

when INT_EN is LOW. The INT_EN also enables the GPI pins when it is HIGH. In cyclic

pull-up applications the GPI pull-ups should be active before the INT_EN is taken HIGH

and the INT output should only be sampled after transient conditions have settled.

Additionally, interrupts can be disabled in software by using the interrupt mask feature.

The input port status is accessed via the 4-wire SPI interface.

Upon power-up, the power-up reset cell clears all the registers, resulting in all zeros in

both the input status register and the interrupt mask register. Since a zero in the interrupt

mask register masks the interrupt from that pin, there will not be any interrupts generated.

After power-up it is necessary to access the PCA9703 through the SPI pins in order to

activate the interrupt for any GPI pins. When the PCA9703 is read over the SPI wires, the

input conditions are clocked into the input status register on the CS falling edge. Since the

inputs and the input status register now match, no interrupt is generated and any

pre-existing interrupt is cleared. The input status register data is parallel loaded into the

shift register on the first rising edge of the SCLK. The serial input data is captured on the

opposite clock edge so that there is a 1⁄2 clock cycle hold time. The set-up time is

diminished by the propagation time so the SCLK falling edge to rising edge must be long

enough to provide sufficient set-up time. Successive clock cycles on the SCLK pin clock

the data out of the PCA9703 and new data from the SDIN into the shift register. There is

no limit to the number of clock cycles that can be applied with the CS LOW, however

sufficient clock cycles should be used to both shift out all of the GPI data and shift in the

new interrupt mask data to the correct position with the MSB first before the CS rising

edge.

For cyclic switch bias applications the switch bias should be applied first, then after the

input voltage is settled the general purpose inputs are switched on by taking the INT_EN

HIGH. This also enables the interrupt output, which will only indicate an interrupt if the GPI

data does not match the input status register on a bit that is enabled by the interrupt mask

register value. If an interrupt is generated, the pull-up should remain active and the

INT_EN should remain active and the SPI pins are used to update the input status register

and read the data out. They are also used to store the new interrupt mask on the rising

edge of CS. After the SPI transaction is complete the INT_EN is taken LOW to turn the

inputs off and disable the INT output. Then the GPI pull-ups can be turned off. The GPI

pins are specifically designed so that any ESD/overstress current flows to ground, not

VDD. They are also specifically designed so that if the input voltage returns to the same

value after pull-up cycling as before the input pull-up cycling, before the input is enabled it

will be detected as the same state.

If the VDD falls below the 4.5 V minimum specified supply voltage, the input threshold will

move down since they are a function of the VDD voltage. The input status register and the

interrupt mask register retain their values to below VDD = 2.0 V and power-down can only

be used to generate a power-up reset if the VDD falls below 0.2 V before returning to the

operating range.

PCA9703_1

Product data sheet

Rev. 01 — 23 February 2010

© NXP B.V. 2010. All rights reserved.

5 of 27

5 Page

NXP Semiconductors

www.DataSheet4U.com

PCA9703

18 V tolerant SPI 16-bit GPI with maskable INT

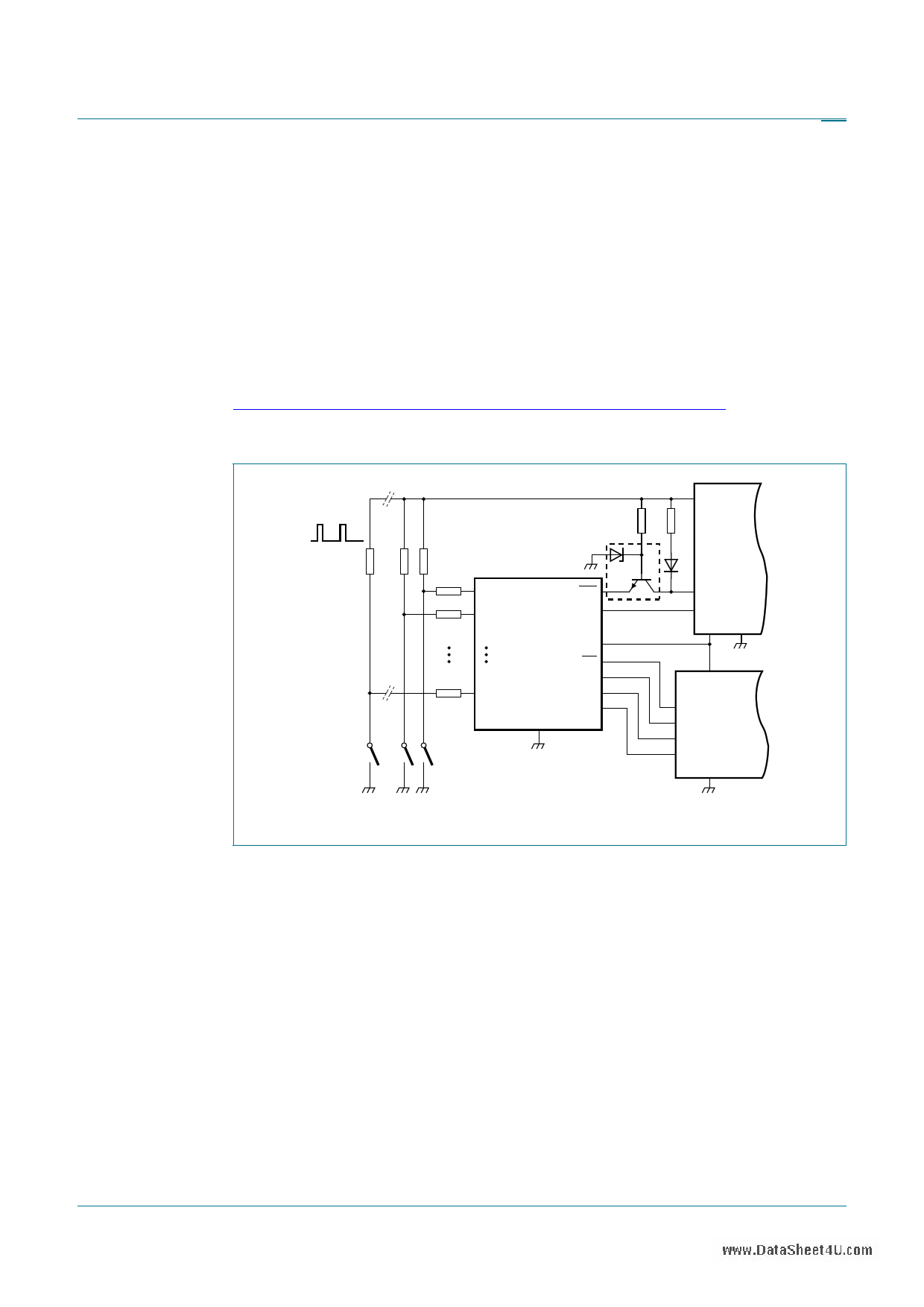

8.2.1 SBC wake port extension with cyclic biasing

System Basis Chips (SBC) offer many functions needed for in-vehicle networking

solutions. Some of the features built into SBC are:

• Transceivers (HS-CAN, LIN 2.0)

• Scalable voltage regulators

• Watchdog timers; wake-up function

• Fail-safe function

For more information on SBC, refer to

http://www.nxp.com/index.html#/pip/pip=[pfp=53482]|pp=[t=pfp,i=53482].

8.2.1.1 UJA106x with PCA9703, standby

alternate

PVR100AD-B5V0

V3

UJA106x

IN0 INT

IN1 INT_EN

PCA9703

VDD

IN15

CS

SDIN

SDOUT

SCLK

VSS

WAKE

V2

V1 GND

VCC

CSN

MOSI

μC

MISO

SCLK

GND

002aae027

Fig 7. UJA106x with PCA9703 with supplied μC (standby)

• PCA9703 fits to SBC UJA106x and UJA107x family

• PCA9703 can be powered by V1 of SBC

• Extends the SBC with 16 additional wake inputs

• μC can be set to stop-mode during standby to save ECU standby current. SBC with

GPI periodically monitors the wake inputs

– Cyclic bias via V3

– Very low system current consumption even with clamped switches

– Interrupt enable control via V2

PCA9703_1

Product data sheet

Rev. 01 — 23 February 2010

© NXP B.V. 2010. All rights reserved.

11 of 27

11 Page | ||

| Páginas | Total 27 Páginas | |

| PDF Descargar | [ Datasheet PCA9703.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PCA9701 | (PCA9701 / PCA9702) 18 V tolerant SPI 16-bit/8-bit GPI | NXP Semiconductors |

| PCA9702 | (PCA9701 / PCA9702) 18 V tolerant SPI 16-bit/8-bit GPI | NXP Semiconductors |

| PCA9703 | 18 V Tolerant SPI 16-bit GPI With Maskable INT | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |