|

|

PDF MAX3945 Data sheet ( Hoja de datos )

| Número de pieza | MAX3945 | |

| Descripción | SFP+ Dual-Path Limiting Amplifier | |

| Fabricantes | Maxim Integrated Products | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX3945 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

19-5144; Rev 0; 2/10

EVAALVUAAILTAIOBNLEKIT

www.DataSheet4U.com

1.0625Gbps to 11.3Gbps,

SFP+ Dual-Path Limiting Amplifier

General Description

The MAX3945 is a +3.3V, multirate, low-power limiting

amplifier optimized for Fibre Channel and Ethernet trans-

mission systems at data rates up to 11.3Gbps. The high-

sensitivity limiting amplifier limits the signal generated by

a transimpedance amplifier into a CML-level differential

output signal. All differential inputs and outputs (I/O) are

optimally back terminated for 50I transmission line PCB

design. The MAX3945’s dual-path limiting amplifier has

programmable filtering to optimize sensitivity for differ-

ent data rates and to suppress relaxation oscillations

that could occur in some optical systems. The MAX3945

incorporates two loss-of-signal (LOS) circuits and a pro-

grammable time mask for the LOS output.

A 3-wire digital interface reduces the pin count and

enables control of LOS threshold, LOS polarity, LOS

mode, CML output level, input offset correction, receive

(Rx) polarity, Rx input filter, and Rx deemphasis without

the need for external components.

The MAX3945 is packaged in a 3mm x 3mm, 16-pin

TQFN package.

Applications

1x/2x/4x/8x SFF/SFP/SFP+ MSA Fibre-Channel

Optical Transceiver

10GBASE-SR/LR SFP+ Optical Transceiver

10G PON ONU

Ordering Information

PART

TEMP RANGE

PIN-PACKAGE

MAX3945ETE+

-40NC to +85NC

16 TQFN-EP*

+Denotes a lead(Pb)-free/RoHS-compliant package.

*EP = Exposed pad.

Typical Application Circuit appears at end of data sheet.

Features

S 130mW Power Dissipation Enables < 1W SFP+

Modules

S Enables Single-Module Design Compliance

with 1000BASE-SX/LX and 10GBASE-SR/LR

Specifications

S -25.3dBm Optical Sensitivity at 1.25Gbps Using a

10.32Gbps ROSA

S Selectable 1GHz/2GHz/2.5GHz/3GHz Input Filters

at RATE_SEL = 0 Setting

S Supports SFF-8431 SFP+ MSA and SFF-8472

Digital Diagnostic

S Total Power Dissipation of 130mW at 3.3V Power

Supply with RSSI Monitor-Based LOS

S Total Power Dissipation of 154mW at 3.3V Power

Supply with Rx Input-Based LOS

S 4mVP-P Input Sensitivity at 11.3Gbps

S 4psP-P DJ at 11.3Gbps with RATE_SEL = 1

S 4psP-P DJ at 8.5Gbps with RATE_SEL = 1

S 5psP-P DJ at 4.25Gbps with RATE_SEL = 0,

BW1 = 1, BW0 = 1

S 9.0psP-P DJ at 1.25Gbps with RATE_SEL = 0,

BW1 = 0, BW0 = 0

S 26ps Rise and Fall Time with RATE_SEL = 1

S 52ps Rise and Fall Time with RATE_SEL = 0

S CML Output with Level Adjustment and Squelch

Mode

S Programmable CML Output Deemphasis

S CML Output Polarity Select

S LOS Polarity Select

S Programmable Masking Time for the LOS Output

S LOS Assert/Deassert Level Adjustment

S Choice of Rx Input-Based LOS or RSSI Monitor-

Based LOS

S 3-Wire Digital Interface Compatible with Maxim’s

SFP+ Family of Products

________________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

1 page

www.DataSheet4U.com

1.0625Gbps to 11.3Gbps,

SFP+ Dual-Path Limiting Amplifier

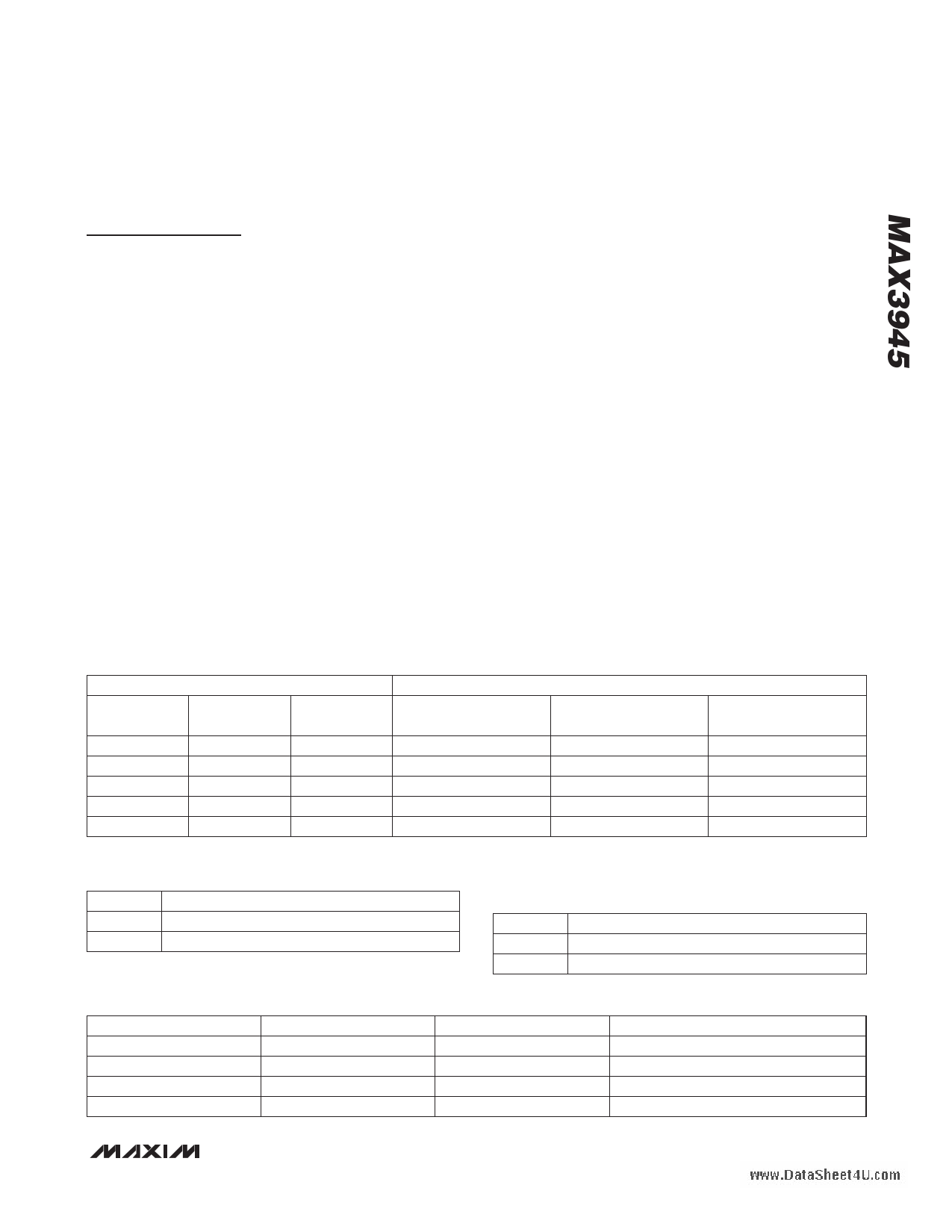

ELECTRICAL CHARACTERISTICS (continued)

(VCC = 2.85V to 3.63V, CML receiver output is AC-coupled to differential 100I load, CCAZ = 0.1FF, TA = -40NC to +85NC. Registers

are set to default values, unless otherwise noted. Typical values are at VCC = 3.3V, TA = +25NC, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

OUTPUT LEVEL VOLTAGE DAC (SET_CML)

100I differential resistive load,

RXDE_EN = 0

Full-Scale Voltage

VFS 100I differential resistive load,

RATE_SEL = 1, RXDE_EN = 1, RXDE1 = 1,

RXDE0 = 1 (maximum deemphasis)

MIN

TYP MAX UNITS

1192

828

mVP-P

Resolution

100I differential resistive load,

RXDE_EN = 0

100I differential resistive load,

RATE_SEL = 1, RXDE_EN = 1, RXDE1 = 1,

RXDE0 = 1 (maximum deemphasis)

4.5

3.3

mVP-P

Integral Nonlinearity

INL SET_CML[7:0] > 60d

LOS THRESHOLD VOLTAGE DAC (SET_LOS)

Full-Scale Voltage

VFS

LOS1_EN = 1, LOS2_EN = 0

LOS1_EN = 0, LOS2_EN = 1

Resolution

LOS1_EN = 1, LOS2_EN = 0

LOS1_EN = 0, LOS2_EN = 1

Integral Nonlinearity

INL SET_LOS[5:0] > 3d

CONTROL I/O SPECIFICATIONS

LOS Output High Voltage

VOH

RLOS = 4.7kI to 10kI to VCC

LOS Output Low Voltage

VOL RLOS = 4.7kI to 10kI to VCC

3-WIRE DIGITAL I/O SPECIFICATIONS (SDA, CSEL, SCL)

Input High Voltage

VIH

Input Low Voltage

VIL

Input Hysteresis

VHYST

Input Leakage Current

IIL,IH

VIN = 0V or VCC, internal pullup or

pulldown (75kI typ)

Q0.9

LSB

96

98

1.52

1.56

Q0.7

mVP-P

mV

mVP-P

mV

LSB

VCC -

0.5

0

VCC

V

0.4 V

2.0 VCC

0.8

0.082

85

V

V

V

FA

Output High Voltage

VOH External pullup of 4.7kI to VCC

Output Low Voltage

VOL External pullup of 4.7kI to VCC

3-WIRE DIGITAL INTERFACE TIMING CHARACTERISTICS (see Figure 5)

SCL Clock Frequency

SCL Pulse-Width High

SCL Pulse-Width Low

SDA Setup Time

SDA Hold Time

fSCL

tCH

tCL

tDS

tDH

SCL Rise to SDA Propagation

Time

tD

CSEL Pulse-Width Low

tCSW

VCC -

0.5

0

VCC

0.4

0 400 1000

500

500

100

100

5

500

V

V

kHz

ns

ns

ns

ns

ns

ns

_______________________________________________________________________________________ 5

5 Page

www.DataSheet4U.com

1.0625Gbps to 11.3Gbps,

SFP+ Dual-Path Limiting Amplifier

Detailed Description

The MAX3945 is designed to operate from 1.0625Gbps

to 11.3Gbps. It consists of a dual-path limiter, offset-

correction circuitry, CML output stage, and LOS circuitry.

The characteristics of the MAX3945 can be controlled

through the on-chip 3-wire interface. The registers that

control the part’s functionality are RXCTRL1, RXCTRL2,

RXSTAT, SET_CML, SET_LOS, MODECRTL, and SET_

LOSTIMER. The MAX3945 provides integrated DACs to

allow the use of low-cost controller ICs. Figure 1 shows

simplified input and output structures.

Dual-Path Limiter

The limiting amplifier features a low data-rate path

(1.0625Gbps to 4.25Gbps) and a high data-rate path

(up to 11.3Gbps), allowing for overall system optimiza-

tion. Figure 2 shows the functional diagram. Data path

selection is controlled by the RATE_SEL bit. The low

data-rate path further features a programmable filter

that provides optimization for 1.0625Gbps, 1.25Gbps,

2.125Gbps, and 4.25Gbps operation. It is important to

tailor the bandwidth of the first stages to get the best

receive sensitivity and to reduce the maximum receive

bandwidth for a given data rate. Table 1 summarizes

the RATE_SEL, BW1, and BW0 control bit functions. The

high data-rate mode (RATE_SEL = 1) is recommended

for operation up to 11.3Gbps.

The polarity of ROUT+/ROUT- relative to RIN+/RIN- is

programmed by the RX_POL bit, as shown in Table 2.

Offset-Correction Circuitry

The offset-correction circuitry is provided to remove

PWD caused by intrinsic offset voltages within the dif-

ferential amplifier stages. An external 0.1FF capacitor

connected between the CAZ pin and ground sets the

offset-correction loop cutoff frequency to approximately

2kHz when RATE_SEL = 0 and to approximately 0.7kHz

when RATE_SEL = 1. The offset-correction loop can be

disabled using the AZ_EN bit, as shown in Table 3.

CML Output Stage

CML Output Enable and Squelch

The CML output stage is optimized for differential 100I

loads. The output stage is controlled by a combination of

the RX_EN and SQ_EN bits and the internal LOS status.

See Table 4.

Table 1. Rate Select and Bandwidth Control

BW1

0

0

1

1

X

RXCTRL1[3:1]

BW0

0

1

0

1

X

RATE_SEL

0

0

0

0

1

OPERATION MODE DESCRIPTION

DATA RATE

(Gbps)

FILTER BANDWIDTH

(MHz)

RISE/FALL TIME

(ps)

1.0625 to 1.25

1000

52

2.125

2100

52

2.125

2500

52

4.25

3000

52

11.3

9000

26

Table 2. Signal Polarity Control

RX_POL

0

1

OPERATION MODE DESCRIPTION

Inversed polarity of the differential signal path

Normal polarity of the differential signal path

Table 3. Offset-Correction Enable/Disable

Control

AZ_EN

0

1

OPERATION MODE DESCRIPTION

Autozero loop is disabled

Autozero loop is enabled

Table 4. CML Output Stage Operation Modes

RX_EN

0

1

1

1

SQ_EN

X

0

1

1

LOS STATUS

X

X

0

1

OPERATION MODE DESCRIPTION

CML output disabled

CML output enabled

CML output enabled

CML output disabled

______________________________________________________________________________________ 11

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet MAX3945.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX394 | Low-Voltage / Quad / SPDT / CMOS Analog Switch | Maxim Integrated |

| MAX3940 | 10Gbps EAM Driver | Maxim Integrated Products |

| MAX3941 | 10Gbps EAM Driver with Integrated Bias Network | Maxim Integrated |

| MAX3941ETG | 10Gbps EAM Driver with Integrated Bias Network | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |