|

|

PDF TDF8599 Data sheet ( Hoja de datos )

| Número de pieza | TDF8599 | |

| Descripción | I2C-bus controlled dual channel 43 W/2 W single channel 85 W/1 W class-D power amplifier | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TDF8599 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

TDF8599

I2C-bus controlled dual channel 43 W/2 Ω single channel

85 W/1 Ω class-D power amplifier with load diagnostics

Rev. 01 — 13 November 2008

Product data sheet

1. General description

www.DataSheet4U.com

The TDF8599 is a dual Bridge-Tied Load (BTL) car audio amplifier comprising an

NDMOST-NDMOST output stage based on SOI BCDMOS technology. Low dissipation

enables the TDF8599 high-efficiency, class-D amplifier to be used with a smaller heat sink

than those normally used with standard class-AB amplifiers.

The TDF8599 can operate in either non-I2C-bus mode or I2C-bus mode. When in I2C-bus

mode, DC load detection results and fault conditions can be easily read back from the

device. Up to five I2C-bus addresses can be selected when an external resistor is

connected to pin ADS.

When pin ADS is short circuited to ground, the TDF8599 operates in non-I2C-bus mode.

Switching between Operating mode and Mute mode in non-I2C-bus mode is only possible

using pins EN and SEL_MUTE.

2. Features

I High-efficiency

I Low quiescent current

I Operating voltage from 8 V to 18 V

I Two 4 Ω/2 Ω capable BTL channels or one 1 Ω capable BTL channel

I Differential inputs

I Supports I2C-bus mode with five I2C-bus addresses or non-I2C-bus mode operation

I Clip detect

I Independent short circuit protection for each channel

I Advanced short circuit protection for load, GND and supply

I Load dump protection

I Thermal foldback and thermal protection

I DC offset protection

I Selectable AD or BD modulation

I Parallel channel mode for high current drive capability

I Advanced clocking:

N Switchable oscillator clock source: internal (master) or external (slave)

N Spread spectrum mode

N Phase staggering

N Frequency hopping

I No ‘pop noise’ caused by DC output offset voltage

1 page

NXP Semiconductors

TDF8599

Class-D power amplifier with load diagnostics

www.DataSheet4U.com

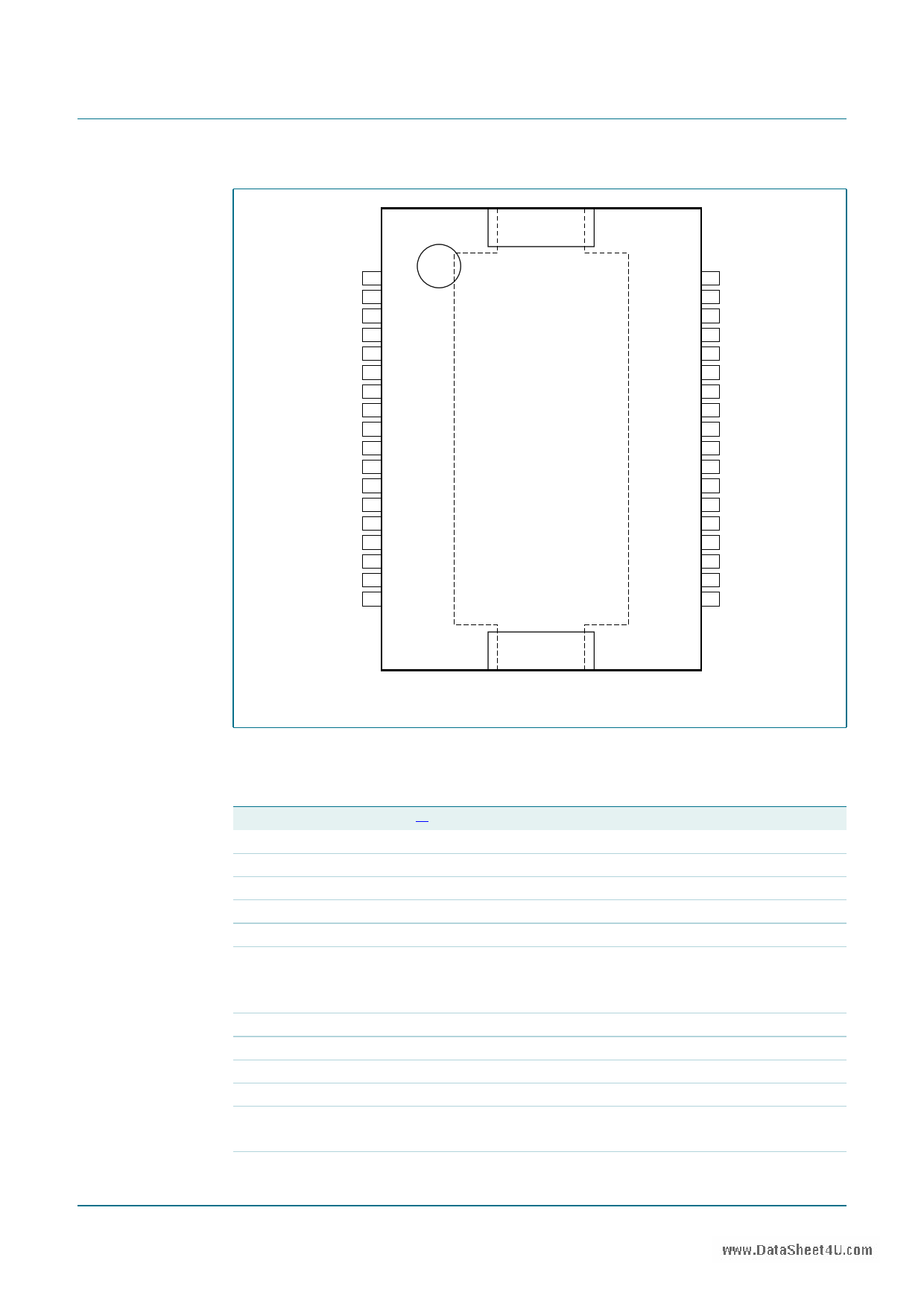

IN1P 1

IN1N 2

IN2P 3

IN2N 4

ACGND 5

EN 6

SEL_MUTE 7

SVRR 8

AGND 9

VDDA 10

ADS 11

MOD 12

CLIP 13

DIAG 14

SDA 15

SCL 16

SSM 17

OSCSET 18

TDF8599TD

36 GNDD/HW

35 VDDD

34 VSTAB1

33 OUT1N

32 BOOT1N

31 VP1

30 PGND1

29 BOOT1P

28 OUT1P

27 OUT2P

26 BOOT2P

25 PGND2

24 VP2

23 BOOT2N

22 OUT2N

21 VSTAB2

20 DCP

19 OSCIO

001aai768

Fig 3. Heatsink down (top view) pin configuration TDF8599TD

7.2 Pin description

Table 3.

Symbol

IN1P

IN1N

IN2P

IN2N

ACGND

EN

Pin description

Pin Type[1]

1I

2I

3I

4I

5I

6I

SEL_MUTE

SVRR

AGND

VDDA

ADS

7I

8I

9G

10 P

11 I

MOD

12 I

Description

channel 1 positive audio input

channel 1 negative audio input

channel 2 positive audio input

channel 2 negative audio input

decoupling for input reference voltage

enable input:

non-I2C-bus mode: switch between off and Mute mode

I2C-bus mode: off and Standby mode

select mute or on (unmute)

decoupling for internal half supply reference voltage

analog supply ground

analog supply voltage

non-I2C-bus mode: connected to ground

I2C-bus mode: selection and address selection pin

modulation mode, phase shift and parallel mode select

TDF8599_1

Product data sheet

Rev. 01 — 13 November 2008

© NXP B.V. 2008. All rights reserved.

5 of 52

5 Page

NXP Semiconductors

TDF8599

Class-D power amplifier with load diagnostics

www.DataSheet4U.com

directly. Values for CPLL_s, CPLL_p and RPLL depend on the desired loop bandwidth

(BWPLL) of the PLL. RPLL is given by: RPLL = 8.4 × BWPLL Ω. The corresponding values for

CPLL_s and CPLL_p are given by:

CPLL_p = -R---P----L--L--0--×-.--0--B-3---2W------P---L---L- [F ]

(3)

Remark: CPLL_P is only needed when π/4 phase shift is selected. See Section 8.4.2 for

more detailed information.

CPLL_s = -R---P----L--L----×-0---.-B-8---W------P---L---L-[F ]

(4)

When pin OSCIO is connected to a clock-master with Spread spectrum mode enabled,

the PLL loop bandwidth BWPLL should be 100 × fSSM.

100 µA

OSCSET

100 µA

OSCSET

SSM

PLL

PLL

SSM

CPLL_s

RPLL

CPLL_P(1)

001aai776

001aai777

a. Off

Fig 9. Phase lock operation

b. On

See Table 7 for all oscillator modes.

Table 7. Oscillator modes

OSCSET pin OSCIO pin

Rosc > 26 kΩ

Rosc > 26 kΩ

Rosc = 0 Ω

Rosc = 0 Ω

output

output

input

input

SSM pin

Cssm

shorted to AGND

CPLL + RPLL

shorted to AGND

Oscillator modes

master, spread spectrum

master, no spread spectrum

slave, PLL enabled

slave, PLL disabled

8.4 Operation mode selection

Pin MOD is used to select specific operation modes. The resistor (RMOD) connected

between pins MOD and AGND determines the operation mode. The mode of operation

depends on whether non-I2C-bus mode or I2C-bus mode is active. This is in turn

determined by the resistor value connected between pins ADS and AGND.

TDF8599_1

Product data sheet

Rev. 01 — 13 November 2008

© NXP B.V. 2008. All rights reserved.

11 of 52

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet TDF8599.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TDF8590TH | 2 x 80 W SE or 1 x 160 W BTL class-D amplifer | NXP Semiconductors |

| TDF8591TH | class-D amplifier | NXP Semiconductors |

| TDF8599 | I2C-bus controlled dual channel 43 W/2 W single channel 85 W/1 W class-D power amplifier | NXP Semiconductors |

| TDF8599A | single channel 250 W/2 W class-D power amplifier | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |