|

|

PDF ICS874001I-05 Data sheet ( Hoja de datos )

| Número de pieza | ICS874001I-05 | |

| Descripción | PCI EXPRESS JITTER ATTENUATOR | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS874001I-05 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

PCI EXPRESS™ JITTER ATTENUATOR

www.DataSheet4U.com

ICS874001I-05

GENERAL DESCRIPTION

The ICS874001I-05 is a high performance Jitter

ICS Attenuator designed for use in PCI Express™ sys-

HiPerClockS™ tems. In some PCI Express systems, such as those

found in desktop PCs, the PCI Express clocks are

generated from a low bandwidth, high phase noise

PLL frequency synthesizer. In these systems, a jitter

attenuator may be required to attenuate high frequency random

and deterministic jitter components from the PLL synthesizer

and from the system board. The ICS874001I-05 has a bandwidth

of 6MHz with <1dB peaking, easily meeting PCI Express Gen2

PLL requirements.

The ICS874001I-05 uses IDT’s 3rd Generation FemtoClockTM

PLL technology to achive the lowest possible phase noise.

The device is packaged in a small 20-pin TSSOP package,

making it ideal for use in space constrained applications such as

PCI Express add-in cards.

FEATURES

• One differential LVDS output pair

• One differential clock input

• CLK and nCLK supports the following input types:

LVPECL, LVDS, LVHSTL, SSTL, HCSL

• Output frequency range: 98MHz - 640MHz

• Input frequency range: 98MHz - 128MHz

• VCO range: 490MHz - 640MHz

• Cycle-to-cycle jitter: 50ps (maximum)

• 3.3V operating supply

• PCI Express (2.5Gb/s) and Gen 2 (5 Gb/s) jitter compliant

• -40°C to 85°C ambient operating temperature

• Available in lead-free (RoHS 6) package

PIN ASSIGNMENT

PLL_SEL

nc

nc

nc

MR

nc

F_SEL1

VDDA

F_SEL0

VDD

1

2

3

4

5

6

7

8

9

10

20 nc

19 VDDO

18 Q

17 nQ

16 nc

15 nc

14 GND

13 nCLK

12 CLK

11 OE

ICS874001I-05

20-Lead TSSOP

6.5mm x 4.4mm x 0.925mm package body

G Package

Top View

IDT™ / ICS™ PCI EXPRESS JITTERATTENUATOR

1

ICS874001AGI-05 REV. A APRIL 20, 2009

1 page

ICS874001I-05

PCI EXPRESS™ JITTER ATTENUATOR

www.DataSheet4U.com

TABLE 5. AC CHARACTERISTICS, VDD = VDDO = 3.3V ± 0.3V, TA = -40°C TO 85°C

Symbol

Parameter

Test Conditions

Minimum Typical Maximum Units

fMAX

tjit(cc)

Output Frequency

Cycle-to-Cycle Jitter,

NOTE 1

Tj

Phase Jitter Peak-to-Peak;

NOTE 2, 4

TREFCLK_HF_RMS

Phase Jitter RMS;

NOTE 3, 4

TREFCLK_LF_RMS

Phase Jitter RMS;

NOTE 3, 4

100MHz output,

Evaluation Band: 0Hz - Nyquist

(clock frequency/2)

125MHz output,

Evaluation Band: 0Hz - Nyquist

(clock frequency/2)

250MHz output,

Evaluation Band: 0Hz - Nyquist

(clock frequency/2)

500MHz, (1.2MHz –21.9MHz),

Evaluation Band: 0Hz - Nyquist

(clock frequency/2)

100MHz output,

High Band: 1.5MHz - Nyquist

(clock frequency/2)

125MHz output,

High Band: 1.5MHz - Nyquist

(clock frequency/2)

250MHz output,

High Band: 1.5MHz - Nyquist

(clock frequency/2)

500MHz output,

High Band: 1.5MHz - Nyquist

(clock frequency/2)

100MHz output,

Low Band: 10kHz - 1.5MHz

125MHz output,

Low Band: 10kHz - 1.5MHz

250MHz output,

Low Band: 10kHz - 1.5MHz

500MHz output,

Low Band: 10kHz - 1.5MHz

98 640 MHz

50 ps

16.14

ps

15.64

ps

13.16

ps

12.17

ps

1.4 ps

1.39

ps

1.18 ps

1.11

0.33

0.22

0.22

0.22

ps

ps

ps

ps

ps

tR / tF

odc

Output Rise/Fall Time

Output Duty Cycle

20% to 80%

F_SEL[10] ≠ 11

F_SEL[10] = 11

200 600 ps

48 52 %

42 58 %

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the

device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after

thermal equilibrium has been reached under these conditons.

NOTE 1: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 2: Peak-to-peak jitter after system transfer function for the Common Clock Architecture. Maximum limit for PCI Express Gen 1

is 86ps peak-to-peak for a sample size of 106 clock periods. See IDT Application Note,PCI Express Reference Clock Requirements

and also the PCI Express Application section of this datasheet which show each individual transfer function and the overall

composite transfer function.

NOTE 3: RMS jitter after applying the two evaluation bands to the two transfer functions defined in the Common Clock Architecture

and reporting the worst case results for each evaluation band. Maximum limit for PCI Express Generation 2 is 3.1ps rms for

tREFCLK_HF_RMS (High Band) and 3.0ps RMS for tREFCLK_LF_RMS (Low Band). See IDT Application Note,PCI Express Reference Clock

Requirements and also the PCI Express Application section of this datasheet which show each individual transfer function and the

overall composite transfer function.

NOTE 4: Guaranteed only when input clock source is PCI Express and PCI Express Gen 2 compliant.

IDT™ / ICS™ PCI EXPRESS JITTERATTENUATOR

5

ICS874001AGI-05 REV. A APRIL 20, 2009

5 Page

ICS874001I-05

PCI EXPRESS™ JITTER ATTENUATOR

www.DataSheet4U.com

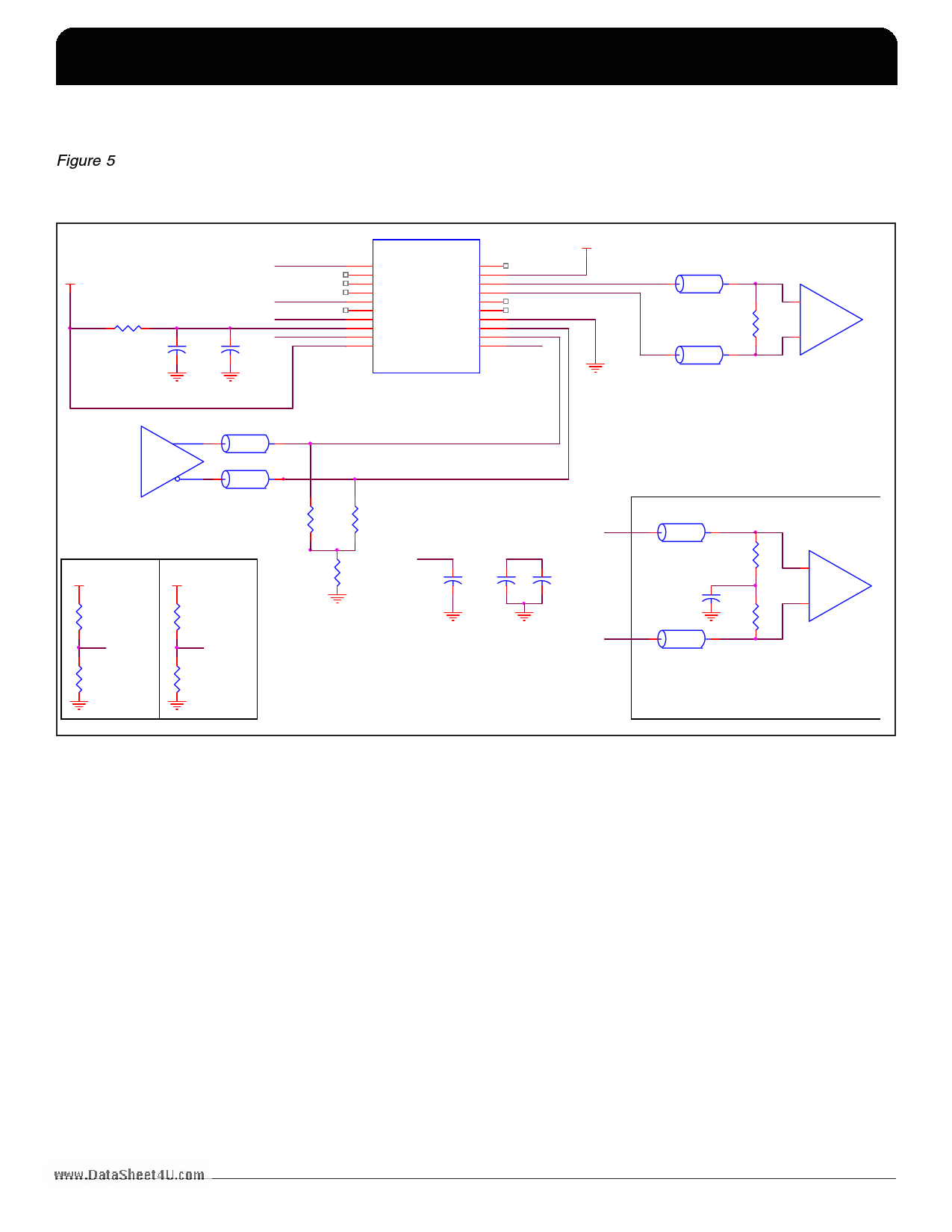

SCHEMATIC EXAMPLE

Figure 5 shows an example of ICS874001I-05 application

schematic. In this example, the device is operated at V =

DD

3.3V. The decoupling capacitors should be located as close

as possible to the power pin. The input is driven by a 3.3V

LVPECL driver.

VDD = 3.3V

VDD

10 R2

VDDA

C1

0.1u

C2

10u

PLL_SEL

MR

F_SEL1

F_SEL0

U1

1

2

PLL_SEL

3 nc

4 nc

5

6

7

8

nc

MR

nc

F_SEL1

9

10

VDDA

F_SEL0

VDD

nc

VDDO

Q

nQ

nc

nc

GND

nCLK

CLK

OE

20

19

18

17

16

15

14

13

12

11

VDDO = 3.3V

VDDO

Q

nQ

nCLK

CLK

OE

GND

Zo = 50 Ohm

Q

Zo = 50 Ohm

nQ

+

R1

100

-

Zo = 50 Ohm

Zo = 50 Ohm

LVPECL Driv er

Logic Control Input Examples

Set Logic

Set Logic

VDD

VDD

Input to '1'

Input to '0'

RU1

1K

To Logic

Input

pins

RD1

Not Install

RU2

Not Install

To Logic

Input

pins

RD2

1K

R6 R7

50 50

R8

50

VDDO (U1:19)

C5

.1uf

VDD(U1:10)

C6

10uf

C7

.1uf

Zo = 50 Ohm

Q

R4

50

C3

0.1uF

R5

Zo = 50 Ohm

50

nQ

Alternate

LVDS

Termination

FIGURE 5. ICS874001I-05 SCHEMATIC LAYOUT

+

-

IDT™ / ICS™ PCI EXPRESS JITTERATTENUATOR

11

ICS874001AGI-05 REV. A APRIL 20, 2009

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet ICS874001I-05.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS874001I-05 | PCI EXPRESS JITTER ATTENUATOR | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |