|

|

PDF AD8384 Data sheet ( Hoja de datos )

| Número de pieza | AD8384 | |

| Descripción | 6-Channel Decimating LCD | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD8384 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

10-Bit, 6-Channel Decimating

www.DataSheet4U.com

LCD DecDriver® with Level Shifters

AD8384

PRODUCT FEATURES

High accuracy, high resolution voltage outputs

10-bit input resolution

Laser trimmed outputs

Fast settling, high voltage drive

30 ns settling time to 0.25% into a 150 pF load

Slew rate 460 V/µs

Outputs to within 1.3 V of supply rails

High update rates

Fast, 100 Ms/s 10-bit input data update rate

Voltage controlled video reference (brightness), offset, and

full-scale (contrast) output levels

Flexible logic

STSQ/XFR allow parallel AD8384 operation

INV bit reverses polarity of video signal

Output short-circuit protection

3.3 V logic, 9 V to 18 V analog supplies

18 V level shifters for panel timing signals

Available in 80-lead 12 mm × 12 mm TQFP E-pad

APPLICATIONS

LCD analog column drivers

PRODUCT DESCRIPTION

The AD8384 DecDriver provides a fast, 10-bit, latched,

decimating digital input that drives six high voltage outputs.

10-bit input words are loaded sequentially into six separate high

speed, bipolar DACs. Flexible digital input format allows several

AD8384s to be used in parallel in high resolution displays. The

output signal can be adjusted for dc reference, signal inversion,

and contrast for maximum flexibility. Integrated level shifters

convert timing signals from a 3 V timing controller to high

voltage for LCD panel timing inputs. Two serial input, 8-bit

DACs are integrated to provide dc reference signals. DAC

addresses and 8-bit data are loaded in one 12-bit serial word.

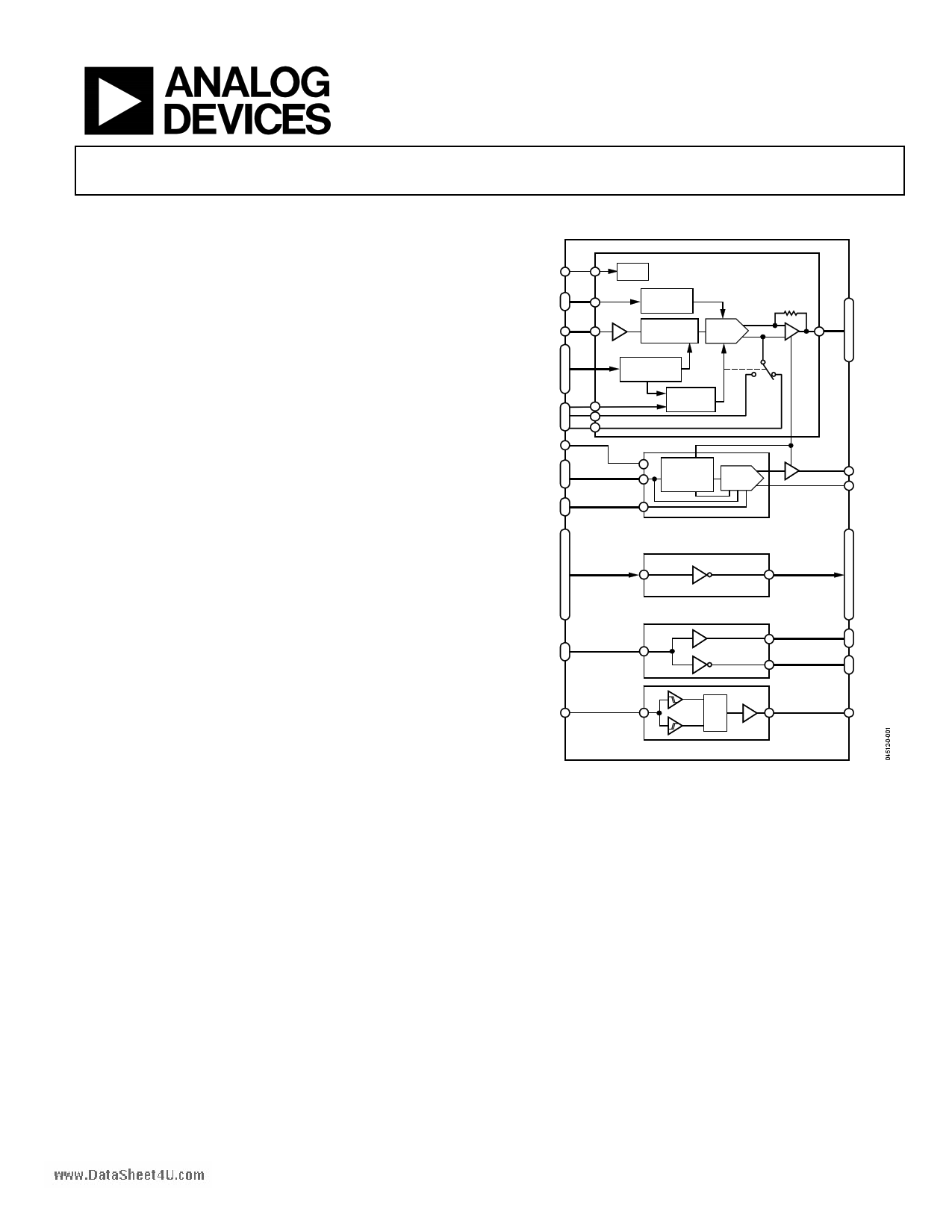

FUNCTIONAL BLOCK DIAGRAM

BYP

BIAS

/VRH

VRL

2

SCALING

CONTROL

/DB(0:9) 10

2-STAGE

LATCH

DACs

R/L

CLK

STSQ

XFR

INV

V1

V2

4/

SEQUENCE

CONTROL

INV

CONTROL

TSTM

SDI

SCL

SEN

SVRH

SVRL

3/

2/

12-BIT

SHIFT

REGISTER

DUAL

DAC

DYIN

DXIN

DIRYIN

DIRXIN

NRGIN

ENBX1IN

ENBX2IN

ENBX3IN

ENBX4IN

9/

CLXIN

CLYIN

2/

MONITI

R

S

Figure 1.

VID0

VID1

/6 VID2

VID3

VID4

VID5

VAO1

VAO2

DY

DX

DIRY

/9 DIRX

NRG

ENBX1

ENBX2

ENBX3

ENBX4

/2 CLX

CLY

/2 CLXN

CLYN

MONITO

AD8384

The AD8384 is fabricated on the 26 V, fast, bipolar XFHV

process developed by Analog Devices, Inc. This process

provides fast input logic, bipolar DACs with trimmed accuracy

and fast settling, high voltage, precision drive amplifiers on the

same chip.

The AD8384 dissipates 1.1 W nominal static power.

The AD8384 is offered in an 80-lead 12 mm × 12 mm TQFP

E-pad package and operates over the 0°C to 85°C commercial

temperature range.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

1 page

AD8384www.DataSheet4U.com

LEVEL SHIFTERS

Table 2. @ 25°C, AVCC = 15.5 V, DVCC = 3.3 V, TA MIN = 0°C, TA MAX = 85°C, VRH = 9.5 V, VRL = V1 = V2 = 7 V,

unless otherwise noted

Parameter

Conditions

Min

Typ Max

LEVEL SHIFTER LOGIC INPUTS

CIN 3

IIH 0.05

IIL –0.6

VTH 1.65

VIH 2.0 DVCC

VIL

DGND

0.8

LEVEL SHIFTER OUTPUTS

RL ≥ 10 kΩ

VOH

AVCC – 0.45

AVCC – 0.25

VOL 0.25 0.45

LEVEL SHIFTER DYNAMIC PERFORMANCE

TA MIN to TA MAX

Output Rise, Fall Times—tr, tf

DX, CLX, CLXN, ENBX(1–4)

CL = 40 pF

18.5 30

DY, CLY, CLYN

CL = 40 pF

40 70

DIRX, DIRY

CL = 40 pF

100 150

NRG

CL = 200 pF

35 50

CL = 300 pF

55 100

Propagation Delay Times—t11, t12, t13, t14

DX, CLX, CLXN, ENBX(1–4)

CL = 40 pF

20 50

DY, CLY, CLYN

CL = 40 pF

29 50

DIRX, DIRY

CL = 40 pF

60 100

NRG

CL = 200 pF

25 55

CL = 300 pF

32

Output Skew

ENBX(1–4)—t15, t16

CL = 40 pF

2

DX to ENBX(1–4)—t16

CL = 40 pF

2

DX to CLX—t15, t16, t17, t18

CL = 40 pF

10

DY to CLY, CLYN—t15, t16, t17, t18

CL = 40 pF

20

Unit

pF

µA

µA

V

V

V

V

V

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

LEVEL SHIFTING EDGE DETECTOR

Table 3. CL = 10 pF, TA MIN to TA MAX, unless otherwise noted

Parameter

VIL Input Low Voltage

VIH Input High Voltage

VTH LH

Input Rising Edge Threshold Voltage

VTH HL

Input Falling Edge Threshold Voltage

VOH Output High Voltage

VOL Output Low Voltage

IIH Input Current High State

IIL Input Current Low State

t19 Input Rising Edge Propagation Delay Time

∆t19 t19 Variation with Temperature

t20 Input Falling Edge Propagation Delay Time

∆t20 t20 Variation with Temperature

tr Output Rise Time

tf Output Fall Time

Min

AGND

AVCC – 2.7

DVCC – 0.45

–2.5

Typ

AGND + 3

AVCC – 3

DVCC – 0.25

0.25

1.2

–1.2

16

2

12

2

5

6

Max

AGND + 2.75

AVCC

0.45

2.5

Unit

V

V

V

V

V

V

µA

µA

ns

ns

ns

ns

ns

ns

Rev. 0 | Page 5 of 24

5 Page

TIMING CHARACTERISTICS

DECDRIVER SECTION

DB(0:9)

10

10 10 2-STAGE 10 DAC

LATCH

AD8384

10 2-STAGE 10 DAC

LATCH

BYP

CLK

STSQ

XFR

R/L

BIAS

SEQUENCE

CONTROL

10 2-STAGE 10 DAC

LATCH

10 2-STAGE 10 DAC

LATCH

10 2-STAGE 10 DAC

LATCH

10 2-STAGE 10 DAC

LATCH

INV INV CONTROL

SCALING

CONTROL

VRH VRL

V1 V2

Figure 4. Block Diagram

VID0

VID1

VID2

VID3

VID4

VID5

tf

CLK

DB(0:9)

AD8384www.DataSheet4U.com

tr

t1

t7

t2

t8

VTH

VTH

STSQ

XFR

CLK

DB(0:9)

t3 t4

VTH

t5 t6

VTH

Figure 5. Input Timing, Even Mode (E/O = HIGH)

t8

t1 t2

t7

VTH

VTH

STSQ

t3 t4

VTH

XFR

t5

t6

VTH

Figure 6. Input Timing, Odd Mode ( E/O = LOW)

CLK

DB(0:9) –8 –7 –6 –5 –4 –3 –2 –1 0 1 2 3 4 5 6 7

STSQ

XFR

INV

V2+VFS

VID(0:5)

V2

50%

t9

50% PIXELS

–6, –5, –4, –3, –2, –1

t9 PIXELS 0, 1, 2, 3, 4, 5

t10

V1

V1–VFS

Figure 7. Output Timing (R/L = Low, E/O = High)

Table 8. Timing Characteristics

Parameter

t1 CLK to Data Setup Time

t2 CLK to Data Hold Time

t3 CLK to STSQ Setup Time

t4 CLK to STSQ Hold Time

t5 CLK to XFR Setup Time

t6 CLK to XFR Hold Time

t7 CLK High Time

t8 CLK Low Time

t9 CLK to VIDx Delay

t10 INV to VIDx Delay

Conditions

Min

0

3

0

3

0

3

3

2.5

10

13

Typ

12

15

Max

14

17

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Rev. 0 | Page 11 of 24

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet AD8384.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD8380 | Decimating LCD Panel Driver | Analog Devices |

| AD8381 | 6-Channel Output DecDriver Decimating LCD Panel Driver | Analog Devices |

| AD8382 | Decimating LCD DecDriver | Analog Devices |

| AD8383 | 6-Channel Output Decimating LCD | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |