|

|

PDF HYB39S13620TQ-6 Data sheet ( Hoja de datos )

| Número de pieza | HYB39S13620TQ-6 | |

| Descripción | Special Mode Registers Two color registers Burst Read | |

| Fabricantes | Siemens Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HYB39S13620TQ-6 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Overview

www.DataSheet4U.com

HYB 39S13620TQ-6/-7/-8

• High Performance:

-6 -7 -7 -8 Units

fCK 166 125 125 125 MHz

latency 3 2 3 3 −

tCK3 6 8 7 8 ns

tAC3 5.5 5.5 5.5 6 ns

• Single Pulsed RAS Interface

• Programmable CAS Latency: 2, 3

• Fully Synchronous to Positive Clock Edge

• Programmable Wrap Sequence:

Sequential or Interleave

• Programmable Burst Length:

1, 2, 4, 8 and full page for sequential

1, 2, 4, 8 for interleave

• Special Mode Registers

• Two color registers

• Burst Read with Single Write Operation

• Block Write and Write-per-Bit Capability

• Byte controlled by DQM0-3

• Auto Precharge and Auto Refresh Modes

• Suspend Mode and Power Down Mode

• 2k refresh cycles/32 ms

• tAC = 5 ns

• tSETUP/tHOLD = 2 ns/1 ns

• Latency 2 @ 125 MHz

• Random Column Address every CLK

(1-N Rule)

• Single 3.3 V ± 0.3 V Power Supply

• LVTTL compatible inputs and outputs

The HYB 39S163200TQ are dual bank Synchronous Graphics DRAM’s (SGRAM) organized as

2 banks × 256 Kbit × 32 with built-in graphics features. These synchronous devices achieve high

speed data transfer rates up to 143 MHz by employing a chip architecture that prefetches multiple

bits and then synchronizes the output data to a system clock. The chip is fabricated with an

advanced 64MBit DRAM process technology.

The device is designed to comply with all JEDEC standards set for synchronous graphics DRAM

products, both electrically and mechanically.

RAS, CAS, WE, DSF and CS are pulsed signals which are examined at the positive edge of each

externally applied clock. Internal chip operating modes are defined by combinations of these

signals. A ten bit address bus accepts address data in the conventional RAS/CAS multiplexing

style. Ten row address bits (A0 - A9) and a bank select BA are strobed with RAS. Column address

bits plus a bank select are strobed with CAS.

Prior to any access operation, the CAS latency, burst length and burst sequence must be

programmed into the device by address inputs during a mode register set cycle. An Auto Precharge

function may be enabled to provide a self-timed row precharge. This is initiated at the end of the

burst sequence. In addition, it features the write per bit, the block write and the masked block write

Semiconductor Group

1

1998-10-01

1 page

HYB 39S16320TQ-6/-7/-8

www.DataSheet4U.com

Signal Pin Description

Pin Type Signal Polarity Function

CLK Input Pulse Positive The system clock input. All of the SGRAM inputs are

Edge sampled on the rising edge of the clock.

CKE

Input Level Active

High

Activates the CLK signal when high and deactivates the

CLK signal when low. By deactivating the clock, CKE low

initiates the Power Down mode, Suspend mode, or the Self

Refresh mode.

CS Input Pulse Active CS enables the command decoder when low and disables

Low the command decoder when high. When the command

decoder is disabled, new commands are ignored but

previous operations continue.

RAS

CAS

WE

Input Pulse Active

Low

When sampled at the positive rising edge of the clock,

CAS, RAS, and WE define the operation to be executed by

the SGRAM.

A0 - A9 Input Level –

During a Bank Activate command cycle, A0-A9 defines the

row address (RA0-RA9) when sampled at the rising clock

edge.

During a Read or Write command cycle, A0-A7 defines the

column address (CA0-CA7) when sampled at the rising

clock edge.

In addition to the column address, CA8 is used to invoke

autoprecharge operation at the end of the burst read or

write cycle. If A8 is high, autoprecharge is selected and BA

defines the bank to be precharged (low = bank A,

high bank B). If A8 is low, autoprecharge is disabled.

During a Precharge command cycle, A8 is used in

conjunction with BA to control which bank(s) to precharge.

If A8 is high, both bank A and bank B will be precharged

regardless of the state of BA. If A8 is low, then BA is used

to define which bank to precharge.

BA Input Level –

Selects which bank is activated. BA low selects bank A and

BA high selects bank B.

DQ0 -

DQ31

Input Level –

Output

Data Input/Output pins operate in the same manner as on

conventional DRAMs, with the exception of the Block Write

function. In this case, the DQx pins perform a masking

operation.

Semiconductor Group

5

1998-10-01

5 Page

HYB 39S16320TQ-6/-7/-8

www.DataSheet4U.com

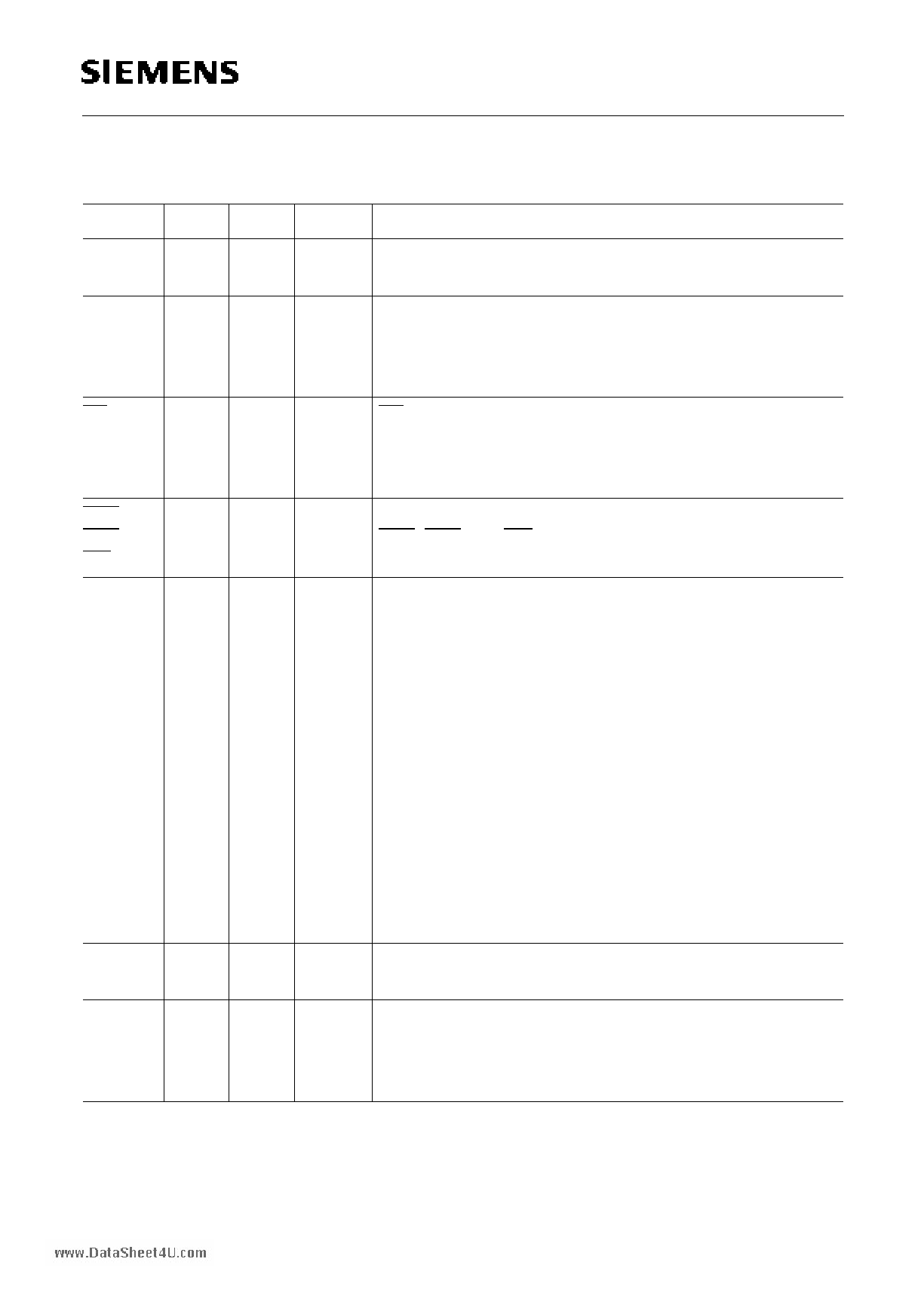

Commands

The Function Truth Table provides a quick reference of available commands.

Operation

CKE

n−1

Device Deselect

(INHBT)

H

No Operation (NOP) H

Load Mode Register H

(LMR)

Load Special Mode H

Register (LSMR)

Row Activate (ACT) H

Row Active with WpB H

(ACTM)

Read (RD)

H

Read with Auto

Precharge (RDA)

H

Write Command

(WR)

H

Write Command with H

Auto Precharge

(WRA)

Block Write (BW)

H

Block Write with Auto H

Precharge (BWA)

Burst Terminate

(BST)

H

Precharge Single

Bank (PRE)

H

Precharge All Banks H

(PREAL)

Auto Refresh (REF) H

Self Refresh Entry

(SREF (EN)

H

Self Refresh Exit

(SREF (EX)

L

L

Power Down Mode

Entry (PDN-EN)

H

H

Power Down Mode

Exit (PDN-EX)

L

CKE

n

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

H

L

H

H

L

L

H

CS

H

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

L

H

L

H

L

X

RAS CAS WE

XXX

HHH

LLL

LLL

L HH

L HH

HL H

HL H

HL L

HL L

HL L

HL L

HHL

L HL

L HL

LLH

LLH

XXX

HHH

XXX

HHH

XXX

DSF DQM BA

XXX

XXX

L XX

HXX

L X BA

H X BA

X X BA

X X BA

L X BA

L X BA

H X BA

H X BA

XXX

X X BA

XXX

XXX

XXX

XXX

XXX

XXX

XXX

XXX

A8 A0 -

A7

XX

XX

OPCODE

OPCODE

Row Addr

Row Addr

L Col.

H Col.

L Col.

H Col.

L Col.

H Col.

XX

LX

HX

XX

XX

XX

XX

XX

XX

XX

Semiconductor Group

11

1998-10-01

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HYB39S13620TQ-6.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HYB39S13620TQ-6 | Special Mode Registers Two color registers Burst Read | Siemens Semiconductor |

| HYB39S13620TQ-7 | Special Mode Registers Two color registers Burst Read | Siemens Semiconductor |

| HYB39S13620TQ-8 | Special Mode Registers Two color registers Burst Read | Siemens Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |