|

|

PDF VSC8116 Data sheet ( Hoja de datos )

| Número de pieza | VSC8116 | |

| Descripción | ATM/SONET/SDH 622/155Mb/s Transceiver Mux/Demux | |

| Fabricantes | Vitesse Semiconductor Corporation | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de VSC8116 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

Data Sheet

VSC8116

VITESSE

SEMICONDUCTOR CORPORATION

www.DataSheet4U.com

ATM/SONET/SDH 622/155Mb/s Transceiver

Mux/Demux with Integrated Clock Generation

Features

• Operates at Either STS-3/STM-1 (155.52 Mb/s) or

STS-12/STM-4 (622.08 Mb/s) Data Rates

• Compatible with Industry ATM UNI Devices

• On Chip Clock Generation of the 155.52 Mhz

or 622.08 Mhz High Speed Clock

• Dual 8 Bit Parallel TTL Interface

• Loss of Signal (LOS) Control

• Provides Equipment, Facilities and Split Loop-

back Modes as well as Loop Timing Mode

• Meets Bellcore, ITU and ANSI Specifications for

Jitter Performance

• Single 3.3V Supply Voltage

• Low Power - 1.2 Watts Maximum

• SONET/SDH Frame Detection and Recovery

• 64 PQFP Package

General Description

The VSC8116 is an ATM/SONET/SDH compatible transceiver integrating an on-chip clock multiplication

unit (PLL) for the high speed clock and 8 bit serial-to-parallel and parallel-to-serial data conversion. The high

speed clock generated by the on-chip PLL is selectable for 155.52 or 622.08 MHz operation. The demultiplexer

contains SONET/SDH frame detection and recovery. In addition, the device provides both facility and equip-

ment loopback modes and loop timing modes. The part is packaged in a 64 PQFP with an integrated heat

spreader for optimum thermal performance and reduced cost. The VSC8116 provides an integrated solution for

ATM physical layers and SONET/SDH systems applications.

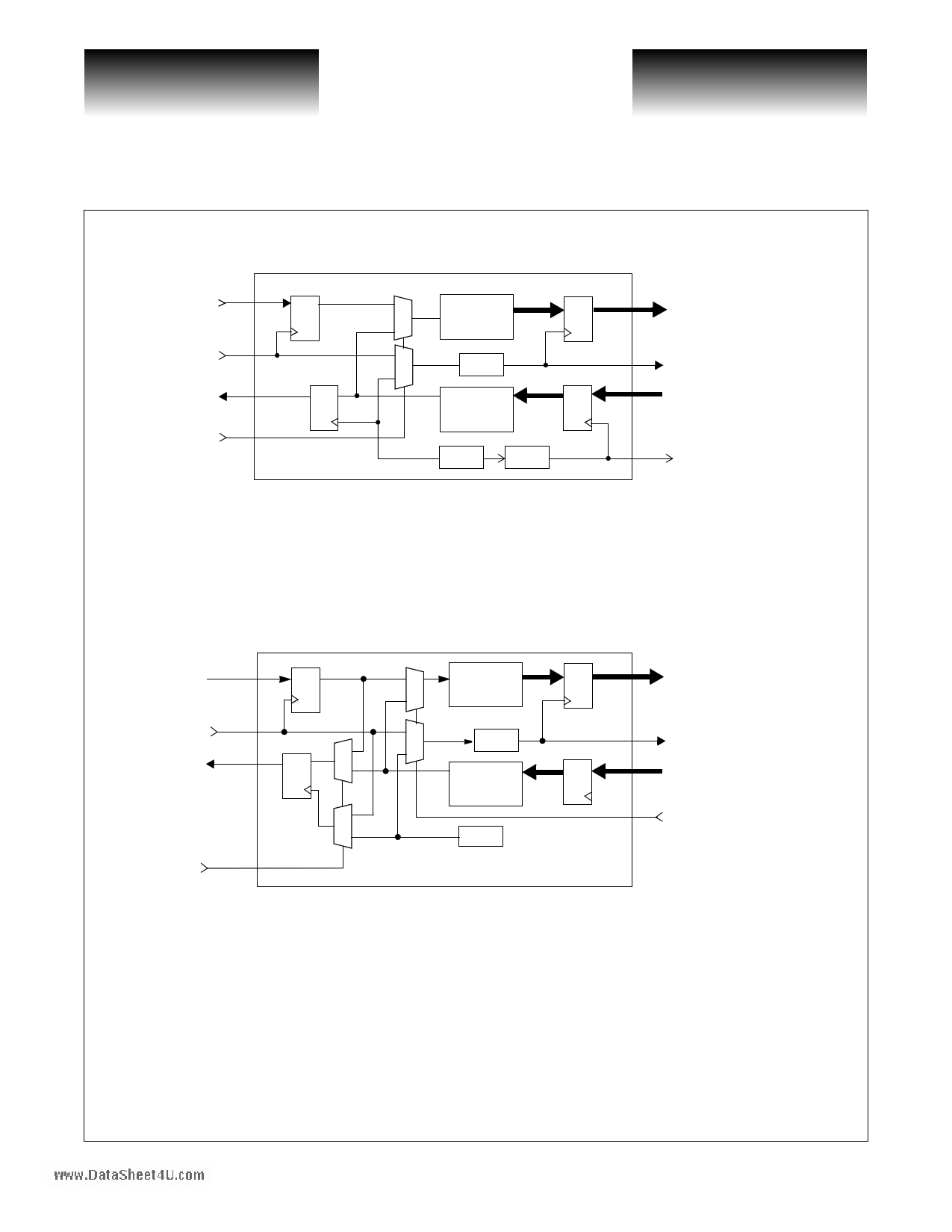

VSC8116 Block Diagram

EQULOOP

LOSTTL

RXDATAIN+/-

RXCLKIN+/-

LOS

DQ

0

1

FRAMER

OOF

FP

0

1

1:8

DEMUX

8

DQ

RXOUT[7:0]

0

Divide-by-8

1

RXLSCKOUT

TXDATAOUT+/-

FACLOOP

QD

1

0

1

0

10

8:1

MUX

8

QD

Divide-by-8

TXIN[7:0]

TXLSCKOUT

CMU

LOOPTIM0

REFCLK

G52220-0, Rev 4.1

1/8/00

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

Page 1

1 page

Data Sheet

VSC8116

VITESSE

SEMICONDUCTOR CORPORATION

www.DataSheet4U.com

ATM/SONET/SDH 622/155Mb/s Transceiver

Mux/Demux with Integrated Clock Generation

Figure 4: Equipment Loopback Data Path

RXDATAIN

RXCLKIN

TXDATAOUT

EQULOOP

DQ

QD

0 1:8

Serial to

1 Parallel

0

÷8

1

8:1

Parallel to

Serial

DQ

QD

PLL ÷ 8

RXOUT[7:0]

RXLSCKOUT

TXIN[7:0]

TXLSCKOUT

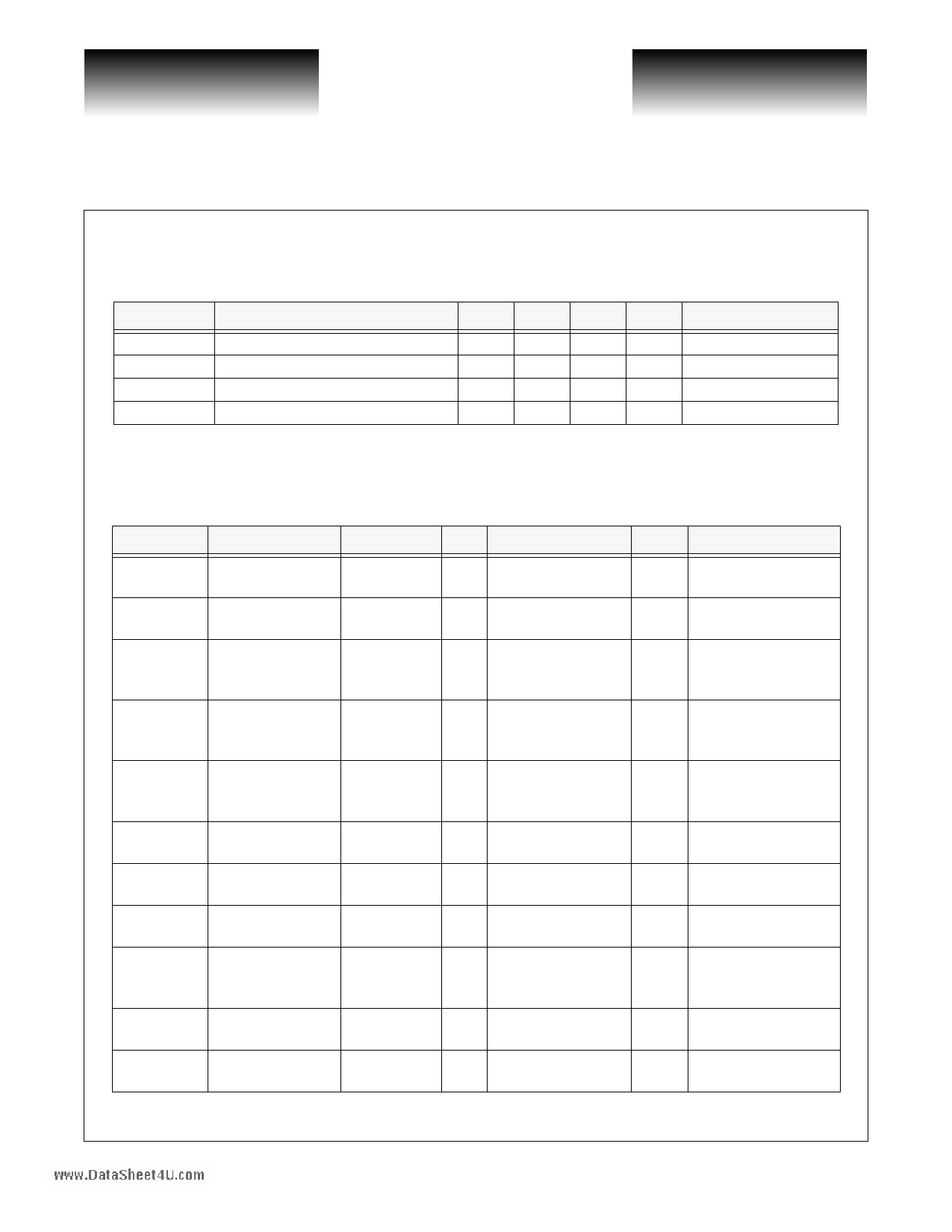

Split Loopback

Equipment and facility loopback modes can be enabled simultaneously. See descriptions for equipment and

facility loop modes above. The only change is, since they are both active, RXDATAIN will not be deserialized

and presented to RXOUT[0:7], and TXIN[0:7] will not be serialized and present to TXDATAOUT.

Figure 5: Split Loopback Datapath

RXDATAIN

RXCLKIN

TXDATAOUT

FACLOOP

DQ

QD

1

0

1

0

0

1:8

Serial to

Parallel

1

0

÷8

1

8:1

Parallel to

Serial

PLL

DQ

QD

RXOUT[7:0]

RXLSCKOUT

TXIN[7:0]

EQULOOP

Loop Timing

LOOPTIM0 mode bypasses the CMU when the LOOPTIM0 input is asserted high. In this mode the CMU

is bypassed by using the receive clock (RXCLKIN), and the entire part is synchronously clocked from a single

external source.

G52220-0, Rev 4.1

1/8/00

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

Page 5

5 Page

Data Sheet

VSC8116

VITESSE

SEMICONDUCTOR CORPORATION

www.DataSheet4U.com

ATM/SONET/SDH 622/155Mb/s Transceiver

Mux/Demux with Integrated Clock Generation

AC Characteristics

Table 10: PECL and TTL Outputs

Parameters

TR,TTL

TF,TTL

TR,PECL

TF,PECL

Description

TTL Output Rise Time

TTL Output Fall Time

PECL Output Rise Time

PECL Output Fall Time

Min Typ Max Units

Conditions

— 2 — ns 10-90%

— 1.5 — ns 10-90%

— 350 —

— 350 —

ps 20-80%

ps 20-80%

DC Characteristics

Table 11: PECL and TTL Inputs and Outputs

Parameters

VOH

VOL

VOCM

∆VOUT75

∆VOUT50

VIH

VIL

∆VIN

VICM

VOH

VOL

Description

Output HIGH

voltage (PECL)

Output LOW

voltage (PECL)

O/P Common

Mode Range

(PECL)

Differential

Output Voltage

(PECL)

Differential

Output Voltage

(PECL)

Input HIGH

voltage (PECL)

Input LOW

voltage (PECL)

Differential Input

Voltage (PECL)

I/P Common

Mode Range

(PECL)

Output HIGH

voltage (TTL)

Output LOW

voltage (TTL)

Min Typ

Max

Units

Conditions

— — VDDP – 0.9V V —

0.7 —

—

V—

1.1 — VDDP – 1.3V V —

600 —

1300

mV 75Ω to VDDP – 2.0 V

600 —

1300

mV 50Ω to VDDP – 2.0 V

VDDP – 0.9V —

0—

400 —

VDDP – 0.3V

VDDP – 1.72V

1600

V For single ended

V For single ended

mV —

1.5 – ∆VIN/2 — VDDP – 1.0 – ∆VIN/2 V —

2.4 —

——

—

0.5

V IOH = -1.0 mA

V IOL = +1.0 mA

G52220-0, Rev 4.1

1/8/00

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

Page 11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet VSC8116.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| VSC8111 | ATM/SONET/SDH 155/622 Mb/s Transceiver Mux/Demux | Vitesse Semiconductor |

| VSC8115 | STS-12/STS-3 Multi Rate Clock and Data Recovery Unit | Vitesse Semiconductor |

| VSC8116 | ATM/SONET/SDH 622/155Mb/s Transceiver Mux/Demux | Vitesse Semiconductor Corporation |

| VSC8117 | ATM/SONET/SDH 622/155 Mb/s Transceiver Mux/Demux | Vitesse Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |