|

|

PDF LG1600FXH1555 Data sheet ( Hoja de datos )

| Número de pieza | LG1600FXH1555 | |

| Descripción | LG1600FXH Clock and Data Regenerator | |

| Fabricantes | Agere Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LG1600FXH1555 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

Data Sheet

August 1999

LG1600FXH Clock and Data Regenerator

Figure 1. LG1600FXH Open View

Features

s Integrated clock recovery and data retiming

s Surface-mount package

s Single ECL supply

s Robust FPLL design

s Operation up to BER = 1e–3

s SONET/SDH compatible loss of signal alarm

s High effective Q allows long run lengths

s Jitter tolerance exceeding ITU-T/Bellcore

s Low clock jitter generation: typical <0.005 UI

s Standard and custom data rates

0.50 Gbits/s—5.5 Gbits/s

s Complementary 50 Ω I/Os

Applications

s SONET/SDH receiver terminals and regenerators

OC-12 through OC-96/STM-4 through STM-32

s SONET/SDH test equipment

s Proprietary bit rate systems

s Digital video transmission

s Clock doublers and quadruplers

1 page

Data Sheet

August 1999

LG1600FXH Clock and Data Regenerator

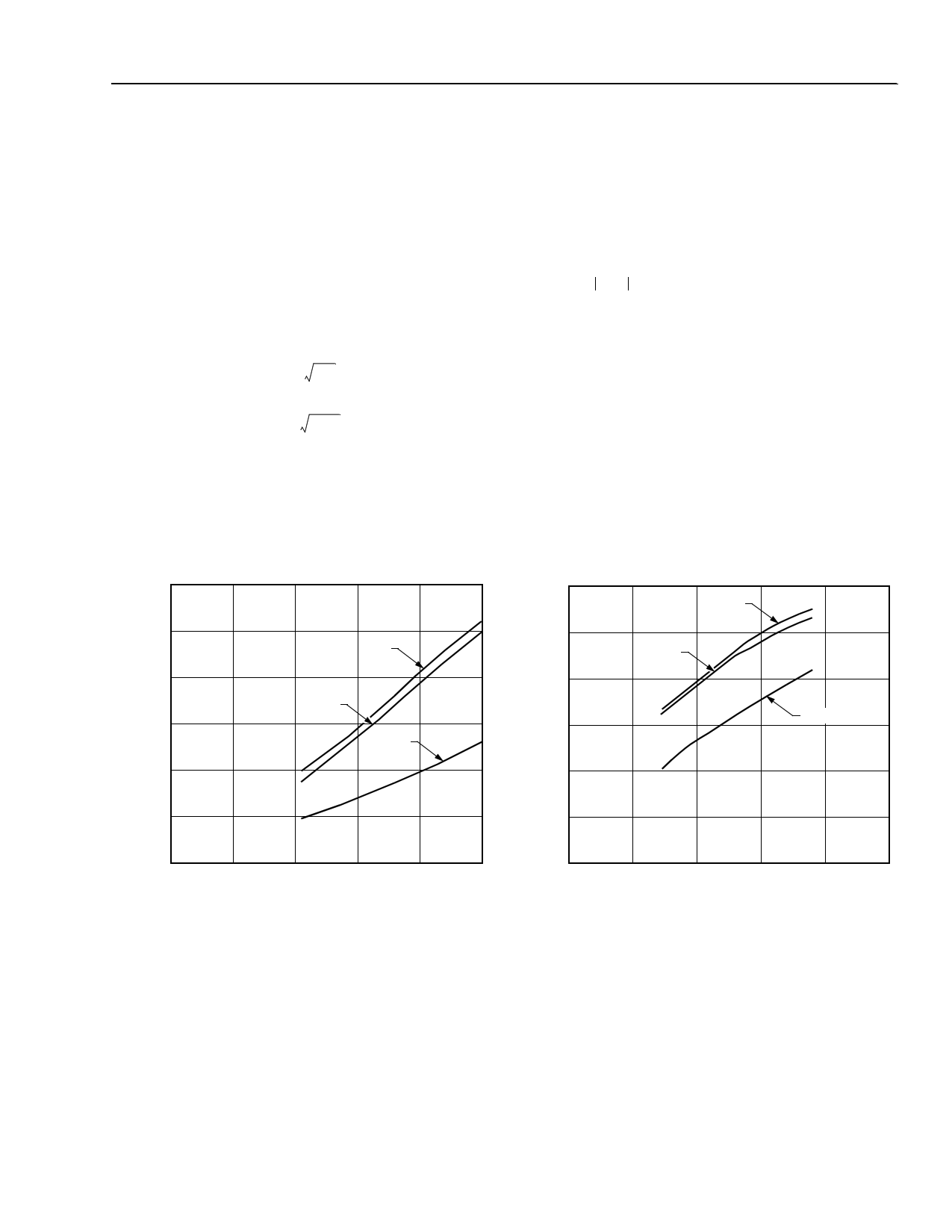

Theory of Operation (continued)

A more useful expression of the PLL characteristics is

the following*:

H(s)

=

ωb1 + s--1--τ-

-------------------------------------

s + ωb1 + s--1--τ-

The jitter transfer is now directly expressed in the phys-

ical loop gain pole product, ωb, and the loop filter time

constant, τ. Damping ratio, ς, and natural frequency, ωn,

simply relate to these two parameters as follows:

ς = 0.5 ωbτ

and

ωn = ωn ⁄ τ

For moderate damping ς > 2.5 (ωbτ < 0.1), the –3 dB

bandwidth of the PLL can be approximated by the loop

gain pole product:

JBW ≈ ωb = KdRxKo

while the jitter peaking can be expressed in terms of

the product of PLL bandwidth and loop filter time con-

stant:

H(s) max ≈ 1 + ω----1-b---τ-

=

1

+

------------1-------------

R x2 C Kd K o

As the last two expressions make clear, the PLL band-

width is controlled by the value of the external resistor

(see Figure 8), while the peaking depends both on the

resistor value (quadratically) and total loop filter capac-

itance.

* Wolaver, D.H., Phase-Locked Loop Circuit Design, Prentice Hall,

1991.

1.2

1.0

0.8

0.6

0.4

0.2

0.0

0

10 °C

25 °C

70 °C

50 100 150 200 250

Rx (Ω)

3.6

3.0

2.4

1.8

1.2

0.6

0.0

0

10 °C

25 °C

70 °C

50 100 150 200 250

Rx (Ω)

A. LG1600FXH0622 (Cx = 0.15 µF)

B. LG1600FXH2488 (Cx = 0)

12-3231(F)r.4—12-3232(F)r.4

Figure 8. Jitter Bandwidth vs. External Resistor Value

Lucent Technologies Inc.

5

5 Page

Data Sheet

August 1999

LG1600FXH Clock and Data Regenerator

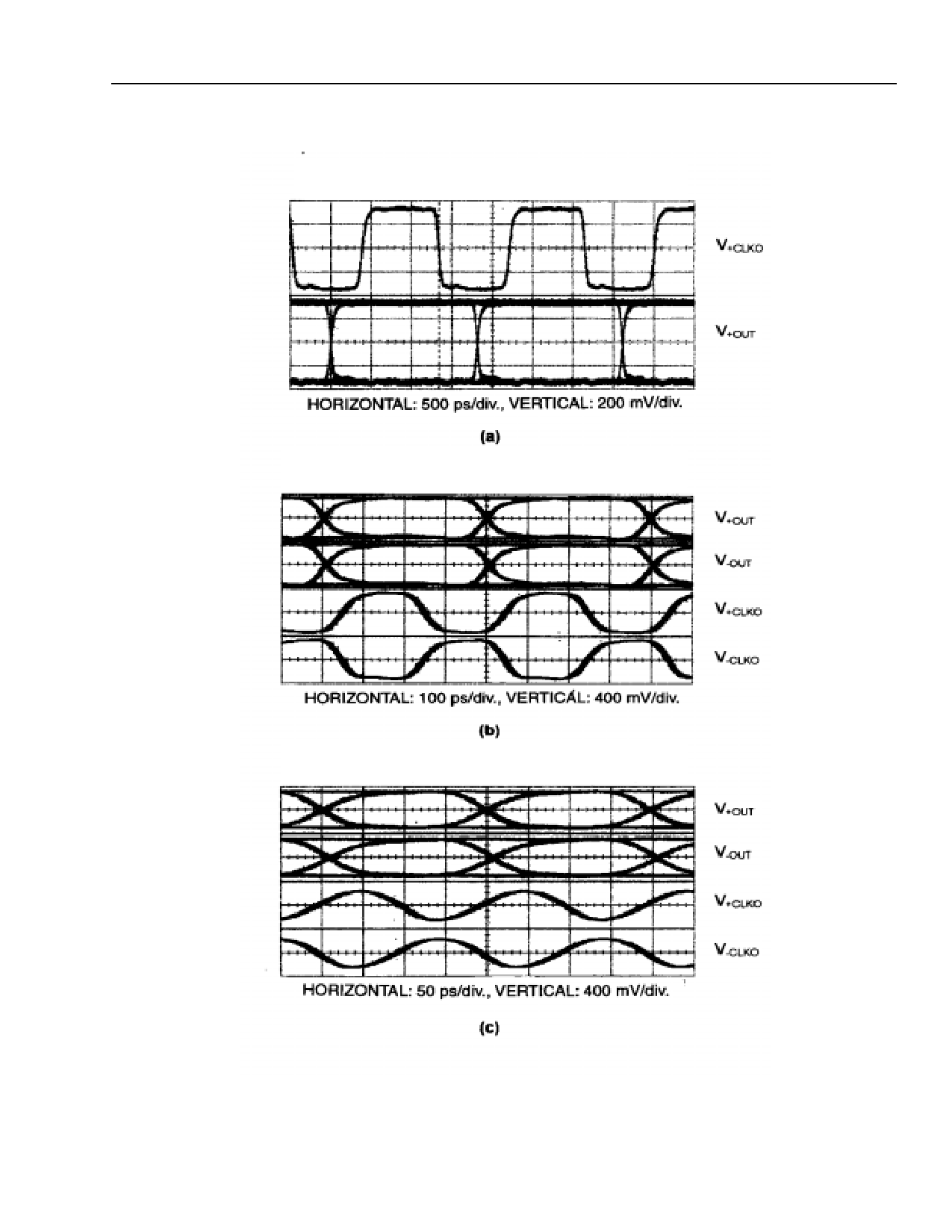

Typical Performance Characteristics

LG1600FXH0553

LG1600FXH2488

LG1600FXH4977

Lucent Technologies Inc.

Figure 11. LG1600FXH Typical Eye Patterns

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet LG1600FXH1555.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LG1600FXH1555 | LG1600FXH Clock and Data Regenerator | Agere Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |