|

|

PDF ADG1636 Data sheet ( Hoja de datos )

| Número de pieza | ADG1636 | |

| Descripción | Dual SPDT Switch | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADG1636 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

1 Ω Typical On Resistance, ±5 V, +12 V,

+5 V, and +3.3 V Dual SPDT Switches

ADG1636

FEATURES

1 Ω typical on resistance

0.2 Ω on resistance flatness

±3.3 V to ±8 V dual supply operation

3.3 V to 16 V single supply operation

No VL supply required

3 V logic-compatible inputs

Rail-to-rail operation

Continuous current per channel

LFCSP package: 385 mA

TSSOP package: 238 mA

16-lead TSSOP and 16-lead, 4 mm × 4 mm LFCSP

APPLICATIONS

Communication systems

Medical systems

Audio signal routing

Video signal routing

Automatic test equipment

Data acquisition systems

Battery-powered systems

Sample-and-hold systems

Relay replacements

GENERAL DESCRIPTION

The ADG1636 is a monolithic CMOS device containing two

independently selectable single-pole/double-throw (SPDT)

switches. An EN input is used to enable or disable the device.

When disabled, all channels are switched off. Each switch

conducts equally well in both directions when on and has

an input signal range that extends to the supplies. In the off

condition, signal levels up to the supplies are blocked. Both

switches exhibit break-before-make switching action for use

in multiplexer applications.

The ultralow on resistance of these switches make them ideal

solutions for data acquisition and gain switching applications where

low on resistance and distortion is critical. The on resistance profile

is very flat over the full analog input range, ensuring excellent

linearity and low distortion when switching audio signals.

The CMOS construction ensures ultralow power dissipation,

making the parts ideally suited for portable and battery-

powered instruments.

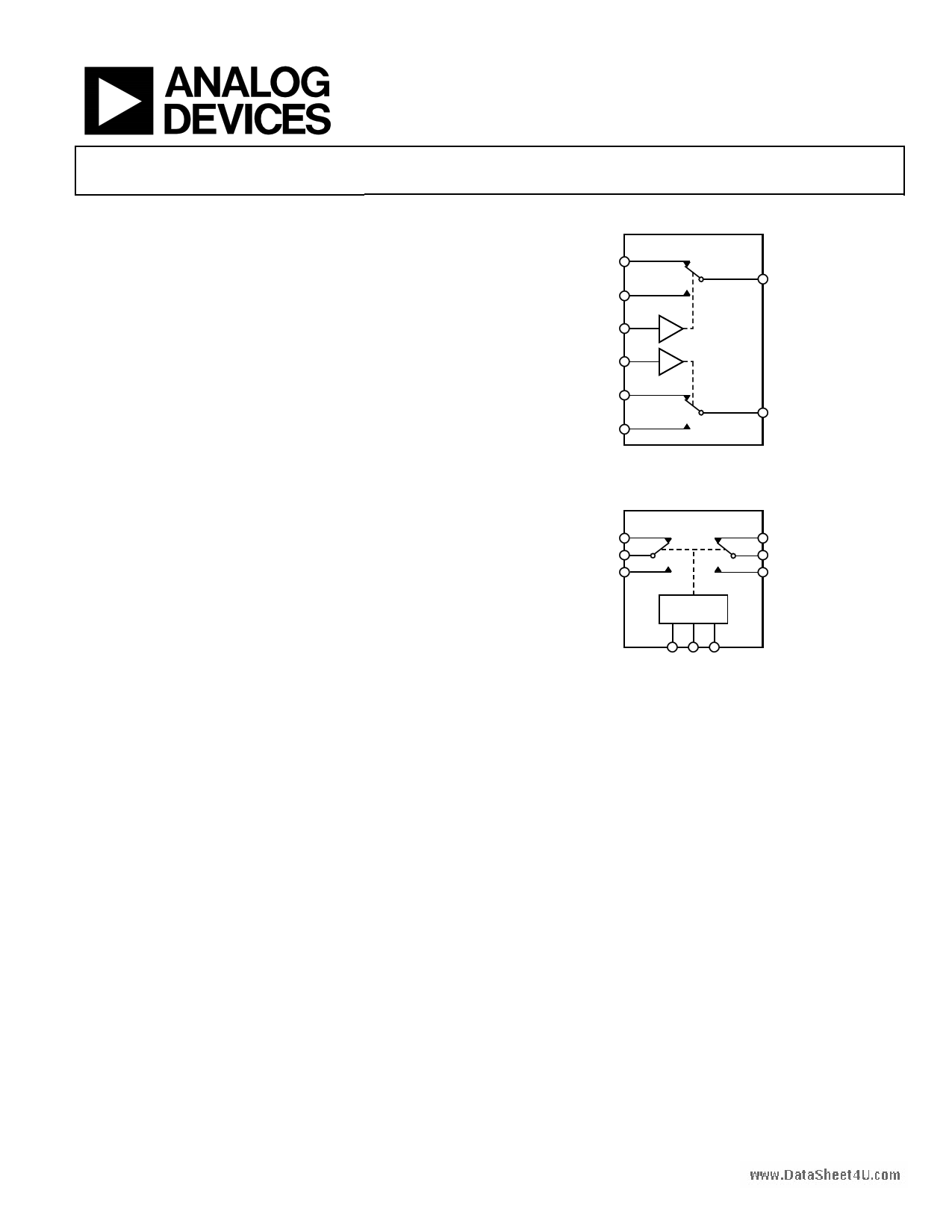

FUNCTIONAL BLOCK DIAGRAMS

ADG1636

S1A

D1

S1B

IN1

IN2

S2A

D2

S2B

NOTES

1. SWITCHES SHOWN FOR A LOGIC 1 INPUT.

Figure 1. 16-Lead TSSOP

ADG1636

S1A

D1

S1B

S2A

D2

S2B

LOGIC

IN1 IN2 EN

NOTES

1. SWITCHES SHOWN FOR A 1 INPUT LOGIC.

Figure 2. 16-Lead LFCSP

PRODUCT HIGHLIGHTS

1. 1.6 Ω maximum on resistance over temperature.

2. Minimum distortion: THD + N = 0.007%.

3. 3 V logic-compatible digital inputs: VINH = 2.0 V, VINL = 0.8 V.

4. No VL logic power supply required.

5. Ultralow power dissipation: <16 nW.

6. 16-lead TSSOP and 16-lead 4 mm × 4 mm LFCSP.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2009 Analog Devices, Inc. All rights reserved.

1 page

www.DataSheet4U.com

ADG1636

5 V SINGLE SUPPLY

VDD = 5 V ± 10%, VSS = 0 V, GND = 0 V, unless otherwise noted.

Table 3.

Parameter

ANALOG SWITCH

Analog Signal Range

On Resistance (RON)

On Resistance Match Between Channels (∆RON)

On Resistance Flatness (RFLAT(ON))

LEAKAGE CURRENTS

Source Off Leakage, IS (Off )

Drain Off Leakage, ID (Off )

Channel On Leakage, ID, IS (On)

DIGITAL INPUTS

Input High Voltage, VINH

Input Low Voltage, VINL

Input Current, IINL or IINH

Digital Input Capacitance, CIN

DYNAMIC CHARACTERISTICS1

Transition Time, tTRANSITION

tON (EN)

tOFF (EN)

Break-Before-Make Time Delay, tD

Charge Injection

Off Isolation

Channel-to-Channel Crosstalk

Total Harmonic Distortion + Noise

−3 dB Bandwidth

CS (Off )

CD (Off )

CD, CS (On)

POWER REQUIREMENTS

IDD

VDD

25°C

1.7

2.15

0.05

0.09

0.4

0.53

±0.05

±0.25

±0.05

±0.25

±0.1

±0.6

0.001

5

160

271

132

172

210

268

30

70

70

90

0.09

26

76

145

237

0.001

−40°C to

+85°C

2.4

0.12

0.55

±1

±2

±2

319

185

313

1.0

−40°C to

125°C

0 V to VDD

2.7

0.15

0.6

±4

±10

±12

2.0

0.8

±0.1

355

201

345

17

1.0

3.3/16

Unit

V

Ω typ

Ω max

Ω typ

Ω max

Ω typ

Ω max

nA typ

nA max

nA typ

nA max

nA typ

nA max

V min

V max

μA typ

μA max

pF typ

ns typ

ns max

ns typ

ns max

ns typ

ns max

ns typ

ns min

pC typ

dB typ

dB typ

% typ

MHz typ

pF typ

pF typ

pF typ

μA typ

μA max

V min/max

Test Conditions/Comments

VS = 0 V to 4.5 V, IS = −10 mA; see Figure 23

VDD = 4.5 V, VSS = 0 V

VS = 0 V to 4.5 V, IS = −10 mA

VS = 0 V to 4.5 V, IS = −10 mA

VDD = 5.5 V, VSS = 0 V

VS = 1 V/4.5 V, VD = 4.5 V/1 V; see Figure 24

VS = 1 V/4.5 V, VD = 4.5 V/1 V; see Figure 24

VS = VD = 1 V or 4.5 V; see Figure 25

VIN = VGND or VDD

RL = 300 Ω, CL = 35 pF

VS = 2.5 V; see Figure 30

RL = 300 Ω, CL = 35 pF

VS = 2.5 V; see Figure 30

RL = 300 Ω, CL = 35 pF

VS = 2.5 V; see Figure 30

RL = 300 Ω, CL = 35 pF

VS1 = VS2 = 2.5 V; see Figure 31

VS = 2.5 V, RS = 0 Ω, CL = 1 nF; see Figure 32

RL = 50 Ω, CL = 5 pF, f = 100 kHz;

see Figure 26

RL = 50 Ω, CL = 5 pF, f = 100 kHz;

see Figure 28

RL = 110 Ω, f = 20 Hz to 20 kHz, VS = 3.5 V p-p;

see Figure 29

RL = 50 Ω, CL = 5 pF; see Figure 27

VS = 2.5 V, f = 1 MHz

VS = 2.5 V, f = 1 MHz

VS = 2.5 V, f = 1 MHz

VDD = 5.5 V

Digital inputs = 0 V or VDD

1 Guaranteed by design, not subject to production test.

Rev. 0 | Page 5 of 16

5 Page

www.DataSheet4U.com

15

ID, IS (ON) +, +

10 ID (OFF) –, +

5

IS (OFF) +, –

0

IS (OFF) –, +

–5 ID, IS (ON) –, –

ID (OFF) +, –

–10

–15 0

20 40 60 80 100 120

TEMPERATURE (°C)

Figure 11. Leakage Currents as a Function of Temperature, ±5 V Dual Supply

20

15

ID, IS (ON) +, +

10

ID (OFF) –, +

5 IS (OFF) +, –

0

–5 ID, IS (ON) –, –

IS (OFF) –, +

–10 ID (OFF) +, –

–15 0

20 40 60 80 100 120

TEMPERATURE (°C)

Figure 12. Leakage Currents as a Function of Temperature,

12 V Single Supply

20

15

ID, IS (OFF) +, +

10

ID, IS (OFF) –, –

5 ID (OFF) –, +

0

IS (OFF) +, –

IS (OFF) –, +

ID (OFF) +, –

–5

0 20 40 60 80 100 120

TEMPERATURE (°C)

Figure 13. Leakage Currents as a Function of Temperature,

5 V Single Supply

ADG1636

18

16

14

12 ID, IS (OFF) +, +

10

8 ID, IS (OFF) –, –

6 ID (OFF) –, +

4

IS (OFF) +, –

2

0

–2 IS (OFF) –, +

ID (OFF) +, –

–4

0 20 40 60 80 100 120

TEMPERATURE (°C)

Figure 14. Leakage Currents as a Function of Temperature,

3.3 V Single Supply

600

500

IIDSSD

=

=

+12V

0V

400

IDD PER CHANNEL

TA = 25°C

300

200

100

0

–100

0

IIDSSD

=

=

+5V

–5V

IIDSSD

=

=

+5V

0V

IIDSSD

=

=

+3.3V

0V

2468

LOGIC (V)

10 12 14

Figure 15. IDD vs. Logic Level

300

250

VVDSSD

=

=

+5V

–5V

200

150

VVDSSD

=

=

+12V

0V

100

50

0

–6 –4 –2

VVDSSD

=

=

+5V

0V

VVDSSD

=

=

+3.3V

0V

0 2 4 6 8 10 12

VS (V)

Figure 16. Charge Injection vs. Source Voltage

14

Rev. 0 | Page 11 of 16

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet ADG1636.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADG1633 | (ADG1633 / ADG1634) +3.3 V Switches | Analog Devices |

| ADG1634 | (ADG1633 / ADG1634) +3.3 V Switches | Analog Devices |

| ADG1636 | Dual SPDT Switch | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |