|

|

PDF IC42S32200L Data sheet ( Hoja de datos )

| Número de pieza | IC42S32200L | |

| Descripción | 512K Words x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IC42S32200L (archivo pdf) en la parte inferior de esta página. Total 62 Páginas | ||

|

No Preview Available !

IC42S32200

IC42S32200L

Document Title

512K x 32 Bit x 4 Banks (64-MBIT) SDRAM

Revision History

www.datasheet4Ru.ecvomision No

0A

0B

0C

0D

History

Initial Draft

Obselete partial refresh function

Obselete 5ns speed grade

Change ICC3P from 3mA to 5mA

Revise typo

Revise p.20,p.22 data and p.28 typo

Draft Date

September 26,2002

September 05,2003

Remark

April 27,2004

February 04,2005

The attached datasheets are provided by ICSI. Integrated Circuit Solution Inc reserve the right to change the specifications and

products. ICSI will answer to your questions about device. If you have any questions, please contact the ICSI offices.

Integrated Circuit Solution Inc.

DR036-0D 02/04/2005

1

1 page

IC42S32200

IC42S32200L

PIN FUNCTION

NC -

No Connect:These pins should be left unconnected.

VDDQ Supply DQ Power:Provide isolated power to DQs for improved noise immunity.

VSSQ Supply DQ Ground:Provide isolated ground to DQs for improved noise immunity.

www.datasheet4u.com

VDD Supply Power Supply:+3.3V ± 0.3V

VSS Supply Ground

PIN CONFIGURATIONS

86-Pin TSOP 2

Pin Assignment (Top View)

VDD

DQ 0

VDDQ

DQ 1

DQ 2

VSSQ

DQ 3

DQ 4

VDDQ

DQ 5

DQ 6

VSSQ

DQ 7

NC

VDD

DQM 0

/WE

/CAS

/RAS

/CS

NC

BS0

BS1

A10/AP

A0

A1

A2

DQM 2

VDD

NC

D Q16

VSSQ

D Q17

D Q18

VDDQ

D Q19

D Q20

VSSQ

D Q21

D Q22

VDDQ

D Q23

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

86 VSS

8 5 DQ15

84 VSSQ

8 3 DQ14

8 2 DQ13

8 1 VDDQ

8 0 DQ12

7 9 DQ11

78 VSSQ

7 7 DQ10

7 6 DQ9

7 5 VDDQ

7 4 DQ8

7 3 NC

72 VSS

71 DQM1

7 0 NC

6 9 NC

6 8 CL K

6 7 CKE

66 A9

65 A8

64 A7

63 A6

62 A5

61 A4

60 A3

59 DQM3

58 VSS

5 7 NC

5 6 DQ31

5 5 VDDQ

5 4 DQ30

5 3 DQ29

52 VSSQ

5 1 DQ28

5 0 DQ27

4 9 VDDQ

4 8 DQ26

4 7 DQ25

46 VSSQ

4 5 DQ24

44 VSS

90-Ball FBGA

1 23 45 6 78 9

A DQ26 DQ24 Vss

B DQ28 VDDQ VSSQ

C VSSQ DQ27 DQ25

D VSSQ DQ29 DQ30

E VDDQ DQ31 NC

F VSS DQM3 A3

G A4 A5 A6

H A7 A8 NC

J

CLK CKE

A9

K DQM1 NC NC

L VDDQ DQ8

VSS

M VSSQ DQ10 DQ9

N VSSQ DQ12 DQ14

P DQ11 VDDQ VSSQ

R DQ13 DQ15 VSS

(Top View)

VDD DQ23 DQ21

VDDQ VSSQ DQ19

DQ22 DQ20 VDDQ

DQ17 DQ18 VDDQ

NC DQ16 VSSQ

A2 DQM2 VDD

A10 A0

A1

NC BA1 NC

BA0 CS RAS

CAS WE DQM0

VDD DQ7 VSSQ

DQ6 DQ5 VDDQ

DQ1 DQ3 VDDQ

VDDQ VSSQ DQ4

VDD DQ0 DQ2

Integrated Circuit Solution Inc.

DR036-0D 02/04/2005

5

5 Page

IC42S32200

IC42S32200L

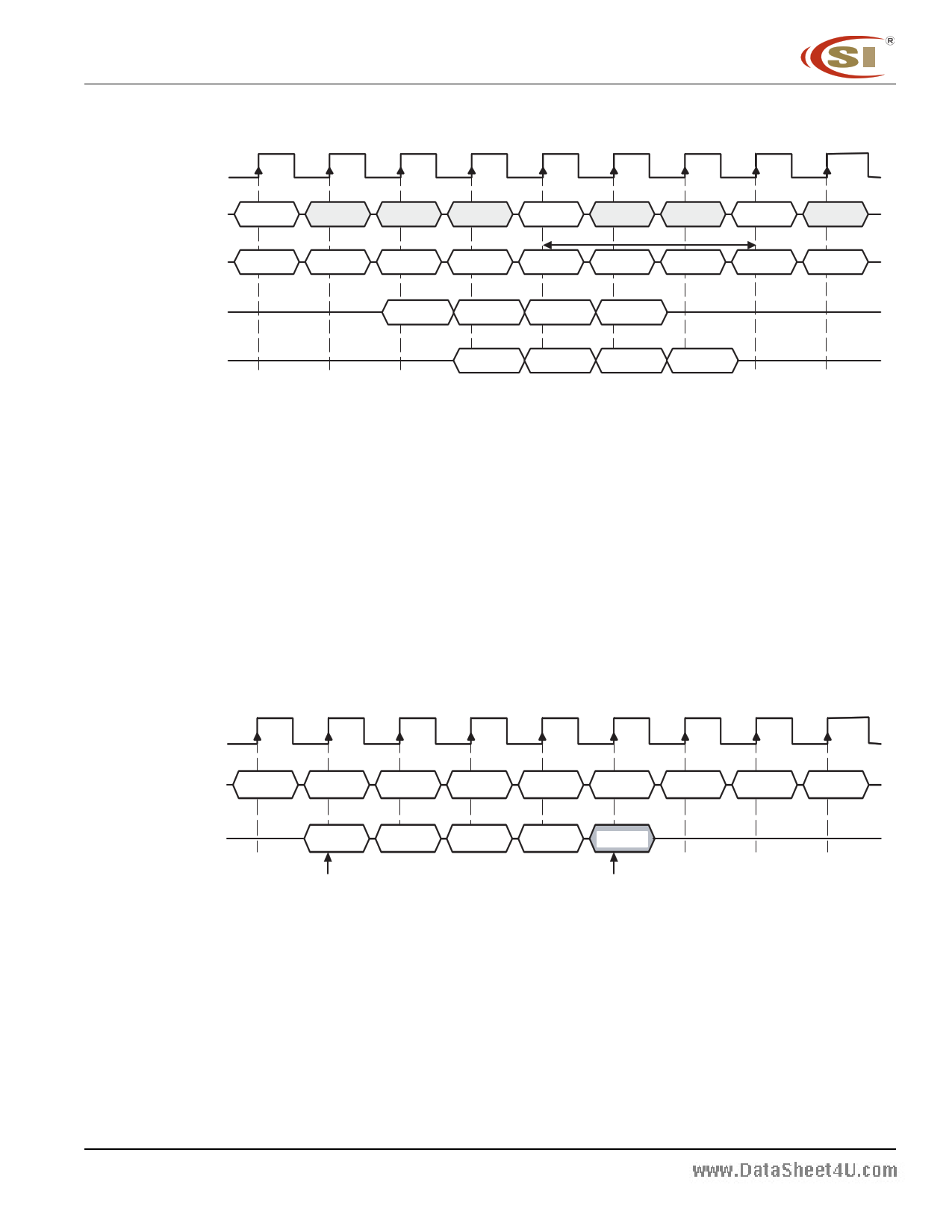

CLK

ADDRESS

www.datasheet4u.com

COMMAND

T0 T1 T2 T3 T4 T5 T6 T7 T8

Bank,

Col A

READ A

NOP

NOP

Bank(s)

NOP

Precharge

tRP

NOP

NOP

Bank,

Row

Activate

NOP

CAS# latency=2

tCK2, DQ s

CAS# latency=3

tCK3, DQ s

DOUT A0

DOUT A1 DOUT A2

DOUT A3

DOUT A0

DOUT A1 DOUT A2

DOUT A3

Read to Precharge (CAS#Latency =2,3)

5 Write command

(RAS#=”H”,CAS#=”L”,WE#=”L”,BS =Bank,A10 =”L”,A0-A7 =Column Address)

The Write command is used to write a burst of data on consecutive clock cycles from an active row in an active

bank.The bank must be active for at least tRCD(min.)before the Write command is issued.During write bursts,

the first valid data-in element will be registered coincident with the Write command.Subsequent data elements

will be registered on each successive positive clock edge (refer to the following figure).The DQs remain with high-

impedance at the end of the burst unless another command is initiated.The burst length and burst sequence are

determined by the mode register,which is already programmed.A full-page burst will continue until terminated (at

the end of the page it will wrap to column 0 and continue).

CLK

COMMAND

T0 T1 T2 T3 T4 T5 T6 T7 T8

NOP WRITEA

NOP

NOP

NOP

NOP

NOP

NOP

NOP

DQ0 - DQ3

DIN A 0

DIN A1

DIN A 2

DIN A 3

don’t care

The first data element and the write

are registered on the same clock edge.

Extra data is masked.

Burst Write Operation (Burst Length =4,CAS#Latency =2,3)

A write burst without the AutoPrecharge function may be interrupted by a subsequent Write, BankPrecharge/

PrechargeAll,or Read command before the end of the burst length.An interrupt coming from Write command can

occur on any clock cycle following the previous Write command (refer to the following figure).

Integrated Circuit Solution Inc.

DR036-0D 02/04/2005

11

11 Page | ||

| Páginas | Total 62 Páginas | |

| PDF Descargar | [ Datasheet IC42S32200L.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IC42S32200 | 512K Words x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM | Integrated Circuit Systems |

| IC42S32200L | 512K Words x 32 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |