|

|

PDF MAX3674 Data sheet ( Hoja de datos )

| Número de pieza | MAX3674 | |

| Descripción | Network Clock Synthesizer | |

| Fabricantes | Maxim Integrated Products | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX3674 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

19-2483; Rev 0; 12/07

High-Performance, Dual-Output, Network Clock

Synthesizer

www.datasheet4u.com

General Description

The MAX3674 is a high-performance network clock

synthesizer IC for networking, computing, and telecom

applications. It integrates a crystal oscillator, a low-

noise phase-locked loop (PLL), programmable dividers,

and high-frequency LVPECL output buffers. The PLL

generates a high-frequency clock based on a low-fre-

quency reference clock provided by the on-chip crystal

oscillator or an external LVCMOS clock. The MAX3674

has excellent period jitter, cycle-to-cycle jitter, and sup-

ply noise rejection performance. With output frequen-

cies programmable from 21.25MHz to 1360MHz and

support of two differential PECL output signals, the

device provides a versatile solution for the most

demanding clock applications.

Programming is accomplished through a 2-wire I2C bus

or parallel interface that can change the output fre-

quency on demand for frequency margining. Both

LVPECL outputs have synchronous stop functionality,

and the PLL has a LOCK indicator output. The

MAX3674 operates from a +3.3V supply and typically

consumes 396mW. The device is packaged in a 48-pin

LQFP, and the operating temperature range is from

-40°C to +85°C.

Applications

Ethernet Network ASIC Clock Generation

Storage Area Network ASIC Clocking

Optical Network ASIC Clocking

Programmable Clock Source for Server, Comput-

ing, or Communication Systems

Frequency Margining

16MHz

SERIAL I2C

INTERFACE

PARALLEL

INTERFACE

PLL DIVIDER

CONTROLS

+3.3V +3.3V +3.3V

REF_SEL VCC VCC_PLL

REF_CLK

QA

XTAL1

QA

QB

XTAL2

SDA

SCL

M[9:0]

NA[2:0]

NB

P

QB

MAX3674

CLK_STOPA

CLK_STOPB

BYPASS

PLOAD MR GND LOCK

Features

♦ 21.25MHz to 1360MHz Programmable PLL Synthe-

sized Output Clocks

♦ Two Differential LVPECL-Compatible Outputs

♦ Cycle-to-Cycle Jitter 1.6ps RMS and Period Jitter

0.9ps RMS at 500MHz

♦ On-Chip Crystal Oscillator or Selectable

LVCMOS-Compatible Reference Clock Input

♦ Excellent Power-Supply Noise Rejection

♦ Parallel or 2-Wire I2C Programming Interface

♦ Lock Indicator Output

♦ +3.3V Power Supply

♦ Power Consumption: 396mW at 3.3V

♦ 48-Pin LQFP Pb-Free Package

♦ -40°C to +85°C Temperature Range

Ordering Information

PART

TEMP RANGE

MAX3674ECM+ -40°C to +85°C

+Denotes a lead-free package.

PIN-PACKAGE

48 LQFP

Pin Configuration appears at end of data sheet.

LVPECL

OUTPUTS

Z = 50Ω

Typical Application Circuit

+3.3V

130Ω

NETWORK

ASIC

+3.3V

82Ω

________________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

1 page

High-Performance, Dual-Output, Network Clock

Synthesizer

www.datasheet4u.com

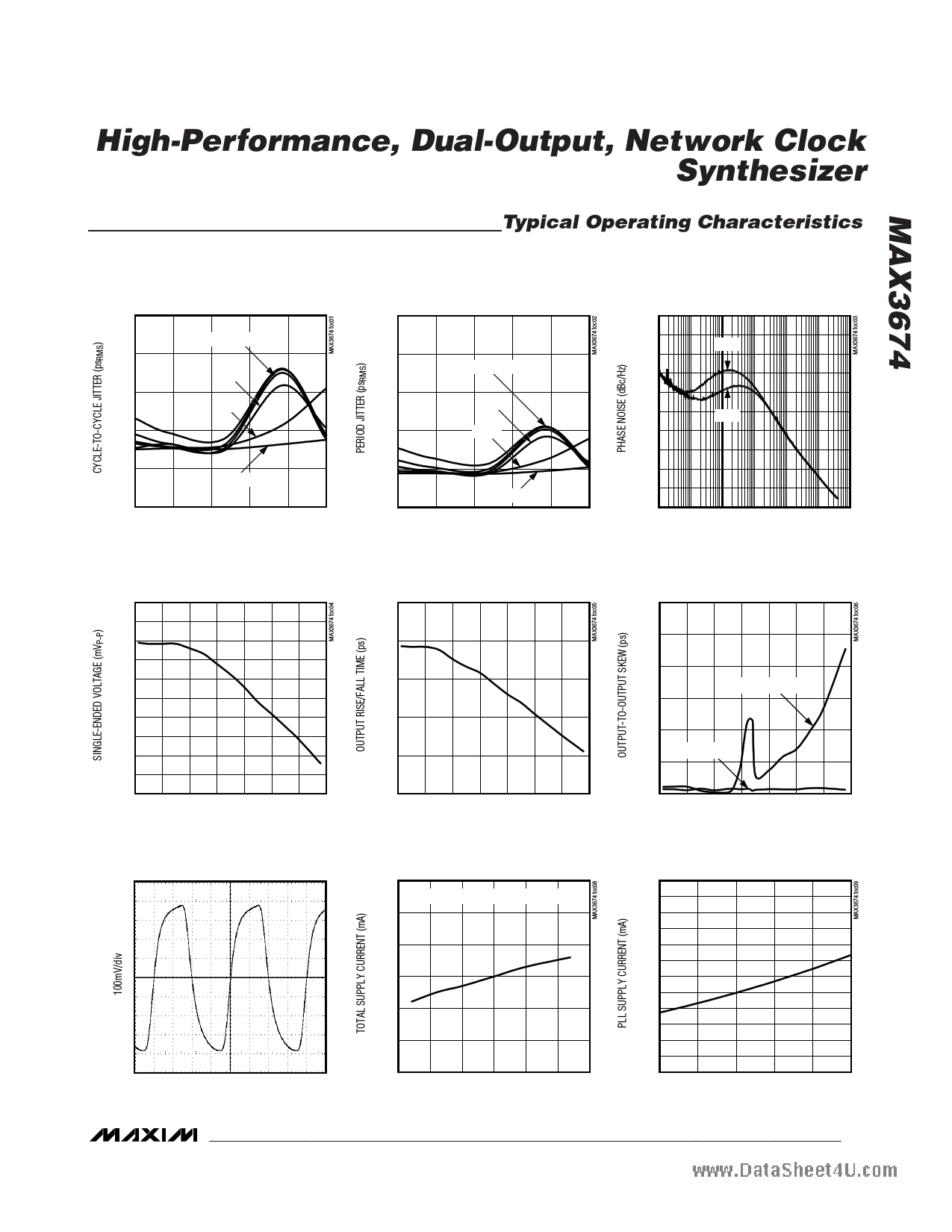

Typical Operating Characteristics

(VCC = VCC_PLL = +3.3V, TA = +25°C, fQA = fQB = 500MHz (P = 4, NA = 4, NB = 1, M = 500), REF_SEL= high (crystal oscillator),

fXTAL = 16MHz, unless otherwise noted.)

CYCLE-TO-CYCLE JITTER

vs. VCO FREQUENCY

5

NA = 16, 32, 64

4

NA = 8

3

NA = 4

2

1

NA = 2

0

1360

1632 1904 2176 2448

VCO FREQUENCY (MHz)

2720

PERIOD JITTER vs. VCO FREQUENCY

5

4

NA = 16, 32, 64

3

NA = 8

2 NA = 4

1

0

1360

NA = 2

1632 1904 2176 2448

VCO FREQUENCY (MHz)

2720

-50

-60

-70

-80

-90

-100

-110

-120

-130

-140

-150

100

PHASE NOISE

P=4

P=2

1k 10k 100k 1M 10M 100M

OFFSET FREQUENCY (Hz)

OUTPUT PEAK-TO PEAK VOLTAGE

vs. OUTPUT FREQUENCY

900

850

800

750

700

650

600

550

500

450

400

0

200 400 600 800 1000 1200 1400

OUTPUT FREQUENCY (MHz)

Qx CLOCK OUTPUT

(SINGLE-ENDED)

MAX3674 toc07

500ps/div

OUTPUT RISE/FALL TIME

vs. OUTPUT FREQUENCY

350

300

250

200

150

100

0

200 400 600 800 1000 1200 1400

OUTPUT FREQUENCY (MHz)

TOTAL SUPPLY CURRENT

vs. TEMPERATURE

150

INCLUDES PECL OUTPUT CURRENTS

140

130

120

110

100

90

-50 -25

0

25 50 75 100

TEMPERATURE (°C)

OUTPUT-TO-OUTPUT SKEW

vs. OUTPUT FREQUENCY

300

250

200

NB = 2, (fQA = 2 x fQB)

150

100

NB = 1, (fQA = fQB)

50

0

0 200 400 600 800 1000 1200 1400

QA OUTPUT FREQUENCY (MHz)

12

11

10

9

8

7

6

5

4

3

2

1

0

1360

PLL SUPPLY CURRENT

vs. VCO FREQUENCY

1632 1904 2176 2448

VCO FREQUENCY (MHz)

2720

_______________________________________________________________________________________ 5

5 Page

High-Performance, Dual-Output, Network Clock

Synthesizer

www.datasheet4u.com

The MAX3674

acts

as

a

I2C Characteristics

slave device on the I2C bus

supporting fast-mode data transfer (up to 400kbps). Its

clock pin, SCL, is an input only. It does not support

clock stretching. Table 3 shows the I2C slave address.

Table 3. I2C Slave Address

BIT

7

(MSB)

6

5

4

3

2

1

0

(LSB)

VALUE 1 0 1 1 0 ADR1 ADR0 R/W

The slave address is composed of a 5-bit fixed address

and 2-bit variable address that is set by the input pins

ADR[1:0]. The variable address pins are used to avoid

address conflicts of multiple MAX3674 devices on the

same I2C bus.

The host controller uses bit 0 (LSB) of the MAX3674

slave address to select either read or write mode. “0”

indicates I2C “write” to the MAX3674 registers; “1” indi-

cates I2C “read” from the MAX3674 registers.

Applications Information

Programming the MAX3674

The MAX3674 PLL configurations can be controlled

either through the parallel interface or the serial I2C

interface. The parallel interface allows the user to

directly configure the PLL dividers through hardwired

pins without the overhead of a serial interface. At

device startup, the device always obtains an initial PLL

frequency configuration through the parallel interface.

The PLL configuration can be read through I2C in paral-

lel interface mode.

The serial interface is I2C compatible. It allows reading

and writing device settings through built-in registers. It

also allows a host controller to program the output

frequency of the synthesizer on the fly using the incre-

ment and decrement functions for frequency margining

applications.

An LVCMOS-compatible input (PLOAD) is used to

select the parallel interface or serial interface, as

described in the Function Table.

Output Frequency Configuration

The MAX3674 output frequency (fOUT) is a function of

the reference frequency (fREF) and the programmable

dividers (P, M, and NA,B) and is expressed as:

fOUT =

fREF

P

×

M

N A,B

The numbers P, M, NA, and NB are divider ratios

requiring configuration through parallel programming or

I2C serial interfaces using registers PLL_L and PLL_H.

P is the predivider to the input of the phase-locked loop

(PLL) and has a valid division ratio of 2 or 4 (Table 4). P

can be set by the parallel interface pin P or through the

serial I2C interface. M is determined by the inputs at the

10-pin M[9:0] through parallel interface or by program-

ming through the serial I2C interface (Table 5). NA

determines the postdivider for differential output QA

and QB, and has a valid division value of 2, 4, 8, 16,

32, or 64 based on the 3-pin inputs NA[2:0] (Table 6).

NA can also be set through the serial I2C interface. NB

is the postdivider for output QB and has a valid value of

1 or 2 (Table 7). NB can be set by the parallel interface

pin NB or through the serial I2C interface.

Table 4. Pre-PLL Divider P

P VALUE

0 fREF / 2

1 fREF / 4

DEFAULT VALUE

—

1

Table 5. PLL Feedback Divider M

M[9:0] M9 M8 M7 M6 M5 M4 M3 M2 M1 M0 DEFAULT VALUE

136 0 0 1 0 0 0 1 0 0 0

—

137 0 0 1 0 0 0 1 0 0 1

—

... —

500 0 1 1 1 1 1 0 1 0 0

01 1111 0100

... —

512 1 0 0 0 0 0 0 0 0 0

—

... —

724 1 0 1 1 0 1 0 1 0 0

—

725 1 0 1 1 0 1 0 1 0 1

—

______________________________________________________________________________________ 11

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet MAX3674.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX3670 | Low-Jitter 155MHz/622MHz Clock Generator | Maxim Integrated |

| MAX3670EGJ | Low-Jitter 155MHz/622MHz Clock Generator | Maxim Integrated |

| MAX3671 | Low-Jitter Frequency Synthesizer | Maxim Integrated Products |

| MAX3672 | Low-Jitter 155MHz/622MHz Clock Generator | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |