|

|

PDF JS28F256P30T95 Data sheet ( Hoja de datos )

| Número de pieza | JS28F256P30T95 | |

| Descripción | Embedded Memory | |

| Fabricantes | Numonyx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de JS28F256P30T95 (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

Numonyx™ StrataFlash® Embedded Memory

(P30)www.DataSheet4U.com

Product Features

Datasheet

High performance

Security

— 85 ns initial access

— One-Time Programmable Registers:

— 52 MHz with zero wait states, 17ns clock-to-data output

• 64 unique factory device identifier bits

synchronous-burst read mode

• 2112 user-programmable OTP bits

— 25 ns asynchronous-page read mode

— Selectable OTP Space in Main Array:

— 4-, 8-, 16-, and continuous-word burst mode

— Buffered Enhanced Factory Programming (BEFP) at 5 μs/

byte (Typ)

— 1.8 V buffered programming at 7 μs/byte (Typ)

• Four pre-defined 128-KByte blocks (top or bottom

configuration)

• Up to Full Array OTP Lockout

— Absolute write protection: VPP = VSS

Architecture

— Multi-Level Cell Technology: Highest Density at Lowest

Cost

— Power-transition erase/program lockout

— Individual zero-latency block locking

— Individual block lock-down

— Asymmetrically-blocked architecture

Software

— Four 32-KByte parameter blocks: top or bottom

— 20 μs (Typ) program suspend

configuration

— 20 μs (Typ) erase suspend

— 128-KByte main blocks

— Numonyx™ Flash Data Integrator optimized

Voltage and Power

— VCC (core) voltage: 1.7 V – 2.0 V

— VCCQ (I/O) voltage: 1.7 V – 3.6 V

— Standby current: 20μA (Typ) for 64-Mbit

— Basic Command Set and Extended Command Set

compatible

— Common Flash Interface capable

Density and Packaging

— 4-Word synchronous read current:

13 mA (Typ) at 40 MHz

— 56- Lead TSOP package (64, 128, 256,

512- Mbit)

Quality and Reliability

— Operating temperature: –40 °C to +85 °C

— Minimum 100,000 erase cycles per block

— ETOX™ VIII process technology

— 64- Ball Numonyx™ Easy BGA package (64,

128, 256, 512- Mbit)

— Numonyx™ QUAD+ SCSP (64, 128, 256,

512- Mbit)

— 16-bit wide data bus

Order Number: 306666-11

November 2007

1 page

P30

Revision History

Revision Date

April 2005

August 2005

www.DataSheet4U.com

September 2005

November 2005

February 2006

April 2006

May 2006

May-2006

June - 2007

November 2007

November 2007

Revision

-001

-002

-003

-004

-005

-006

-007

-008

-009

-010

11

Description

Initial Release

Revised discrete memory maps in Section 4.4, “Memory Maps” on page 22

Added memory maps for 512-Mbit top parameter devices in Section 4.4, “Memory

Maps” on page 22

Fixed size of Programming Region for 256-Mbit to be 8-Mbit in Section 4.4, “Memory

Maps” on page 22 and Section 11.0, “Programming Operations” on page 56

Removed power supply sequencing requirement in Section 8.1, “Power-Up and Power-

Down” on page 41

Updated conditions for Table 15, “Capacitance” on page 29

Updated CFI table in Appendix C, “Common Flash Interface”

Added note to Table 34, “Device ID codes” on page 71 for stacked Device ID codes

Synchronous burst read operation is currently not supported for the TSOP package

Updated 512-Mbit Easy BGA Ball Height (symbol A1) in Figure 2, “Easy BGA Mechanical

Specifications” on page 11

Updated read access speed for 265M TSOP package

Removed all references to 1 Gigabit.

• Added 52 MHz capabilities,

• Added TSOP Package information for 512 Mb throughout the document,

• Added Section 2.1, “Virtual Chip Enable Description” on page 8,

• Modified figures in Section 4.3, “Dual-Die Configurations” on page 21,

• Modified Table 9, “512-Mbit Top and Bottom Parameter Memory Map (Easy BGA and

QUAD+ SCSP)” on page 23,

• Modified Notes 5 & 6 to Reset Specifications table in Section 8.2, “Reset

Specifications” on page 41,

• Added additional note on 512 Mb capability in Table 31, “Selectable OTP Block

Mapping” on page 66.

• Updated the following tables to 52 MHz: Table 16, “AC Read Specifications for 64/

128- Mbit Densities” on page 29 and Table 17, “AC Read Specifications for 256/512-Mbit

Densities” on page 30.

• Added notes 1, 2, and 3 to Table 15, “Capacitance” on page 29.

• Correct typos and add clarifications

• Enabled specific burst operation on TSOP packages.

• Updated device commands table.

• Updaed description on synchronous burst operation.

• Added EOWL description.

• Updated flowcharts

• Updated for 65nm lithography

• Added W602 - Erase to Suspend

• Applied Numonyx branding.

November 2007

Order Number: 306666-11

Datasheet

5

5 Page

P30

Table 3: TSOP Package Dimensions (Sheet 2 of 2)

Product Information

Symbol

Min

Millimeters

Nom

Max

Min

Inches

Nom

Lead Tip Length

L

0.500

0.600

0.700

0.020

0.024

Lead Count

N - 56 - - 56

Lead Tip Angle

ý 0° 3° 5° 0° 3°

Seating Plane Coplanarity

Y

- - 0.100 - -

Lead to Package Offset

Z

0.150

0.250

0.350

0.006

0.010

Notes:

www.DataSheet4U.com1.

One dimple on package denotes Pin 1.

2. If two dimples, then the larger dimple denotes Pin 1.

3. Pin 1 will always be in the upper left corner of the package, in reference to the product mark.

4. Daisy Chain Evaluation Unit information is at Numonyx™ Flash Memory Packaging Technology

http://developer.Numonyx.com/design/flash/packtech.

Max

0.028

-

5°

0.004

0.014

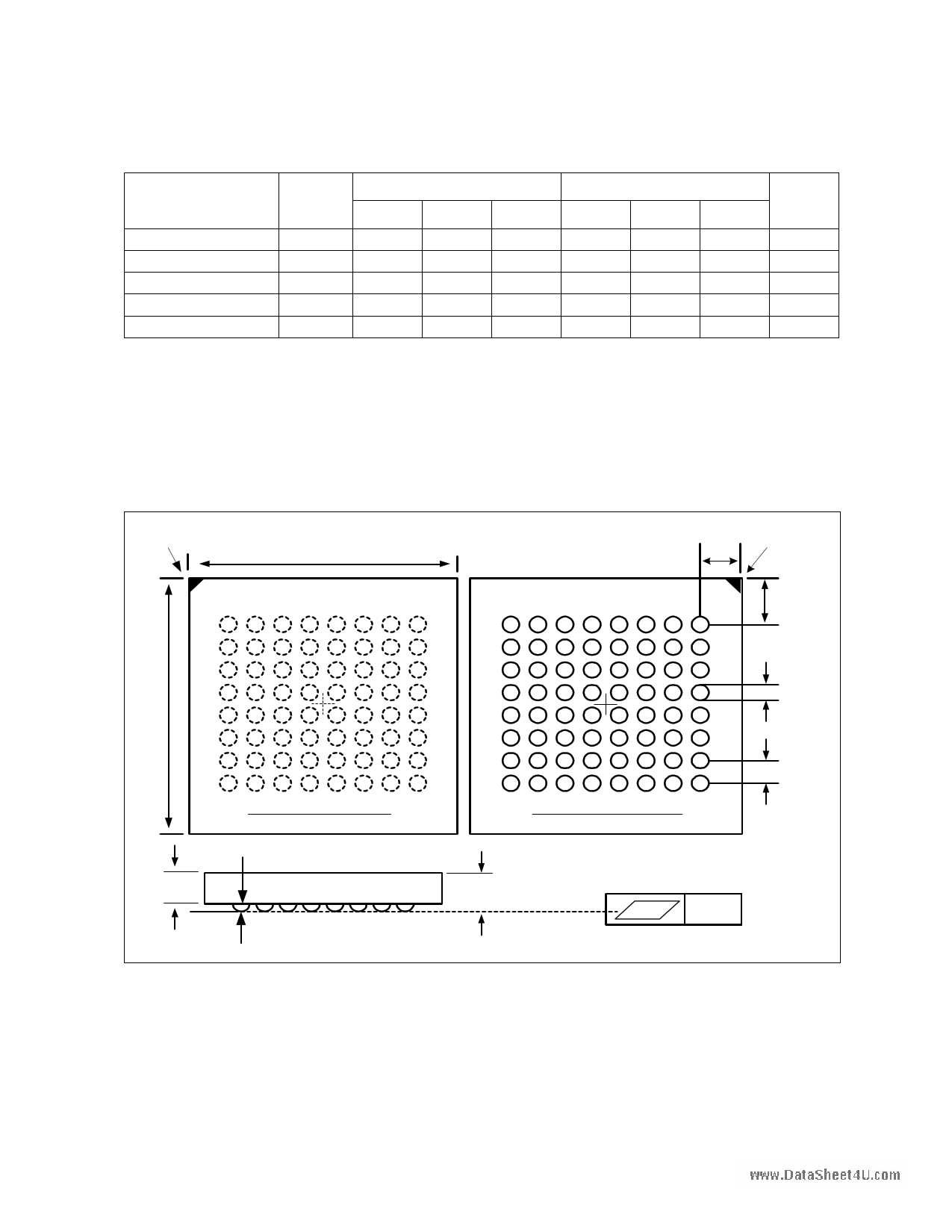

3.2 64-Ball Easy BGA Package

Notes

Figure 2: Easy BGA Mechanical Specifications

Ball A1

Corner

D

Ball A1

Corner

S1

12 3 4 5 6 7 8

A

B

C

D

E

E

F

G

H

Top View - Ball side down

8

A

B

C

D

E

F

G

H

7 6 5 4 3 21

Bottom View - Ball Side Up

S2

b

e

A1

A2

A Seating

Plane

Y

Note: Drawing not to scale

November 2007

Order Number: 306666-11

Datasheet

11

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet JS28F256P30T95.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| JS28F256P30T95 | Embedded Memory | Numonyx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |