|

|

PDF LH5P832 Data sheet ( Hoja de datos )

| Número de pieza | LH5P832 | |

| Descripción | CMOS 256K (32K x 8) Pseudo-Static RAM | |

| Fabricantes | Sharp Electrionic Components | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LH5P832 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

LH5P832

CMOS 256K (32K × 8) Pseudo-Static RAM

FEATURES

• 32,768 × 8 bit organization

• Access time: 100/120 ns (MAX.)

• Cycle time: 160/190 ns (MIN.)

• Power consumption:

Operating: 357.5/303 mW

Standby: 16.5 mW

• TTL compatible I/O

• 256 refresh cycle/4 ms

• Auto refresh is executed by internal

counter (controlled by OE/RFSH pin)

• Self refresh is executed by internal timer

• Single +5 V power supply

• Packages:

28-pin, 600-mil DIP

28-pin, 300-mil SK-DIP

28-pin, 450-mil SOP

DESCRIPTION

The LH5P832 is a 256K bit Pseudo-Static RAM or-

ganized as 32,768 × 8 bits. It is fabricated using sili-

con-gate CMOS process technology.

The LH5P832 uses convenient on-chip refresh cir-

cuitry with a DRAM memory cell for pseudo static

operation. This simplifies external clock inputs, while

providing the same simple, non-multiplexed pinout as

industry standard SRAMs. Moreover, due to the func-

tional similarities between PSRAMs and SRAMs, many

32K × 8 SRAM sockets can be filled with the LH5P832

with little or no changes. The advantage is the cost

savings realized with the lower cost PSRAM.

The LH5P832 PSRAM has the ability to fill the gap

between DRAM and SRAM by offering low cost, low

standby power, and a simple interface.

Three methods of refresh control are provided for

maximum versatility. A ‘CE-Only’ refresh cycle re-

freshes the addressed row of memory cells transpar-

ently. All 256 rows must be refreshed or accessed every

four milliseconds. ‘Auto Refresh’ automatically cycles

through a different row on every OE/RFSH clock pulse,

accomplishing the row refreshes without the need to

supply row addresses externally. ‘Self Refresh’ further

simplifies the refresh requirements by eliminating the

need for address inputs and clock pulses entirely. An

automatic timer senses time periods when memory

accesses have ceased, and provides full refresh of all

rows of memory without any external assistance.

PIN CONNECTIONS

28-PIN DIP

28-PIN SK-DIP

28-PIN SOP

TOP VIEW

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O1

I/O2

I/O3

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 VCC

27 R/W

26 A13

25 A8

24 A9

23 A11

22 OE/RFSH

21 A10

20 CE

19 I/O8

18 I/O7

17 I/O6

16 I/O5

15 I/O4

5P832-1

Figure 1. Pin Connections for DIP, SK-DIP,

and SOP Packages

1

1 page

CMOS 256K (32K × 8) Pseudo-Static RAM

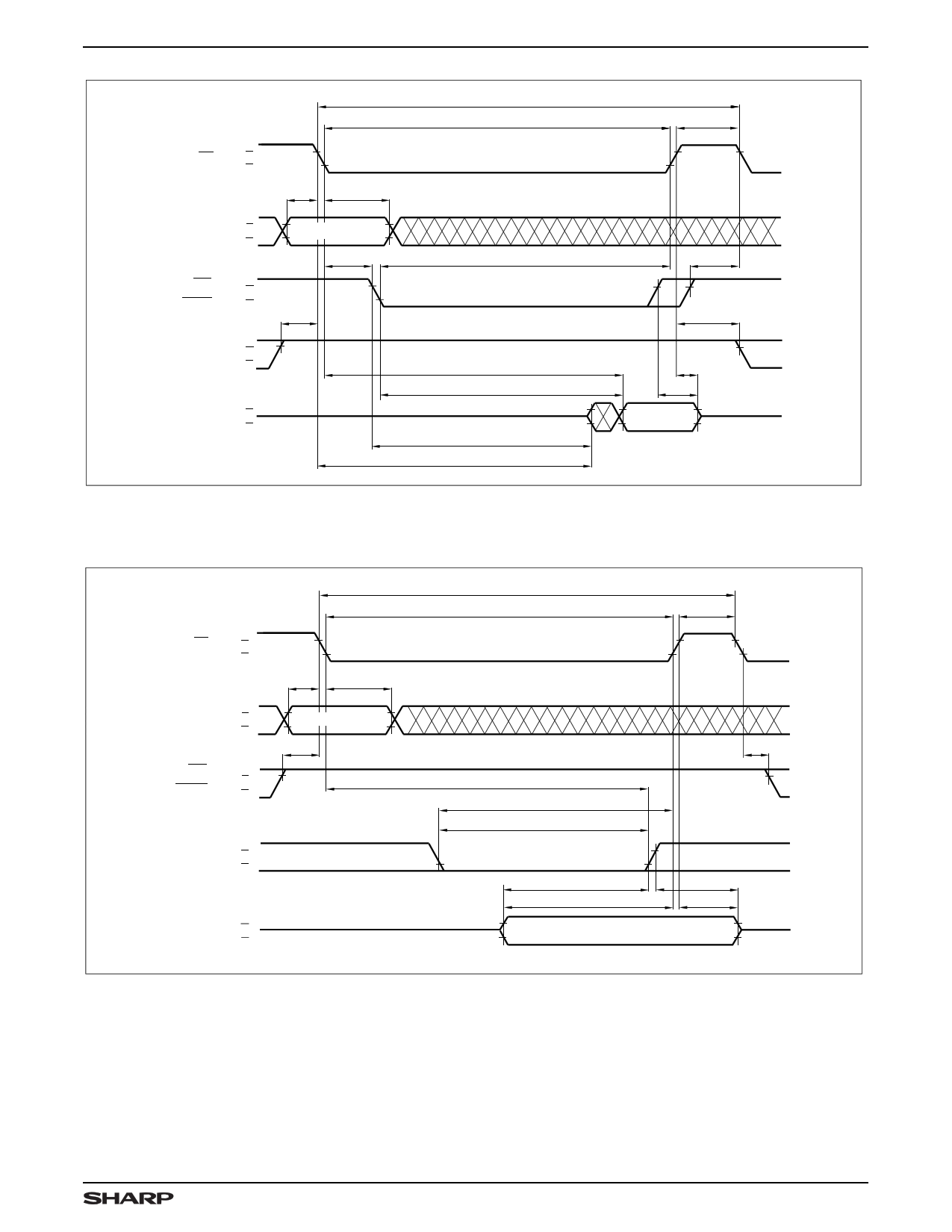

CE

VIH

VIL

A0 - A14

VIH

VIL

OE/ VIH

RFSH VIL

R/W

VIH

VIL

I/O1

-

I/O8

VOH

VOL

tRC

tCE

tAS tAH

ADDRESS

tOEH

tOEL

tRCS

tCEA

tOEA

tCLZ

tOLZ

Figure 3. Read Cycle

LH5P832

tP

tOES

tRCH

tCHZ

tOHZ

DATA

OUT

5P832-3

CE

VIH

VIL

A0 - A14

VIH

VIL

OE/ VIH

RFSH VIL

tAS tAH

ADDRESS

tOES

R/W

VIH

VIL

I/O1 - I/O8

VIH

VIL

tRC

tCE

tP

tWCH

tWCS

tWCP

tOEH

tDSW

tDSC

DATA - IN

tDHW

tDHC

Figure 4. Write Cycle

5P832-4

5

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet LH5P832.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LH5P832 | CMOS 256K (32K x 8) Pseudo-Static RAM | Sharp Electrionic Components |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |