|

|

PDF HY5PS56421F Data sheet ( Hoja de datos )

| Número de pieza | HY5PS56421F | |

| Descripción | 256Mb DDR2 SDRAM | |

| Fabricantes | Hynix | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HY5PS56421F (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

HY5PS56421(L)F

HY5PS56821(L)F

HY5PS561621(L)F

www.DataSheet4U.com

256Mb DDR2 SDRAM

HY5PS56421(L)F

HY5PS56821(L)F

HY5PS561621(L)F

This document is a general product description and is subject to change without notice. Hynix Electronics does not assume

any responsibility for use of circuits described. No patent licenses are implied.

Rev 1.0/ July. 2004

1

1 page

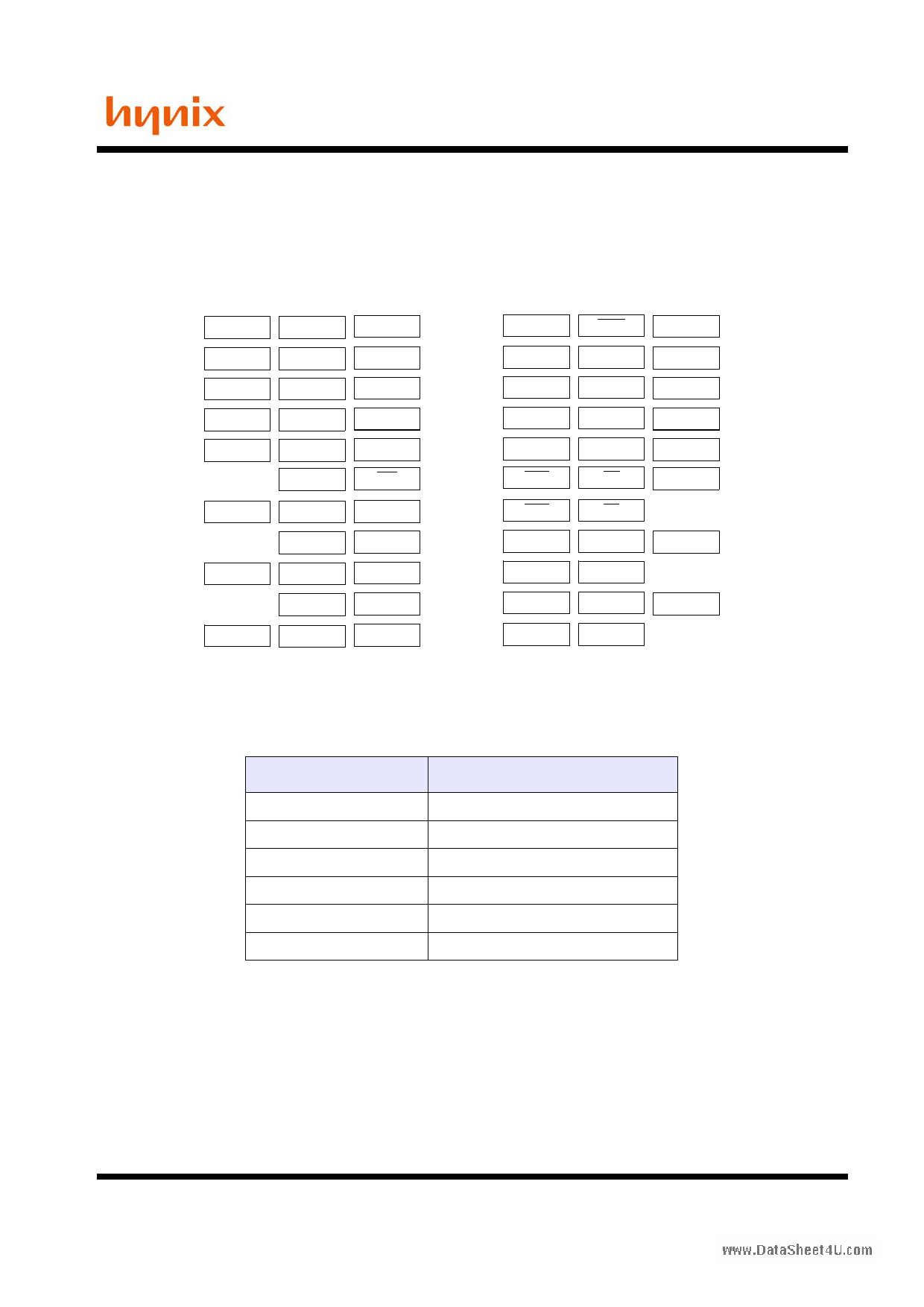

1.2 Pin Configuration & Address Table

64Mx4 DDR2 Pin Configuration

HY5PS56421(L)F

HY5PS56821(L)F

HY5PS561621(L)F

www.DataSheet4U.com

123

789

VDD NC VSS

A VSSQ DQS VDDQ

NC VSSQ DM

B

DQS VSSQ

NC

VDDQ DQ1 VDDQ C VDDQ DQ0 VDDQ

NC

VSSQ

DQ3

D

DQ2 VSSQ

NC

VDDL

VREF

CKE

VSS

WE

E

VSSDL

CK

VDD

F RAS CK ODT

NC BA0 BA1 G CAS CS

A10 A1 H A2 A0 VDD

VSS A3

A5

J

A6 A4

A7 A9

K A11 A8 VSS

VDD

A12

NC

L

NC A13

ROW AND COLUMN ADDRESS TABLE

ITEMS

# of Bank

Bank Address

Auto Precharge Flag

Row Address

Column Address

Page size

64Mx4

4

BA0, BA1

A10/AP

A0 - A12

A0-A9, A11

1 KB

Rev 1.0 / July. 2004

5

5 Page

3. AC & DC Operating Conditons

HY5PS56421(L)F

HY5PS56821(L)F

HY5PS561621(L)F

3.1 DC Operating Conditions

3.1.1 Recommended DC Operating Conditions (SSTL_1.8)

Symbol

Parameter

VDD

www.DataSheet4U.comVDDL

VDDQ

VREF

VTT

Supply Voltage

Supply Voltage for DLL

Supply Voltage for Output

Input Reference Voltage

Termination Voltage

Min.

1.7

1.7

1.7

0.49*VDDQ

VREF-0.04

Rating

Typ.

1.8

1.8

1.8

0.50*VDDQ

VREF

Max.

1.9

1.9

1.9

0.51*VDDQ

VREF+0.04

Units

V

V

V

mV

V

Notes

4

4

1, 2

3

There is no specific device VDD supply voltage requirement for SSTL-1.8 compliance. However under all conditions VDDQ must

be less than or equal to VDD.

1. The value of VREF may be selected by the user to provide optimum noise margin in the system. Typically the value of VREF is

expected to be about 0.5 x VDDQ of the transmitting device and VREF is expected to track variations in VDDQ.

2. Peak to peak ac noise on VREF may not exceed +/-2% VREF (dc).

3. VTT of transmitting device must track VREF of receiving device.

4. VDDQ tracks with VDD, VDDL tracks with VDD. AC parameters are measured with VDD, VDDQ and VDDDL tied together

3.1.2 ODT DC electrical characteristics

PARAMETER/CONDITION

Rtt effective impedance value for EMRS(A6,A2)=0,1; 75 ohm

Rtt effective impedance value for EMRS(A6,A2)=1,0; 150 ohm

Rtt effective impedance value for EMRS(A6,A2)=1,1; 550 ohm

Deviation of VM with respect to VDDQ/2

SYMBOL MIN NOM MAX UNITS NOTES

Rtt1(eff) 60 75 90 ohm 1

Rtt2(eff) 120 150 180 ohm 1

Rtt2(eff) 40 50 60 ohm 1,2

delta VM -6

+6 % 1

Note 1: Test condition for Rtt measurements

Note 2: Optional for DDR2-400/533/667

Measurement Definition for Rtt(eff): Apply VIH (ac) and VIL (ac) to test pin separately, then measure current I(VIH

(ac)) and I( VIL (ac)) respectively. VIH (ac), VIL (ac), and VDDQ values defined in SSTL_18

VIH (ac) - VIL (ac)

Rtt(eff) =

I(VIH (ac)) - I(VIL (ac))

Measurement Definition for VM : Measurement Voltage at test pin(mid point) with no load.

delta VM =

2 x Vm

- 1 x 100%

VDDQ

Rev 1.0/July. 2004

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HY5PS56421F.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HY5PS56421F | 256Mb DDR2 SDRAM | Hynix |

| HY5PS56421LF | 256Mb DDR2 SDRAM | Hynix |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |