|

|

PDF TC190 Data sheet ( Hoja de datos )

| Número de pieza | TC190 | |

| Descripción | System ASIC | |

| Fabricantes | Toshiba | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TC190 (archivo pdf) en la parte inferior de esta página. Total 5 Páginas | ||

|

No Preview Available !

TOSHIBA

System ASIC

TC190 Series CMOS ASICs

0.6µ 3.0/3.3V ASIC Family

The 0.6µm, 5V TC190 ASIC series provides higher system per-

formance and device integration with lower power than previous

generation 5V families. Highly accurate delay models, area effi-

cient memory cells and a very fine pitch TAB bonding capability

for high I/O requirements are some of the features of the family

which consists of Gate Array (TC190G), Embedded Array

(TC190E) and Standard Cell (TC190C) ASIC products. The

www.DataShTeCet14U90.cEomis a gate array based product that incorporates the ability

to embed large diffused cell based hardmacrocells and com-

pilable cells (RAM, ROM, DAC, multipliers, PLLs, etc) rather

than building metalized functions. This enables denser, faster,

higher performance ASICS to be designed while still exhibiting

quick “gate array” type turn around times.

Benefits

– Advanced 0.6µ micron CMOS process with fast 240 gate

delays.

– Reduction of gate power by as much as 20 percent over 0.8µm

ASICs.

– 707,000 usable gates provide high levels of integration for

improved performance and board area savings.

– Extensive libraries with a wide range of macrocells,

compilable cells and megacells availible.

– Library compatible with existing TC160G/170G gate arrays for

ease of design migration to 0.6µm technology

– Design Kit support for a wide range of EDA environments.

– VERILOG-XL sign off capability.

– 62µ TAB pad pitch allows higher number of I/O per gate than

previous product generations.

– A wide range of packages are availible, including heat spreader

plastic QFP, TABFP, BGA, tape BGA and others.

– New accurate delay modeling

– Verilog sign-off

System Performance

The high density, high performance TC190 series ASIC family is

manufactured using Toshiba’s 0.6µm double and triple layer

complimentary metal-oxide silicon process. This family provides

sub-micron ASIC density for pure 5V applications, and applica-

tions that are developed to transition over time to 3V. Typical

applications are PC chipsets, graphics, telecommunications, net-

works, set top boxes and systems designed to migrate from 5V to

3V.

The 707K usable gates allow previously unobtainable levels

of integration to be achieved on a 5V ASIC. The TC190 series

supports many complex functions such as multipliers, DACs,

ADCs,RAM, ROM and FIFOs.

The TC190 series offers Toshiba’s high quality and high

capacity manufacturing expertise. A partnership with Toshiba

brings you not only the high quality and reliability ASICs, but

fast prototype turnaround (3 day for gate array), steep production

ramp-up and proven high volume manufacturing capacity.

Packaging

The TC190 series wide range of packaging options provide a

packaging solution for any requirement. New packages are con-

tinuously being developed. Contact your Toshiba sales represen-

tative for the Toshiba Packaging Book for specific package/pin

count information.

Features

TC190G

TC190E/C

– 22K – 707K usable gates

up to 730K

– 14 standard master sizes

21 standard master sizes

– up to 512 wire bonds

Same

– up to 776 TAB bond pads

– 62µ Inner lead bond pads

Same

– Typical core power – 2.63µW/gate/Mhz

– 180+ primitive cells

(scan, standard, high drive cells)

Same

– 450+ I/O cells including (hign drive

{24mA} slew rate control high

speed output buffers)

Compiled cells – sync/async

single, dual, triple port RAM, ROM

Same

Same

– Hard macrocells including those for PCI

bus interface are availible. Some fast

multipliers, adders, ALUs, UARTS timers

and special I/O cells are in development.

– Ability to embed large Compilable, fully

diffused memory blocks provide higher

performance and increased desnsity.

Same

TC190G Two Input NAND Gate Delay Performance

ND2 Gate Delay1

Typical2

Worst Case3

Fanout = 2

240ps

406ps

Fanout = 4

336ps

568ps

Fanout = 6

432ps

731ps

Power Dissipation

at 5V

Power = 2.63µW/gate/MHz

NOTE 1: These typical numbers are for estimation purposes only. Power dissap-

ation is dependent on wire loading and gate switching rates.

Product Brief

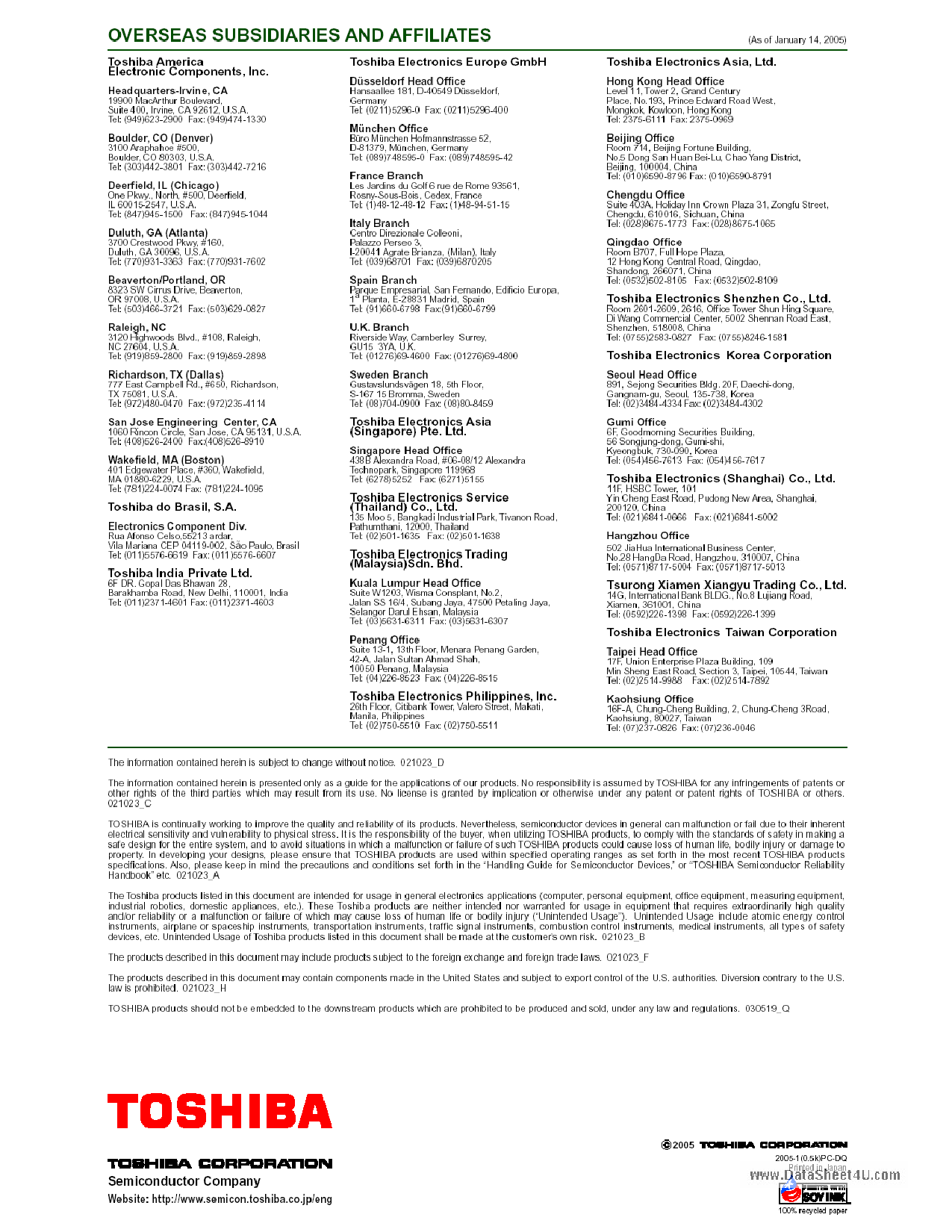

TOSHIBA Corporation

1

1 page

www.DataSheet4U.com

5 Page | ||

| Páginas | Total 5 Páginas | |

| PDF Descargar | [ Datasheet TC190.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TC190 | System ASIC | Toshiba |

| TC19Gxxx | (TC15G0xx / TC17Gxxx / TC19Gxxx) CMOS Gate Array | Toshiba |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |